Method for processing floating-point FFT by FPGA

A floating-point and floating-point number technology, which is applied in the field of signal processing technology, can solve the problems of many clock cycles, limited processing time, limited parallel processing capability and limited number of pipeline stages, and achieves the effect of improving computing efficiency and processing accuracy.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

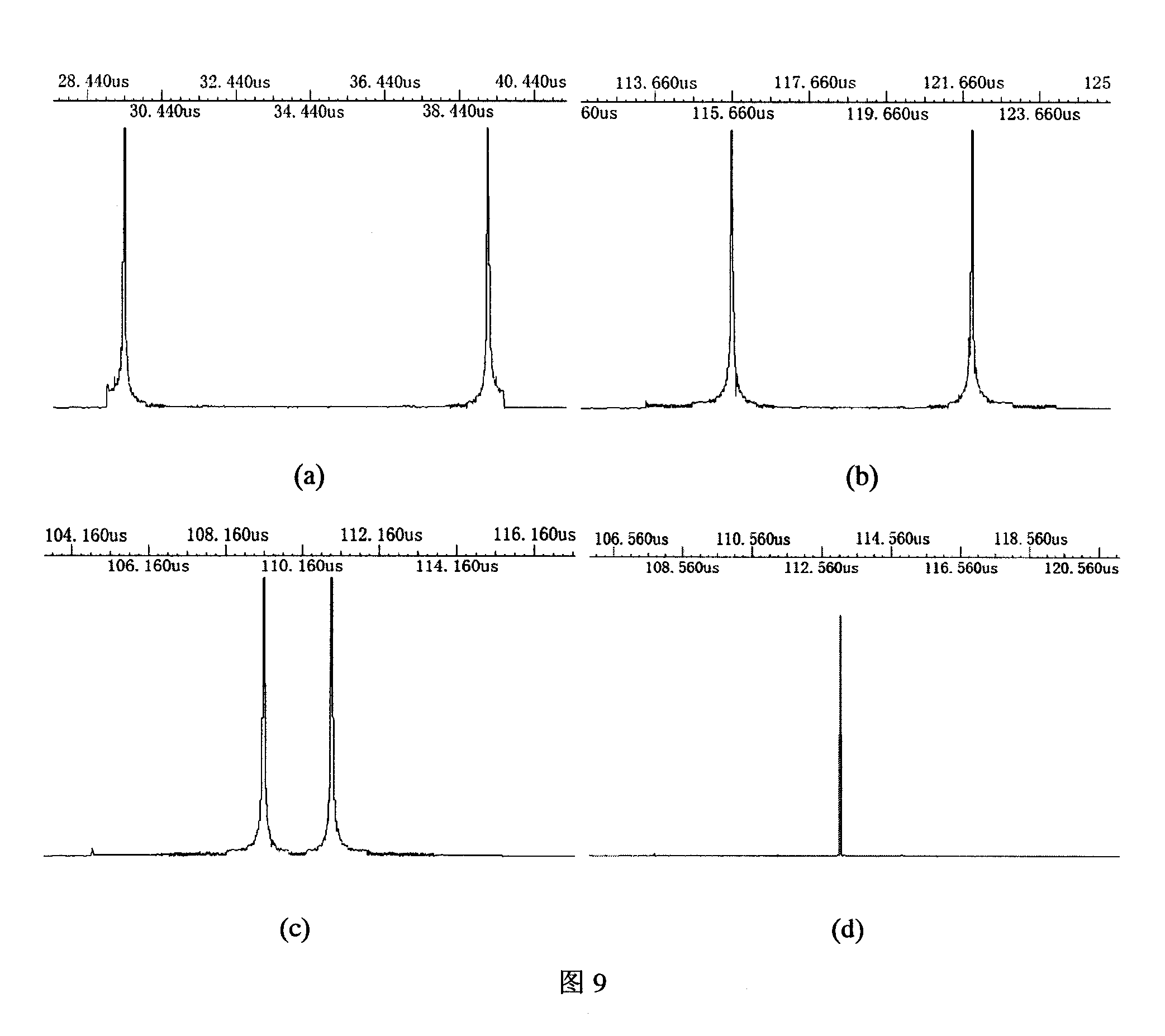

[0031] With reference to Fig. 1, it is the realization flowchart of floating-point FFT processing of the present invention, introduces floating-point FFT processing operation process in the present invention in detail below:

[0032] (1) After the floating-point FFT processor receives the running FFT processing signal, it judges whether the input data is a fixed-point number or a floating-point number according to the externally input floating-point and fixed-point selection signals. If it is a fixed-point number, the input data is first fixed-point Convert to floating point processing.

[0033] (2) Store the above-mentioned processed input data in the intermediate data memory 1 in sequence.

[0034] (3), starting from the all-zero address, take out two data in the intermediate data memory 1 each time, and the addresses of the two data require only the difference in the highest bit, such as the two addresses of the first data fetch are "00000000" and " 10000000", and at the s...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More