Flash memory address translation layer system

A flash memory address conversion and address conversion technology, which is applied in the direction of memory systems, memory address/allocation/relocation, instruments, etc., can solve the problems of flash memory reading efficiency and speed impact, lack of efficiency, adverse effects of data reading and writing speed, etc., to achieve Reduce the number of times and occupied capacity, improve efficiency, reduce the effect of capacity and times

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

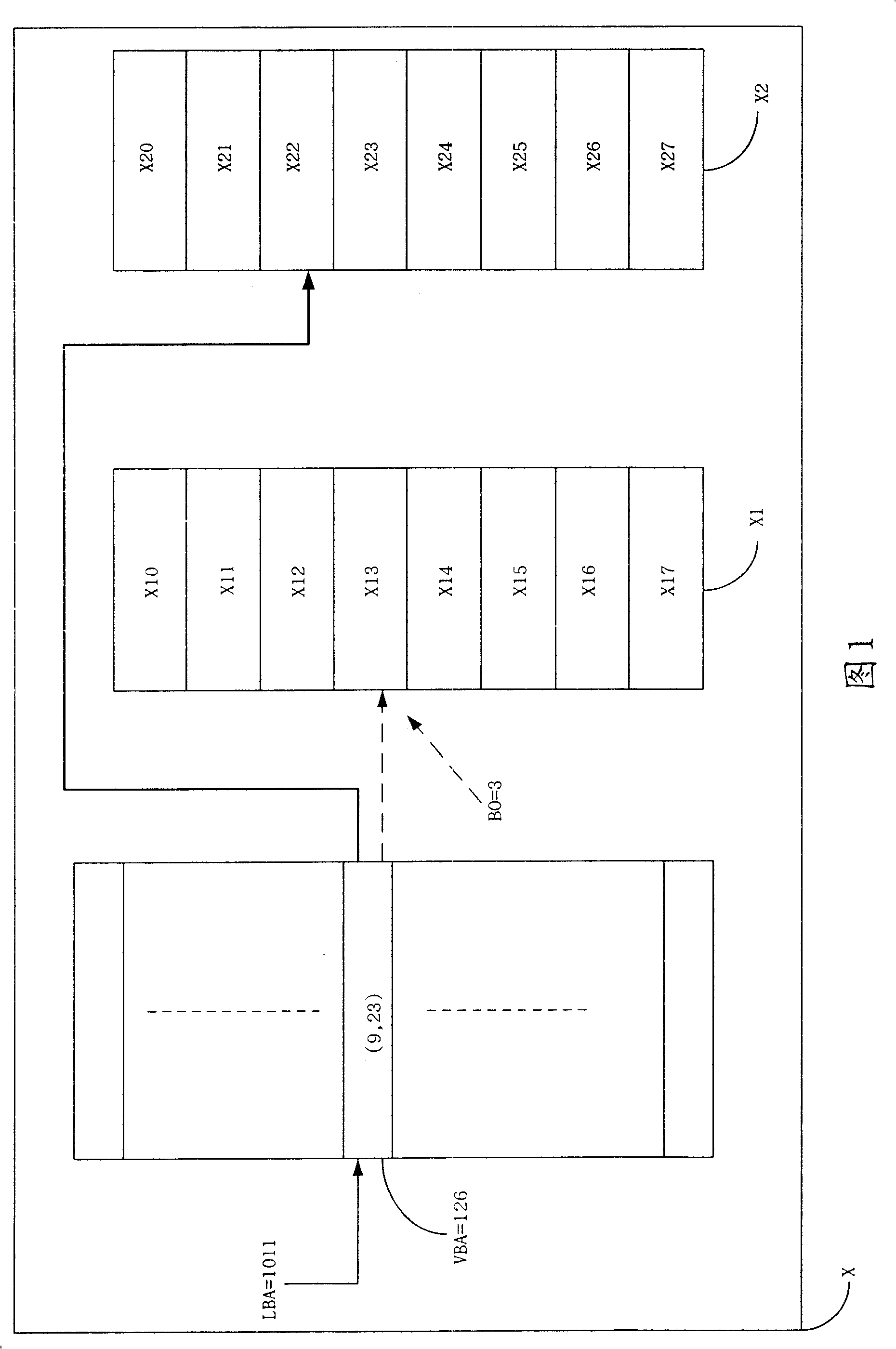

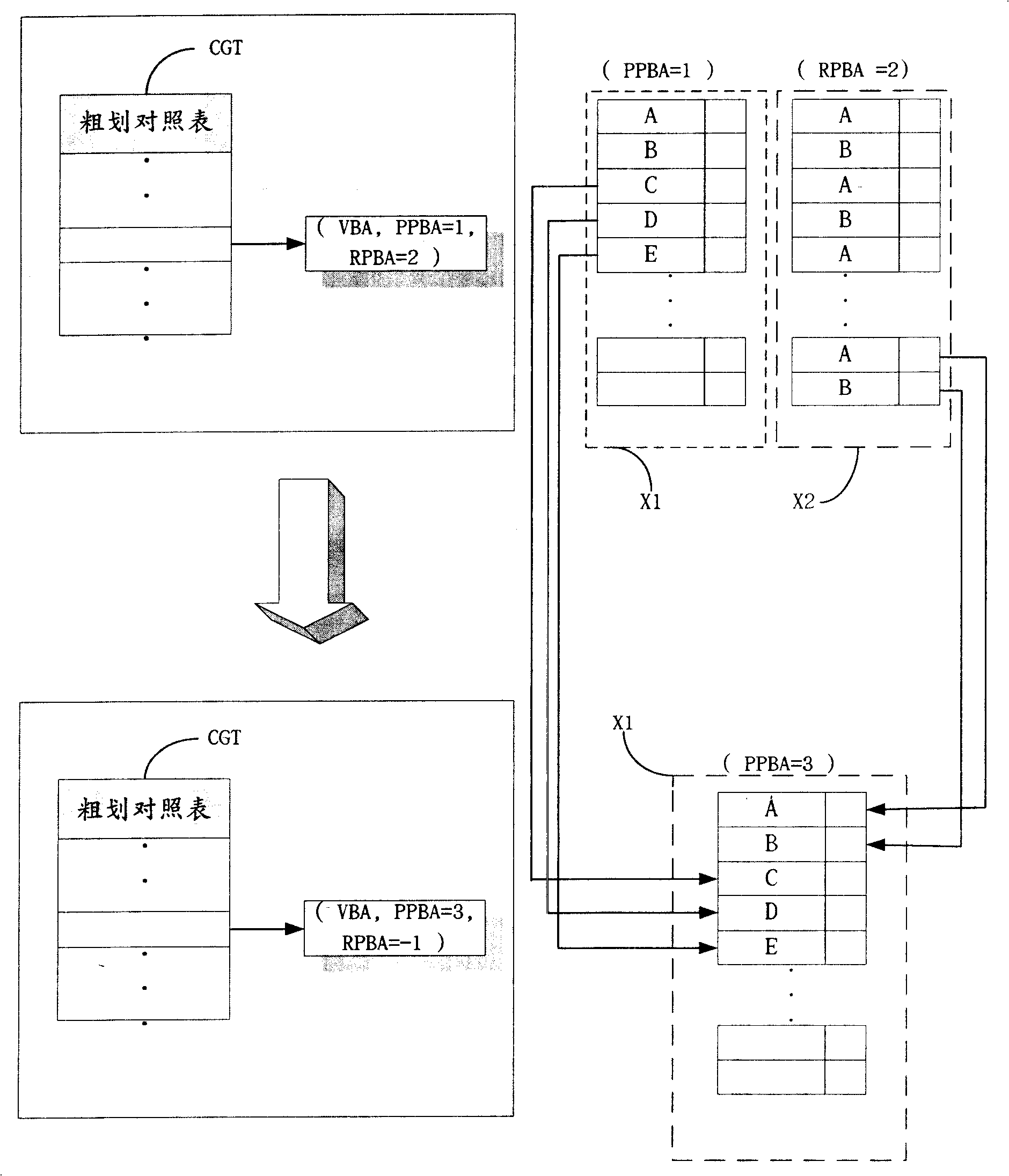

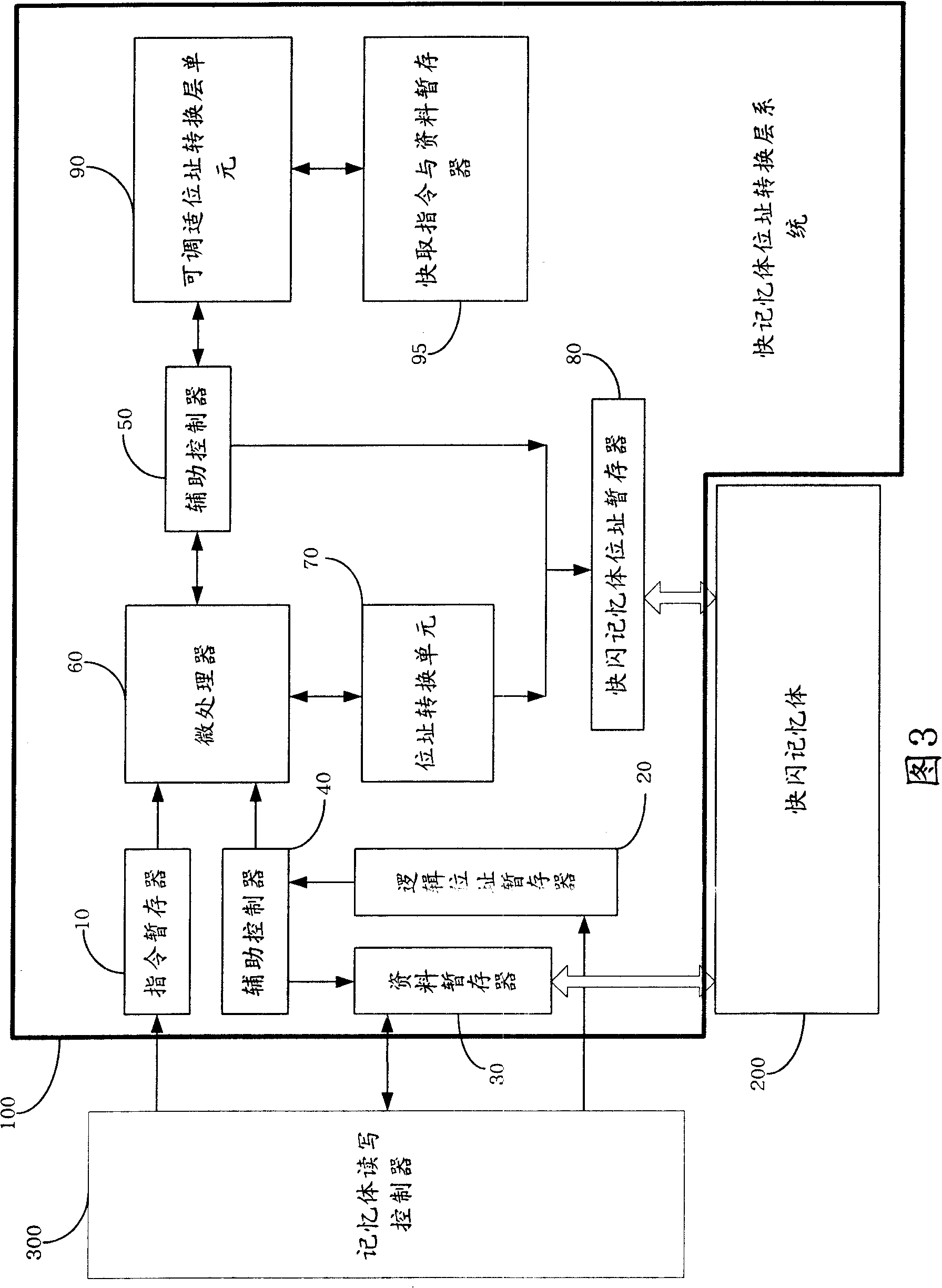

[0051] Please refer to Fig. 3 first, the flash memory changing layer system 100100 of the present invention is to connect between a flash memory 200 and a memory read-write controller 300, and the memory read-write controller 300 is an existing flash memory card reader or a personal computer. card interface, wherein, the cache device 100 includes an instruction cache 10, a logical address cache 20, a data cache 30, a pair of auxiliary controllers 40 and 50, a microprocessor 60, an address translation unit 70, and a flash memory address cache device 80, an adjustable address translation layer unit 90, and a cache instruction and data buffer 95. The instruction register 10 is connected to the memory read / write controller 300 to receive the flash memory 200 data read / write sent by the memory read / write controller 300. command and store it temporarily.

[0052] The above-mentioned logical address register 20 is connected to the memory read / write controller 300 to receive and tempo...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com