Master device of two-wire bus providing release function for clock line and method thereof

A computer system and clock line technology, applied in the field of main control components to achieve high reliability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

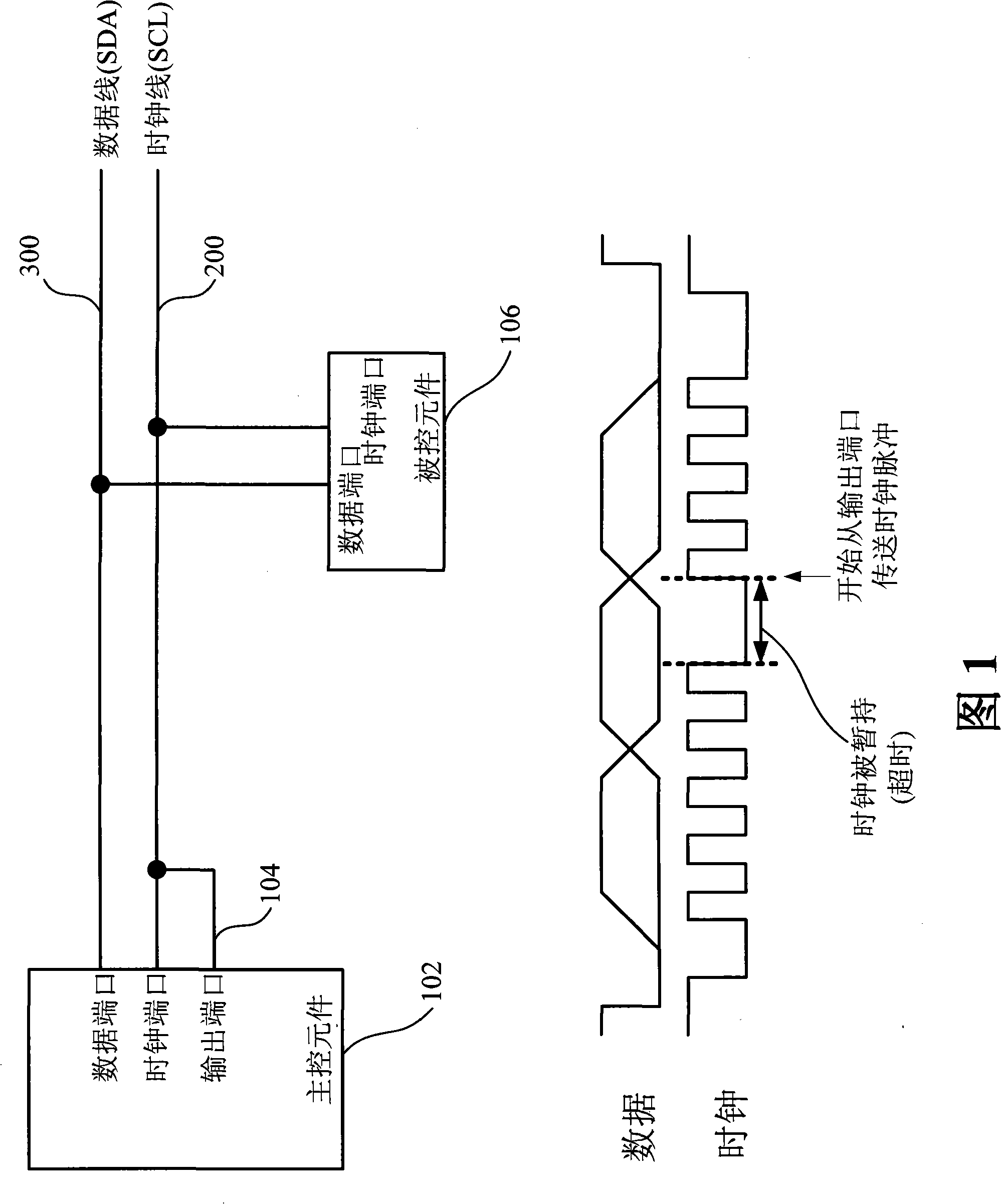

[0019] Please refer to FIG. 1, which is a simplified block diagram of a two-wire bus according to the first embodiment of the present invention, and a pulse diagram of its data line 300 and clock line 200, wherein the master control element 102 of the two-wire bus has a clock line 200 release function. In the first embodiment, the controlled device 106 is coupled to the master device 102 through a two-wire bus. The main control element 102 includes a data port, a clock port and an output port. Generally, the output port can be implemented as a general purpose input output (GPIO) port. The data port transmits data to the controlled device 106 and receives data from the controlled device 106 through the data line 300 . The clock port transmits the clock generated by the master device 102 to the controlled device 106 through the clock line 200 . The output port shown in FIG. 1 is coupled to the clock line 200 by a connection line 104 .

[0020] Taking the inter-integrated cir...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More