Method and device for decreasing offset voltage of Hall integrated circuit

An offset voltage, integrated circuit technology, applied in circuits, electrical components, electro-solid devices, etc., can solve problems such as unpredictable and control offset voltage, and achieve good consistency, small Hall output voltage offset, and good matching. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

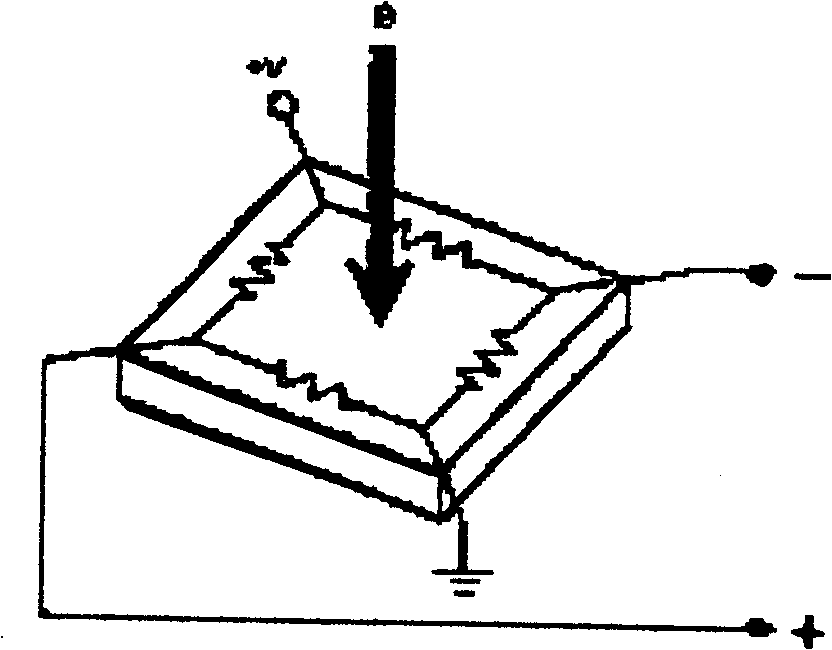

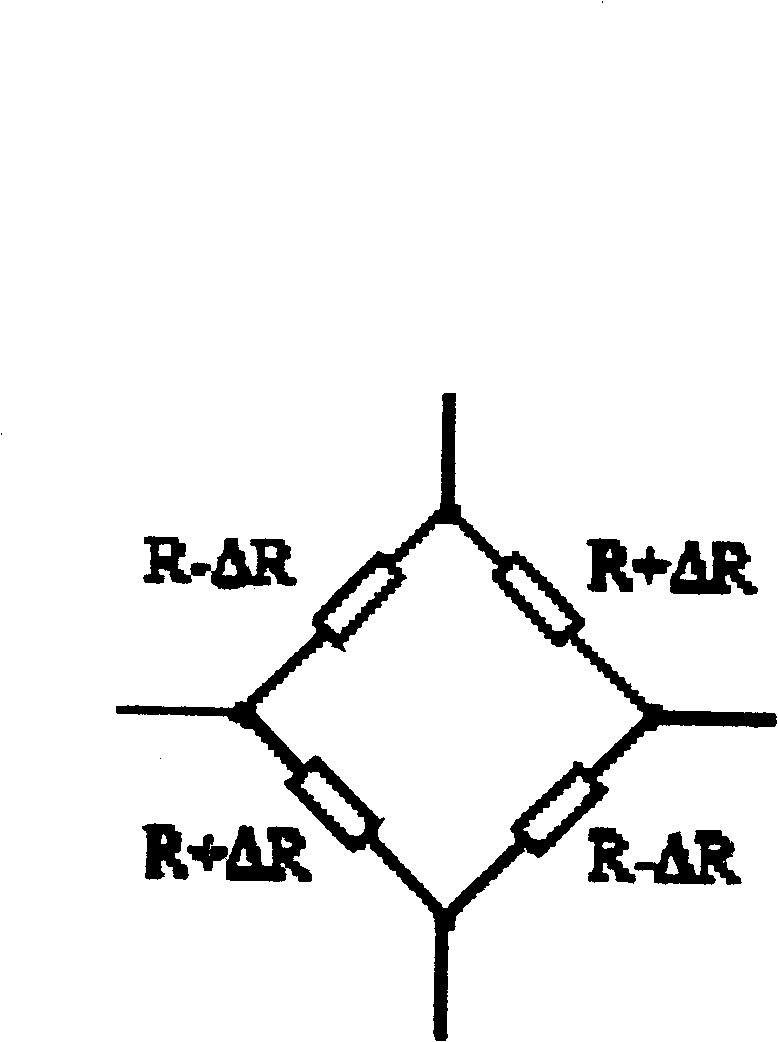

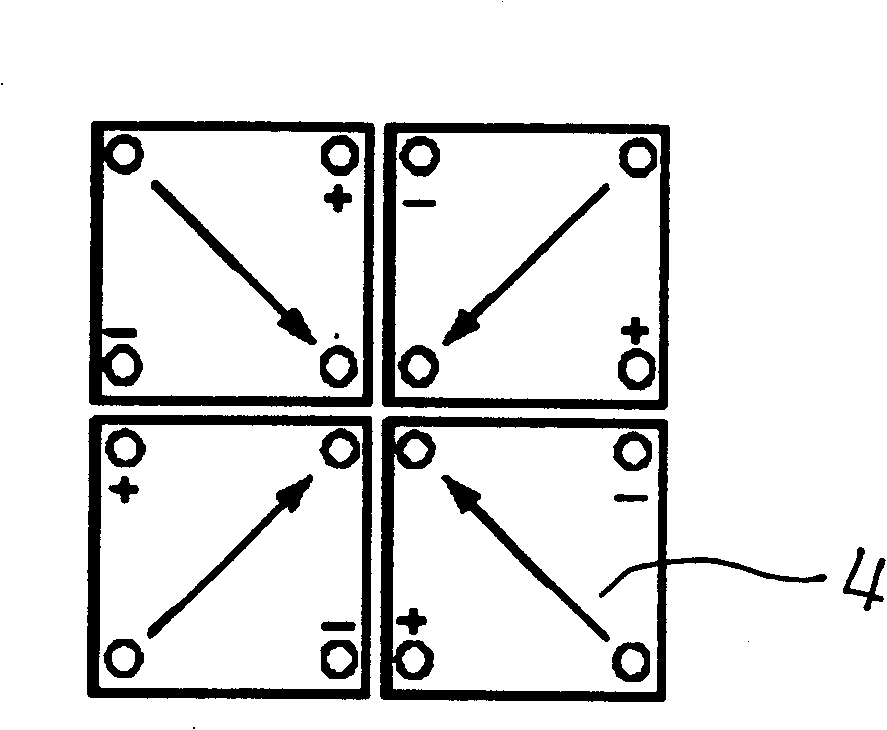

[0033] Image 6 gives Figure 5 A cross-sectional view along the A-A direction. The same number in the figure represents the same area. A lightly doped N-type epitaxial layer 2 is grown on a semiconductor P-type base substrate 1 , and the epitaxial layer 2 is separated by heavily doped P-type isolation bands 3 into isolated epitaxial islands, that is, Hall cells 4 . Four Hall cells 4 that are exactly the same and connected in parallel form a Hall sensor and are located in the middle of the chip ( Figure 5 ).

no. 2 example

[0035] Figure 8 The layout design method and connection method of the Hall unit 4 in the second embodiment are given. Compared with the first embodiment, the Hall unit 4 is set at an angle of 45 degrees, and the wider epitaxial layer is not drawn in the figure 2 and the barrier 3.

no. 3 example

[0037] Figure 9 The layout design method and connection method of the Hall unit 4 in the third embodiment are given. Compared with the second embodiment, it consists of only three Hall units 4, and the Hall units 4 are symmetrically arranged in a parallelogram center. , the wider epitaxial layer 2 and the isolation zone 3 are not shown in the figure.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More