Elastic buffering mechanism and method for compensating clock diversity

An elastic buffer and clock technology, which is applied in the field of compensating clock differences, can solve the problem of large PCI Express design area, and achieve the effect of saving design area and reducing area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

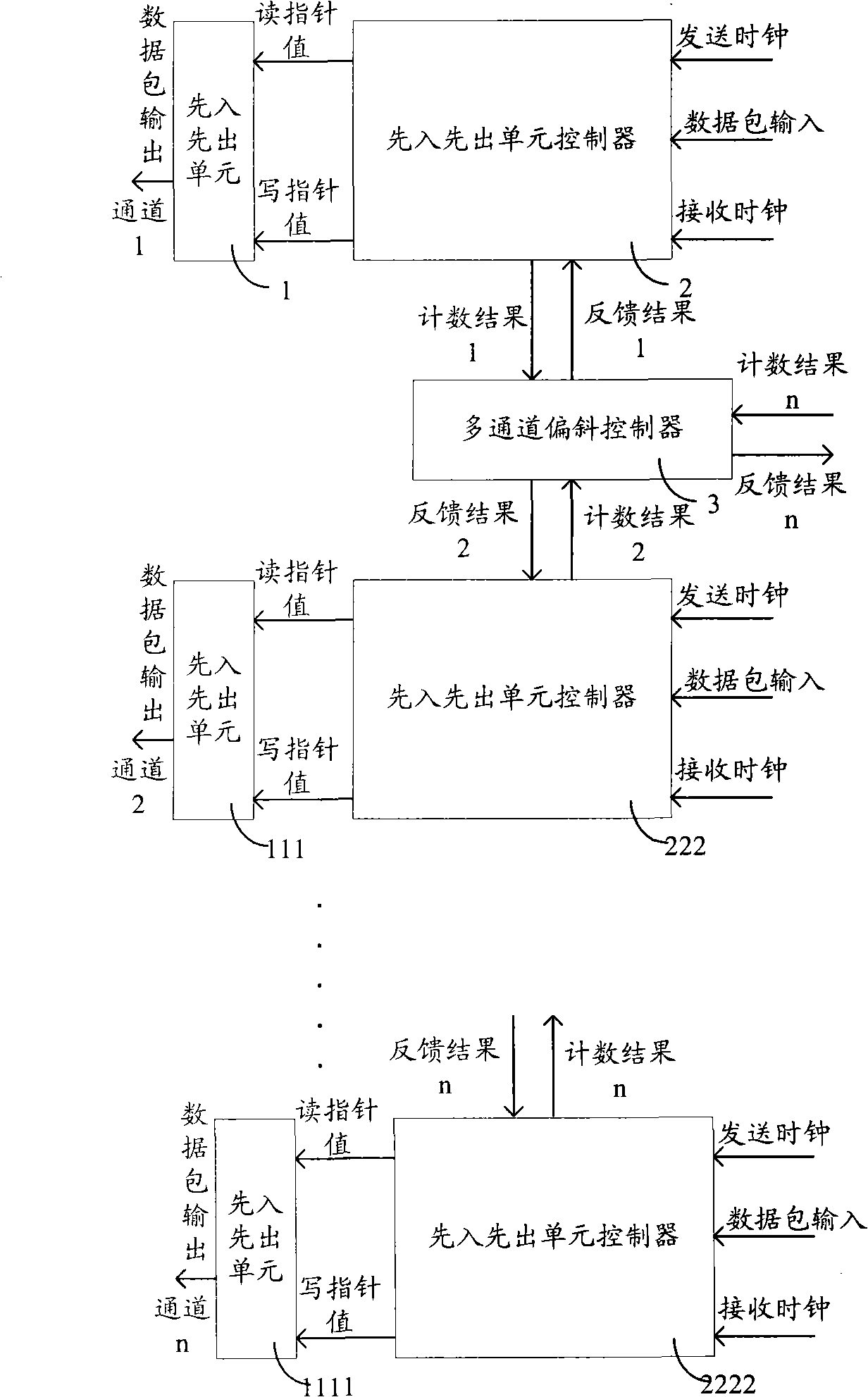

[0033] The elastic buffer device of the present invention adjusts the distance of the read-write pointer according to the detected position of the read-write pointer to compensate for the clock difference, thereby reducing the area of the required buffer unit. And the elastic buffer device of the present invention eliminates deflection by adjusting the position of the reading pointer.

[0034] The elastic cushioning device of the present invention is as image 3 shown, including,

[0035] First-in-first-out unit 1, first-in-first-out unit 111 to first-in first-out unit 1111, used for writing and reading data packet data corresponding to the data channel;

[0036]First-in-first-out unit controller 2, first-in-first-out unit controller 222 to first-in-first-out unit controller 2222, are used to control the write pointer to write data to the first-in-first-out unit of the corresponding data channel under the recovery clock, and control the read pointer at Read data from the f...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More