Method for testing FPGA device

A device and testing machine technology, applied in the direction of digital circuit testing, electronic circuit testing, instruments, etc., to achieve the effect of realizing industrialized testing, reducing operation links and improving testing efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

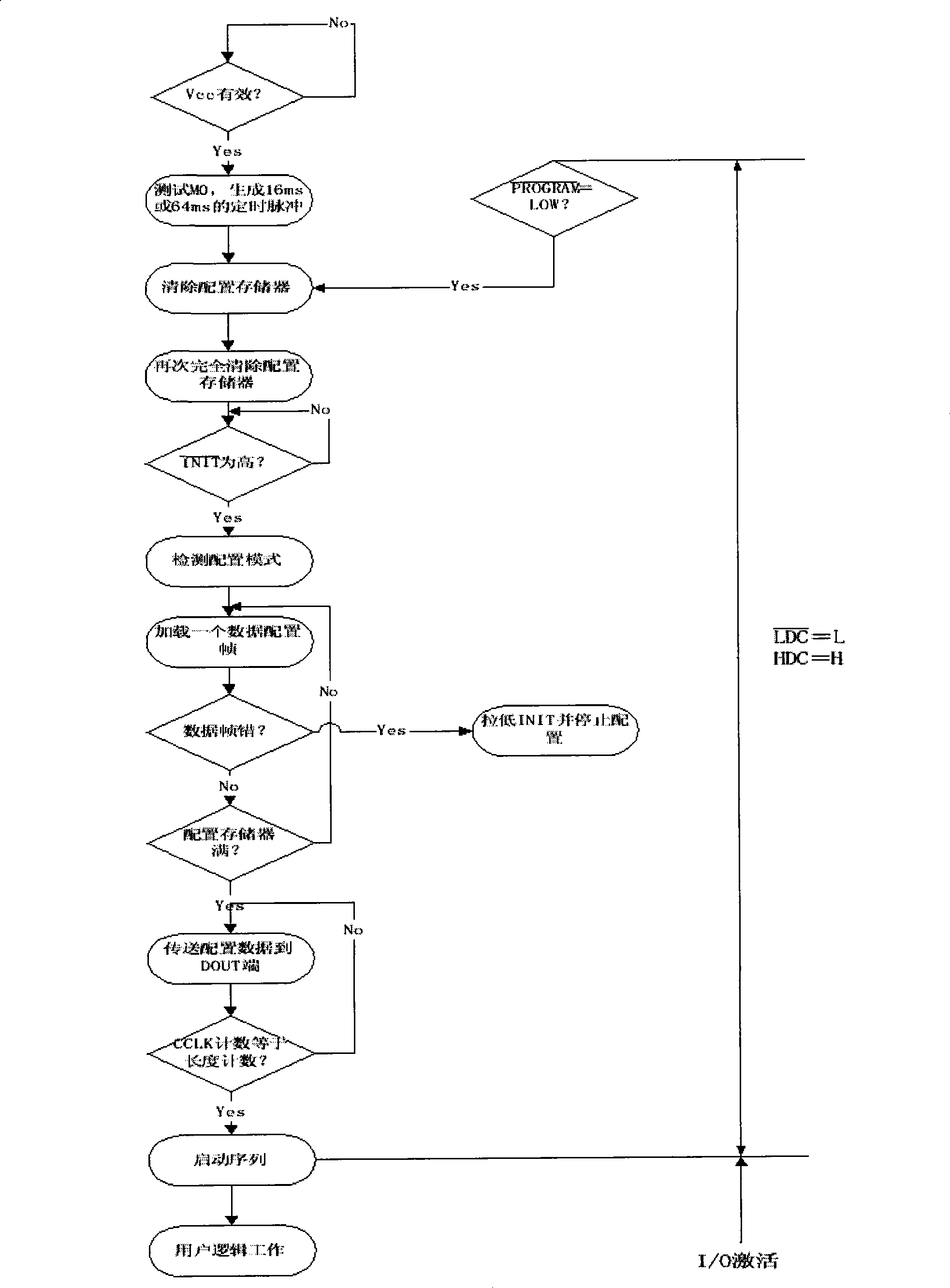

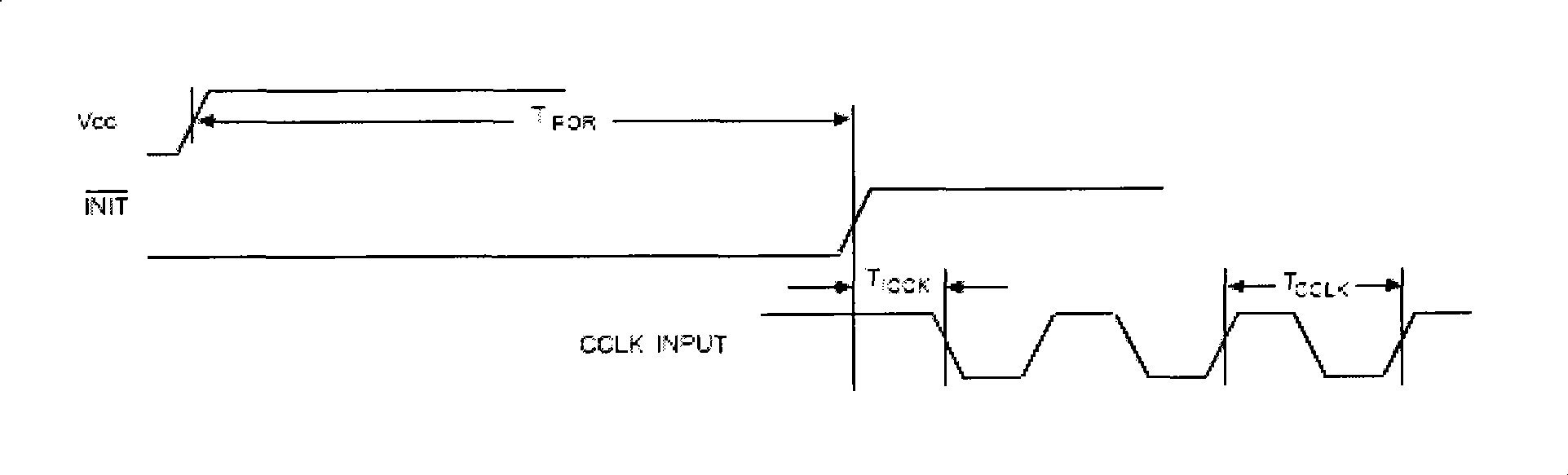

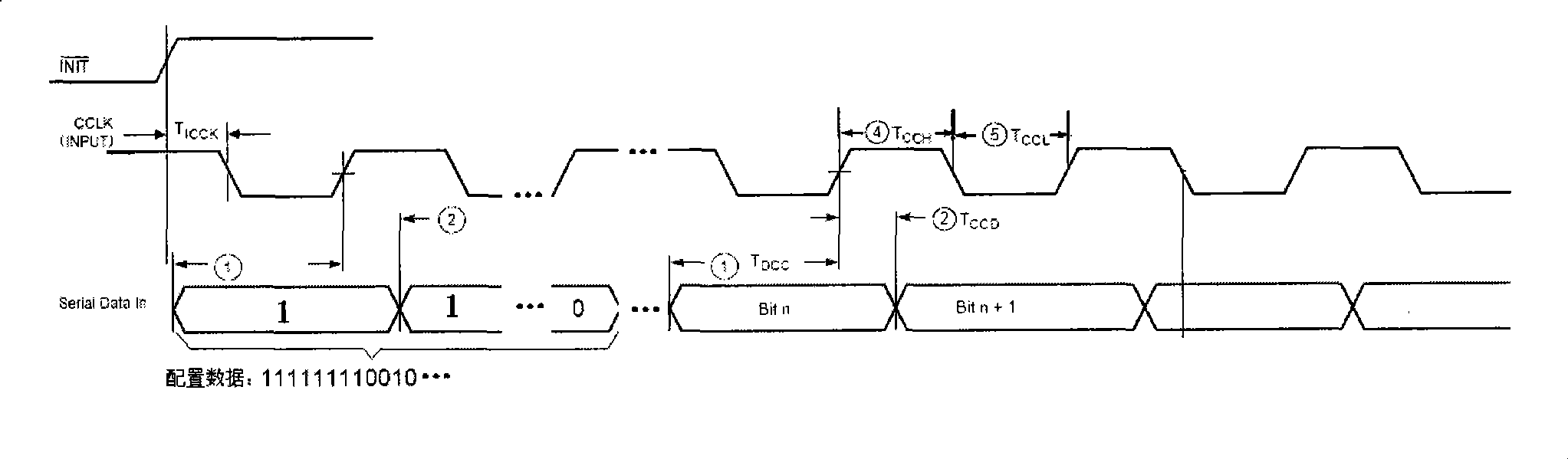

[0029] The problem to be solved by the invention is how to use the existing integrated circuit testing machine to perform the industrialized testing task of the FPGA device. At present, the number of pins of more advanced FPGA devices exceeds 1000, requiring the integrated circuit tester to have more channels than the number of pins of the FPGA device under test, or to have the function of channel multiplexing. For FPGA devices, the length of the test vector for each test is determined by the complexity of the configuration circuit and the purpose of the test, and the length of the test vectors for each test is different. For example, the length of the test vector of the configuration file of the Xilinx4010E FPGA device series device is 178k lines, and the length of the test vector varies during the test process. To test FPGA devices, it is necessary to repeat many "configuration-test" processes. Therefore, the test vector space depth of the integrated circuit tester is requir...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com