Method for controlling sheet resistance of poly in fabrication of semiconductor device

A manufacturing process, sheet resistance technology, applied in semiconductor/solid-state device manufacturing, semiconductor/solid-state device testing/measurement, circuits, etc., and can solve problems such as resistance differences

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

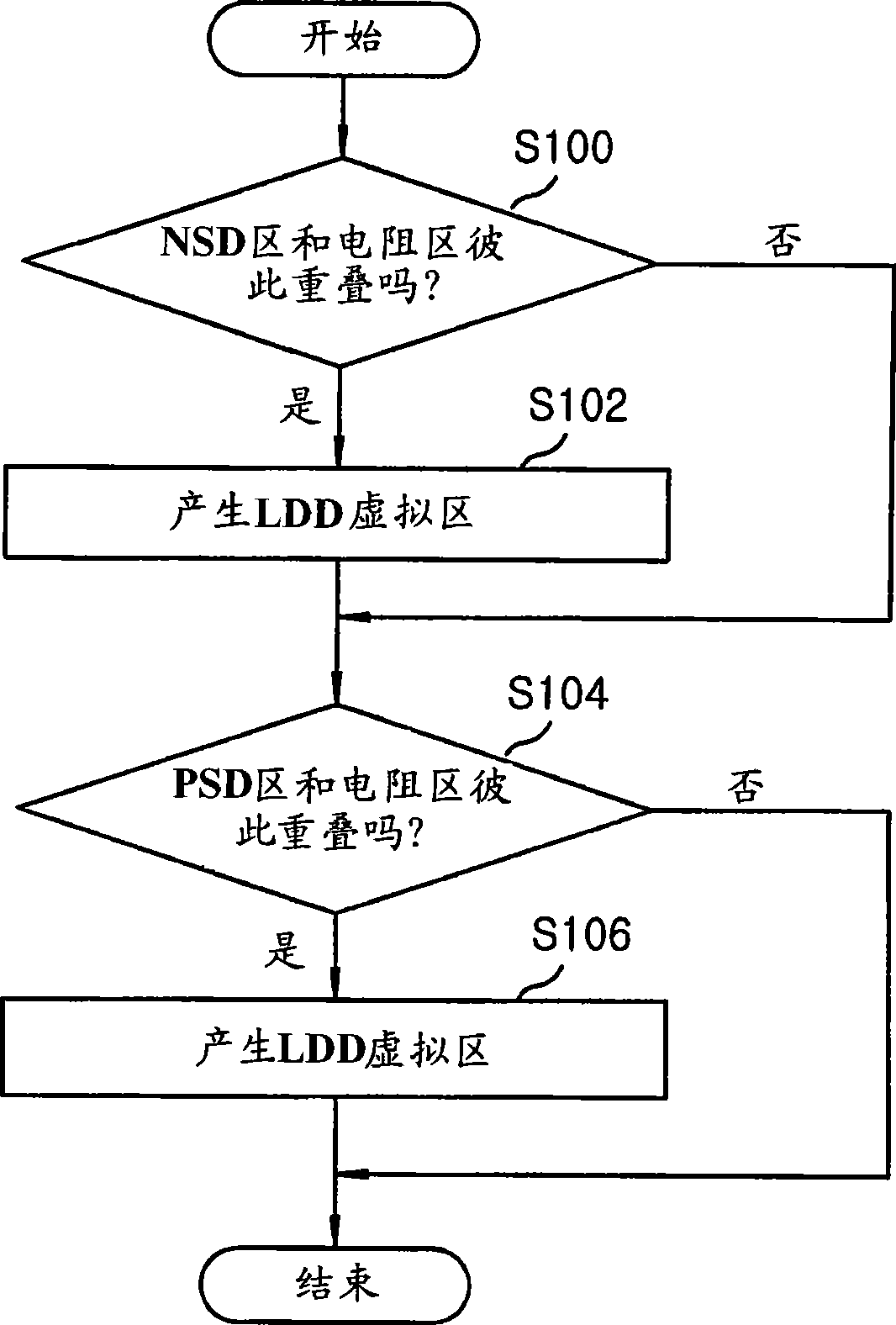

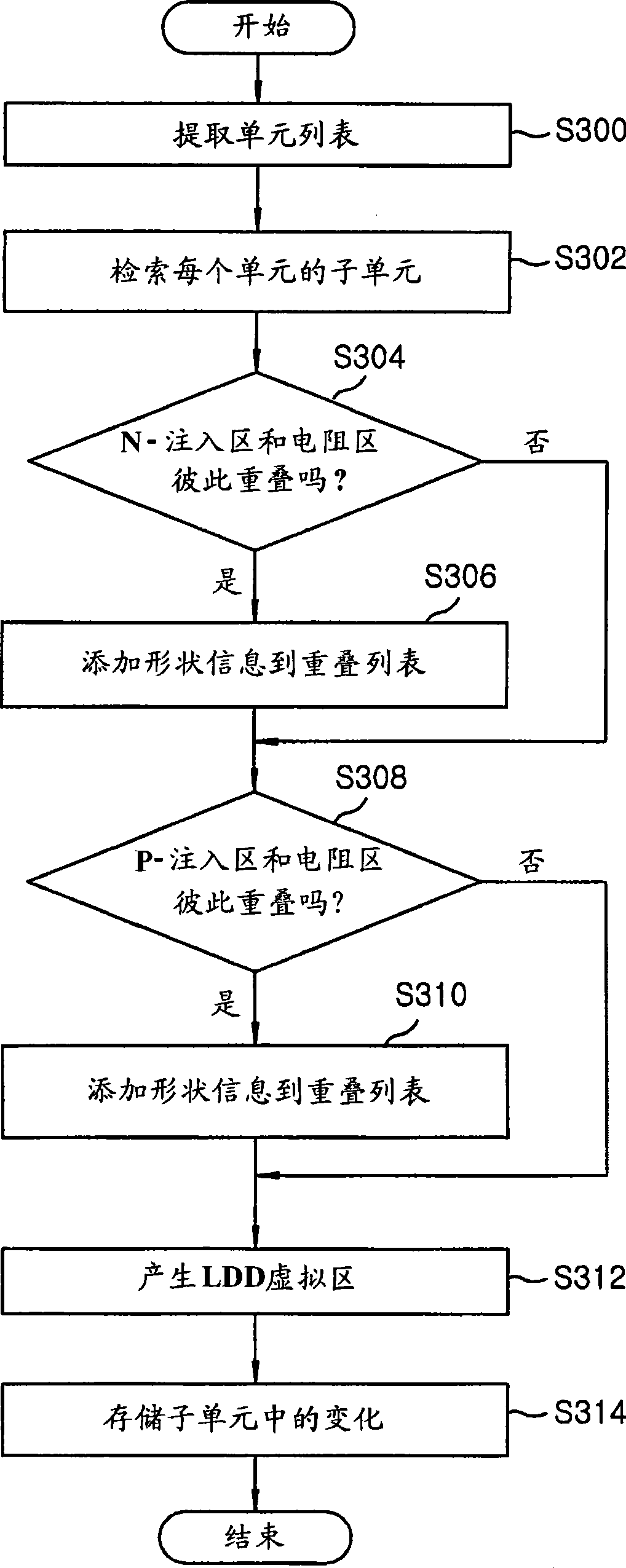

Method used

Image

Examples

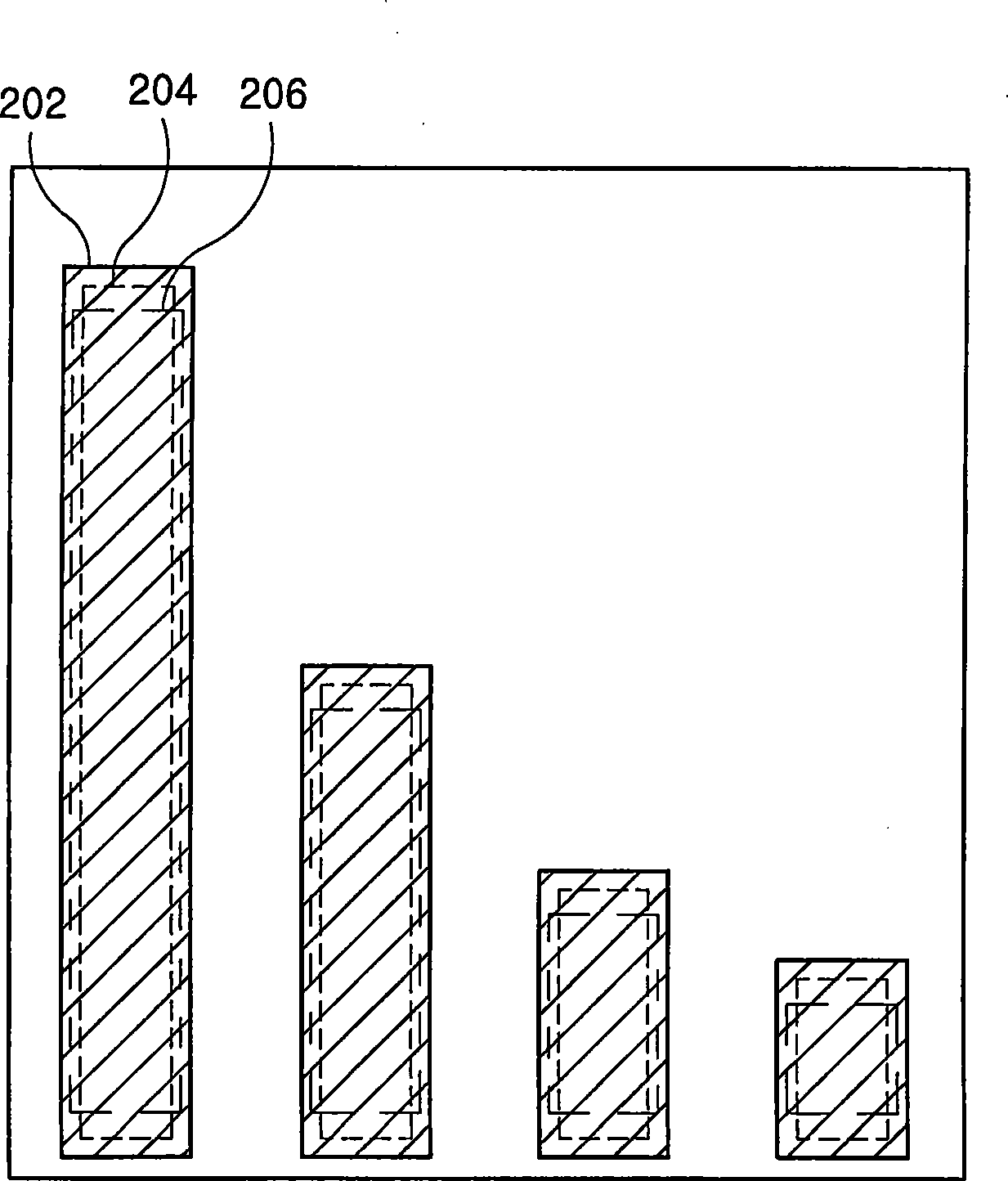

Embodiment Construction

[0017] In the following detailed description of the embodiments, reference will now be made in detail to certain specific embodiments of the invention and to the embodiments illustrated in the accompanying drawings. Wherever possible, the same symbols will be used throughout the drawings to refer to the same or like parts. These specific embodiments are described in sufficient detail to enable those skilled in the art to practice the invention. Other embodiments may be utilized and structural, logical, electrical changes may be made without departing from the scope of the present invention. Moreover, it can be understood that various specific embodiments of the present invention, although different, are not necessarily independent of each other. For example, a distinctive feature, structure or characteristic described in one embodiment may also be included in other embodiments. Therefore, the following detailed description should not be interpreted as limiting, but the scope...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com