Three-dimensional stacking encapsulation method based on silicon through-hole

A packaging method and three-dimensional stacking technology, applied in semiconductor devices, electrical components, circuits, etc., can solve problems such as through-hole voids, high through-hole resistance, premature sealing, etc., to simplify packaging steps, improve reliability, and uniform density. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0012] An embodiment of the TSV-based three-dimensional stack packaging method of the present invention is described below with reference to the accompanying drawings, in order to further understand the purpose, specific structural features and advantages of the present invention.

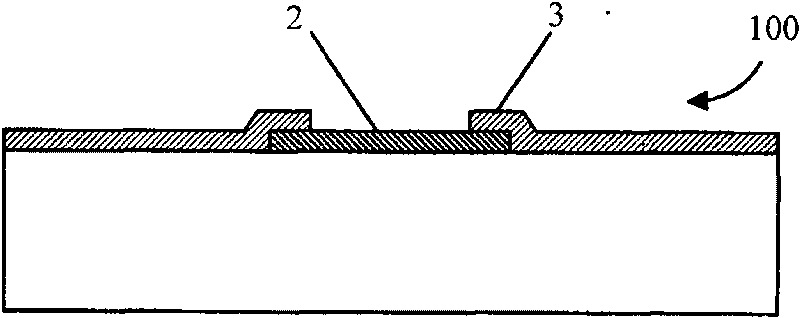

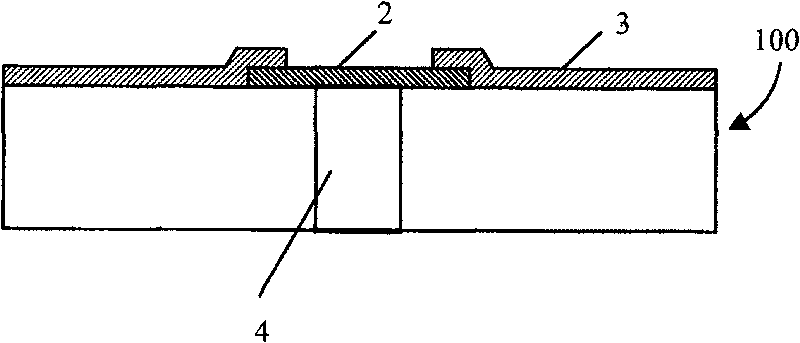

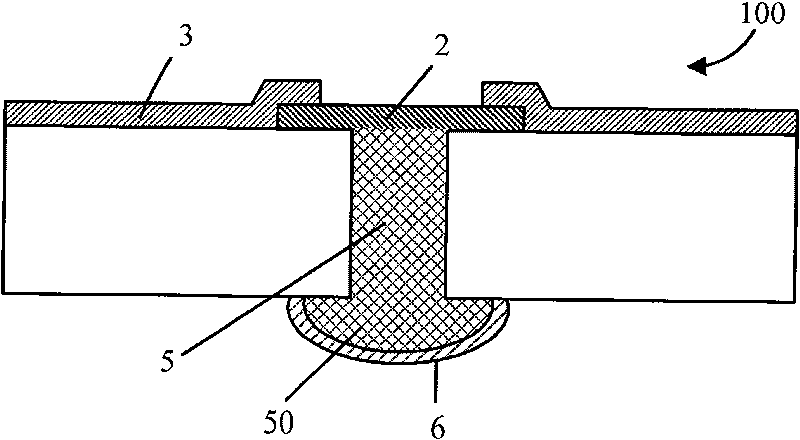

[0013] see figure 1 , the package-on-package method of the present invention includes the following steps. Firstly, several wafers to be packaged are provided. Since the steps of making TSVs are the same for each wafer, the description of the following steps takes the wafer 100 as an example. The front side of the wafer 100 has several welding pads 2 , a barrier layer (silicon dioxide) 3 is deposited on the front side of the wafer 100 , and then an etching step is performed to expose the welding pads 2 . see figure 2 , plate photoresist (not shown) on the back of the wafer, perform photolithography (exposure, development) steps, form photolithographic patterns, and then use Deep Reactive Etch (D...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More