Parallel system bus construction and port configuration management method thereof

A system bus and downlink port technology, applied in transmission systems, bus networks, data exchange through path configuration, etc., can solve the problems of small bandwidth and cannot meet high bandwidth, reduce the number of pins, meet cost design requirements, Effect of Low Cost Design Requirements

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0025] Embodiment 1: Realize the correspondence between uplink and downlink ports by adjusting the aggregation chip port of the main control board

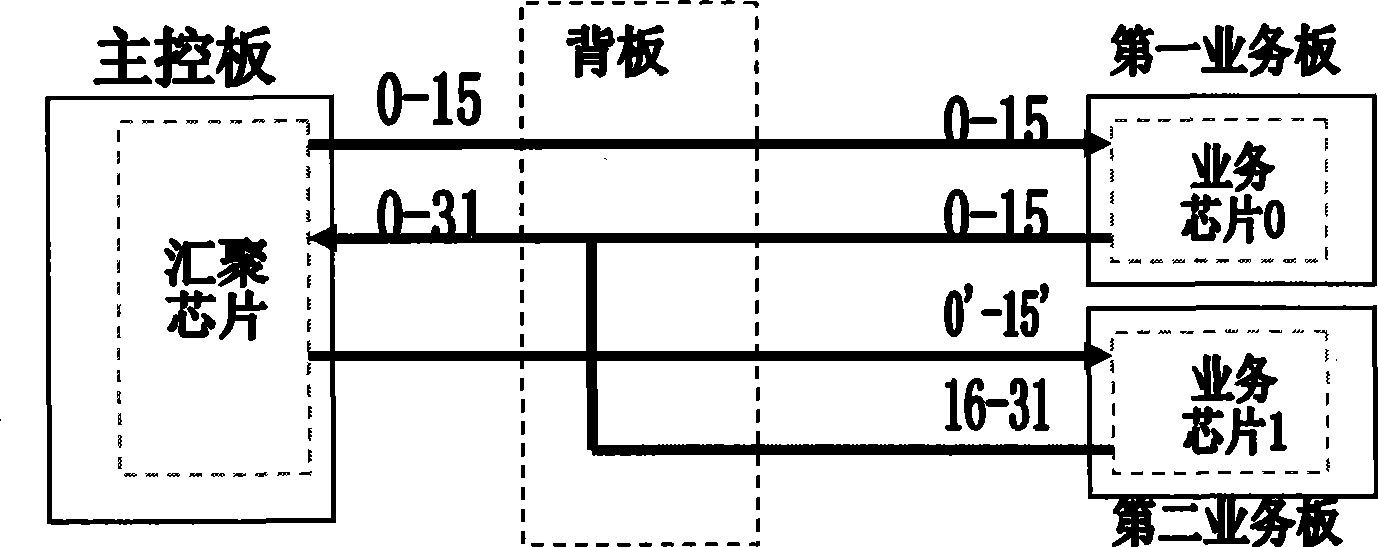

[0026] Such as image 3 As shown, in the downstream direction, 0 to 15 downstream ports of the aggregation chip in the main control board are mapped one by one with 0 to 15 downstream ports of the service chip 0 in the first service board, and the aggregation chip in the main control board The 0' to 15' downlink ports of the second service board are mapped one by one with the 0' to 15' downlink ports of the service chip 1 in the second service board;

[0027] In the uplink direction, the 0 to 15 uplink ports of the service chip 0 in the first service board are mapped one by one with the 0 to 15 uplink ports of the aggregation chip of the main control board, and the service chip in the second service board The 16 to 31 uplink ports of the main control board are mapped one by one with the 0' to 15' uplink ports of the aggregation c...

Embodiment 2

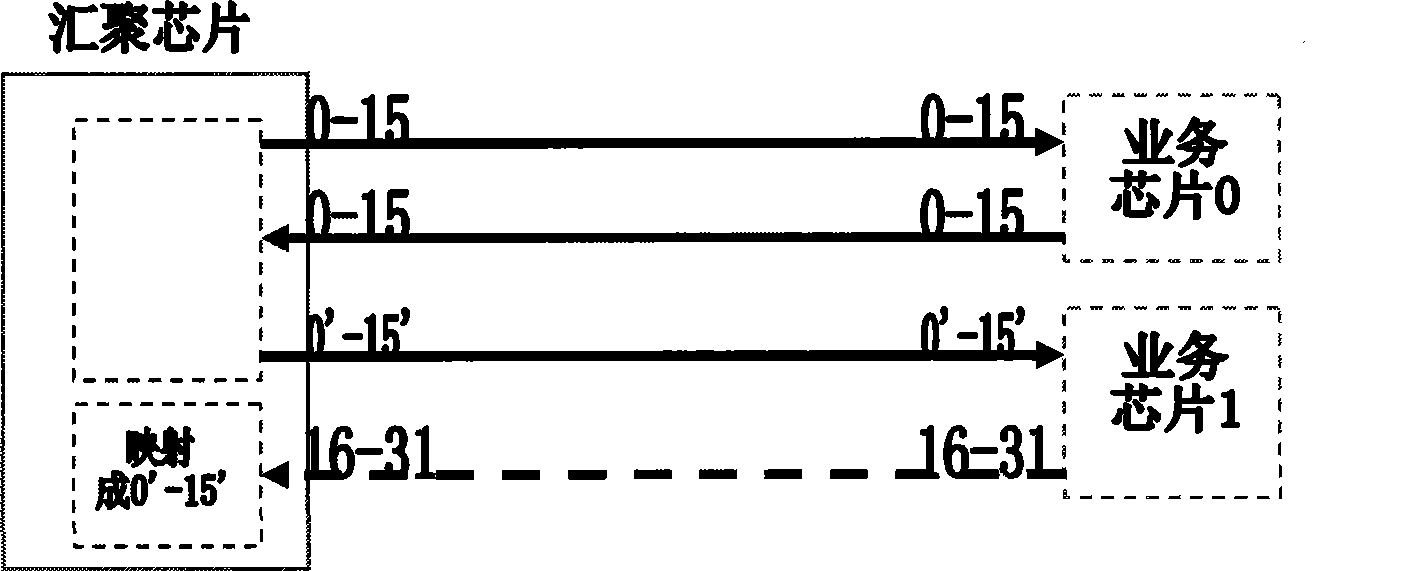

[0028] Embodiment 2: Realize the correspondence between uplink and downlink ports by adjusting the service chip ports of the service board

[0029] Such as Figure 4 As shown, in the downstream direction, 0 to 15 downstream ports of the aggregation chip in the main control board are mapped one by one with 0 to 15 downstream ports of the service chip 0 in the first service board, and the aggregation chip in the main control board The 0' to 15' downlink ports of the second service board are mapped one by one with the 16' to 31' downlink ports of the service chip 1 in the second service board;

[0030] In the uplink direction, the 0 to 15 uplink ports of the service chip 0 in the first service board are mapped one by one with the 0 to 15 uplink ports of the aggregation chip of the main control board, and the service chip in the second service board The 16 to 31 uplink ports of 1 are mapped one by one with the 16 to 31 uplink ports of the aggregation chip of the main control boar...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More