Fault-tolerance memory and error-correction error-tolerance method

An error correction method and memory technology, applied in the field of memory fault tolerance, can solve the problems of reducing memory performance and storage units cannot be effectively replaced, and achieve the effects of reduced delay, good repair efficiency, and cost reduction

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

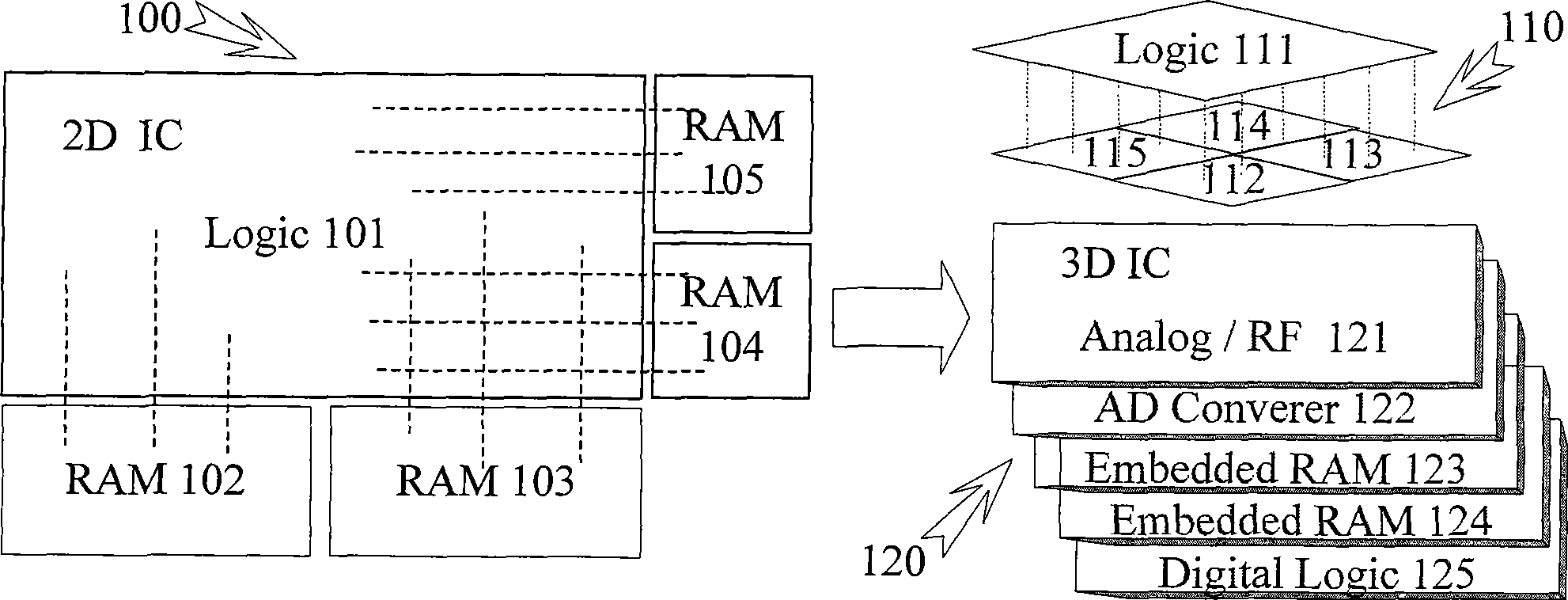

[0038] First, construct the three-dimensional fault-tolerant memory structure designed by the present invention, which includes: words with error correction codes, three-dimensional hierarchical distribution of multiple granular redundancy, three-dimensional hierarchical distribution of built-in self-test, self-diagnosis and self-repair circuit structure , And its hierarchical structure is as follows Figure 3A , 3B , 3C and 3D, the overall structure is shown in Figure 4.

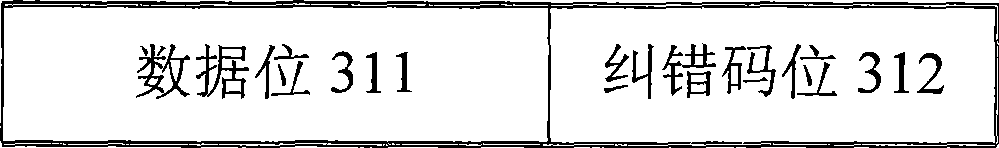

[0039] Figure 3A Shown is the word structure 310 of the memory. This word not only contains inherent data bits 311 for storage, but also contains error correction code bits 312 with a certain error correction function. This error correction code can detect one or more instantaneous errors in the memory word in real time, which is commonly referred to as soft fault, and correct the erroneous bits that can be corrected in the soft fault according to the error correction capability.

[0040] Figure 3B Shown is...

Embodiment 2

[0069] A more specific embodiment of the present invention is given below. In this embodiment, the memory structure includes two layers of silicon wafers, and silicon wafer A is the storage body of the memory, which is composed of a number of first-layer memories, as shown in Figure 4. Show. The storage body of each layer 1 memory is composed of a number of layer 0 memories, the public redundant row is composed of rows of a number of layer 0 memories arranged side by side, and the public redundant column is composed of a number of rows of layer 0 memory arranged in series. The error-correction-tolerant circuit and decoding logic are only responsible for the error-correction-tolerance and decoding functions at this level, such as Figure 3C Shown. The storage body of each layer 0 memory is composed of a number of words with error correction codes, the private redundancy row is composed of words, and the private redundancy column is composed of bits serially. The error correction an...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More