Trench construction in MOS transistor

A MOS transistor and channel structure technology, applied in semiconductor devices, electrical components, circuits, etc., can solve the problems of increasing device area, unfavorable circuit manufacturing and cost reduction, etc., to increase driving capability and increase effective channel length Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

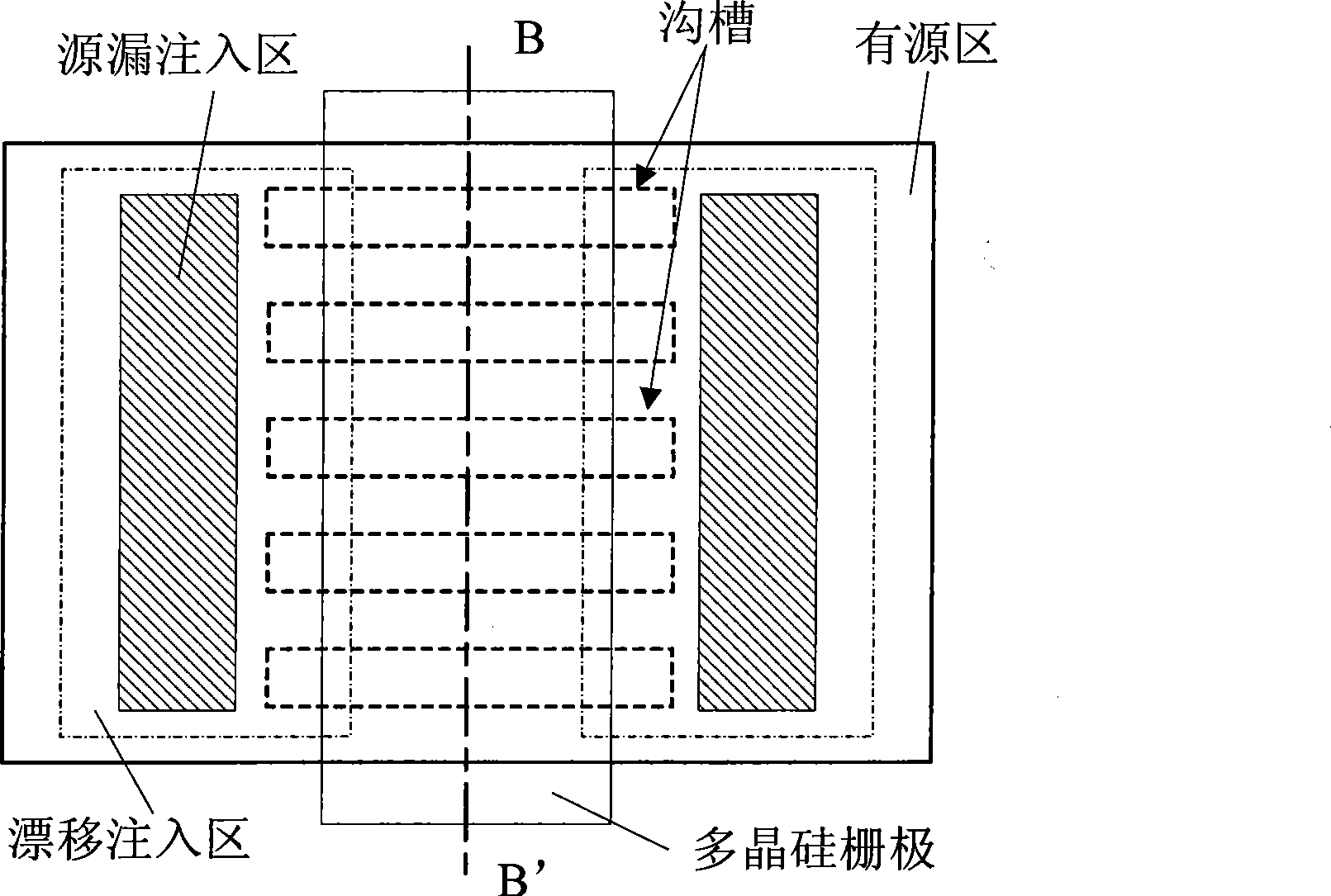

[0011] The channel structure in the MOS transistor of the present invention is provided with a plurality of trenches on the surface of the silicon substrate in the channel region, and the length direction of each trench is the same as that of the current generated in the channel region when the MOS transistor works. The direction of motion is the same.

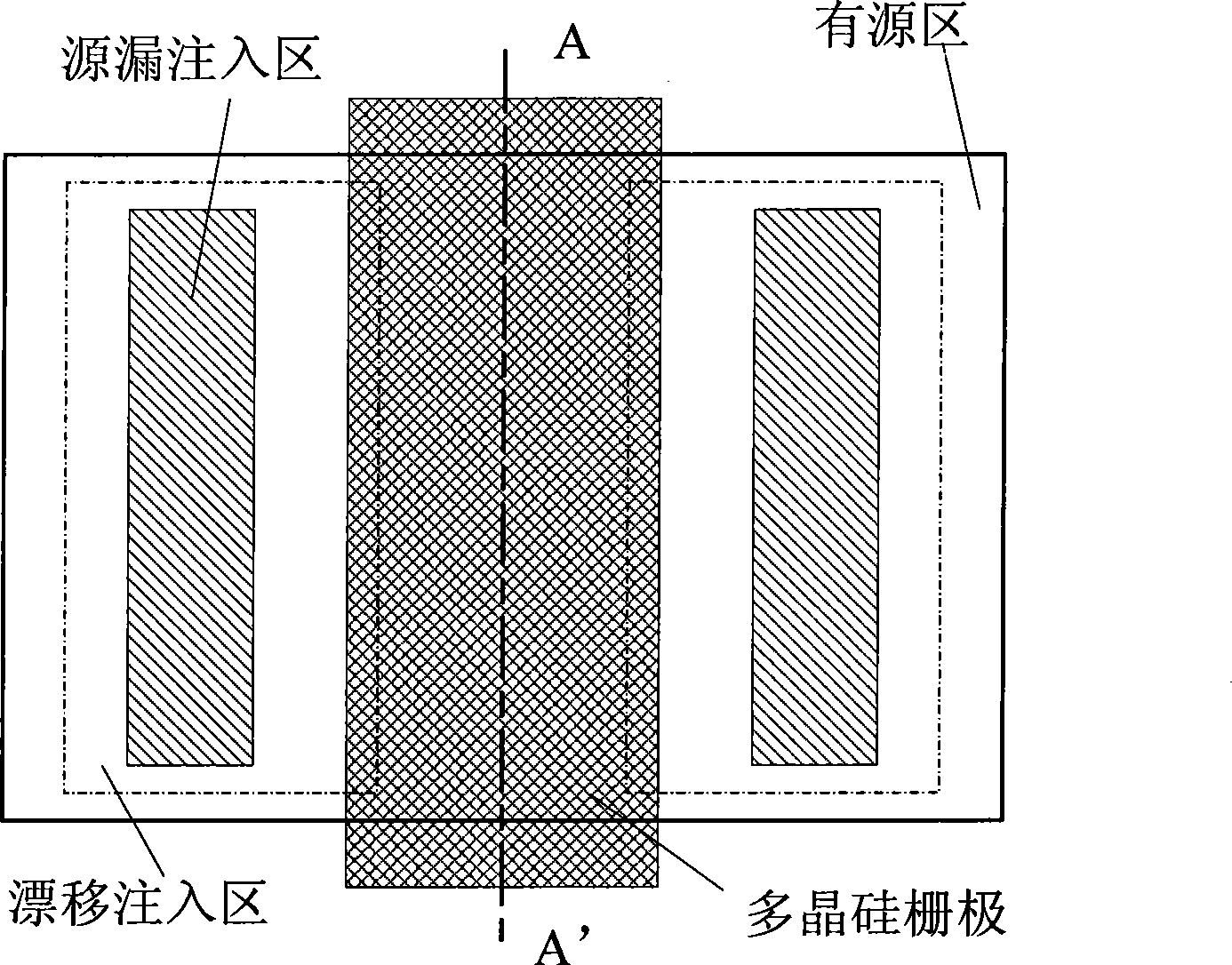

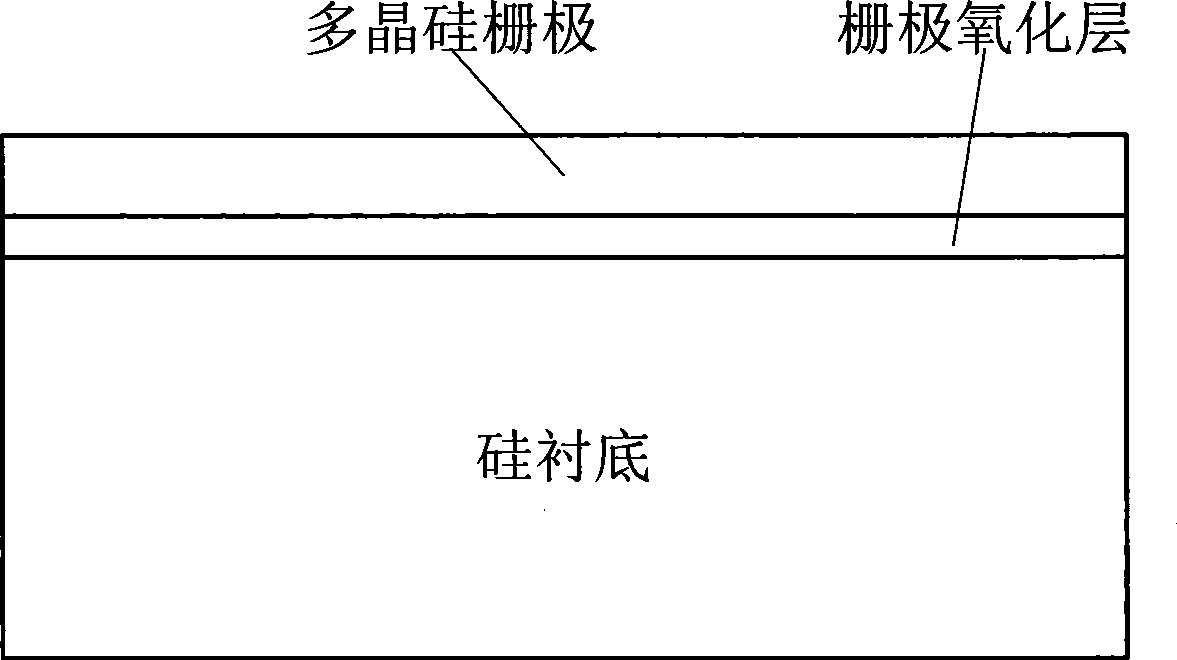

[0012] image 3 It is a schematic diagram of the layout of a specific MOS transistor of the present invention. The channel region between the source and drain regions under the polysilicon gate region is provided with a plurality of grooves, and the length direction of the grooves is the same as that generated in the channel region when the transistor works. The direction of current movement is the same, which is the horizontal direction in the figure. Figure 4 for along image 3 Schematic cross-sectional view of the BB' plane. Because the working principle of the MOS transistor is to generate a current effect on the silic...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More