Patents

Literature

33 results about "Planar channel" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

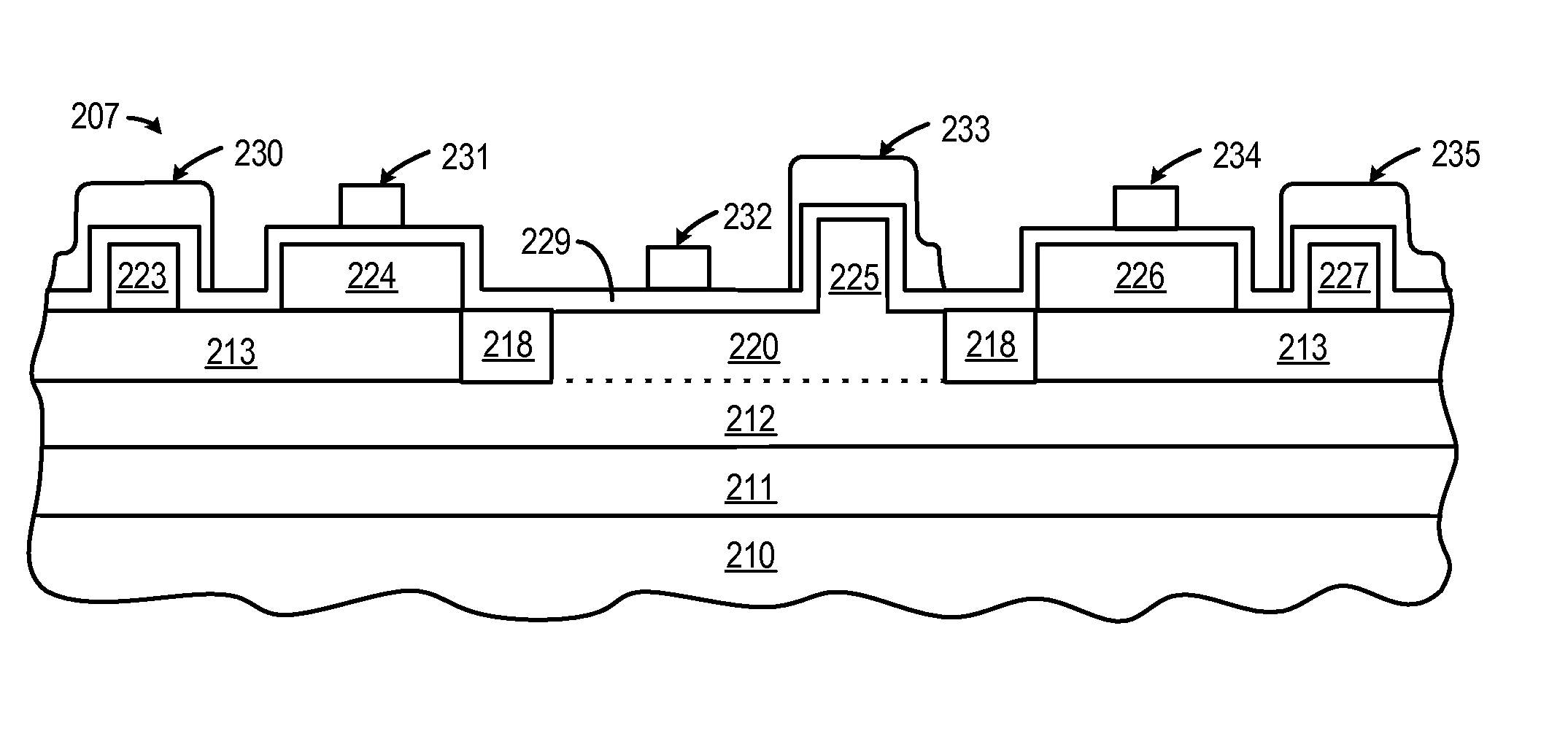

Twisted Dual-Substrate Orientation (DSO) Substrates

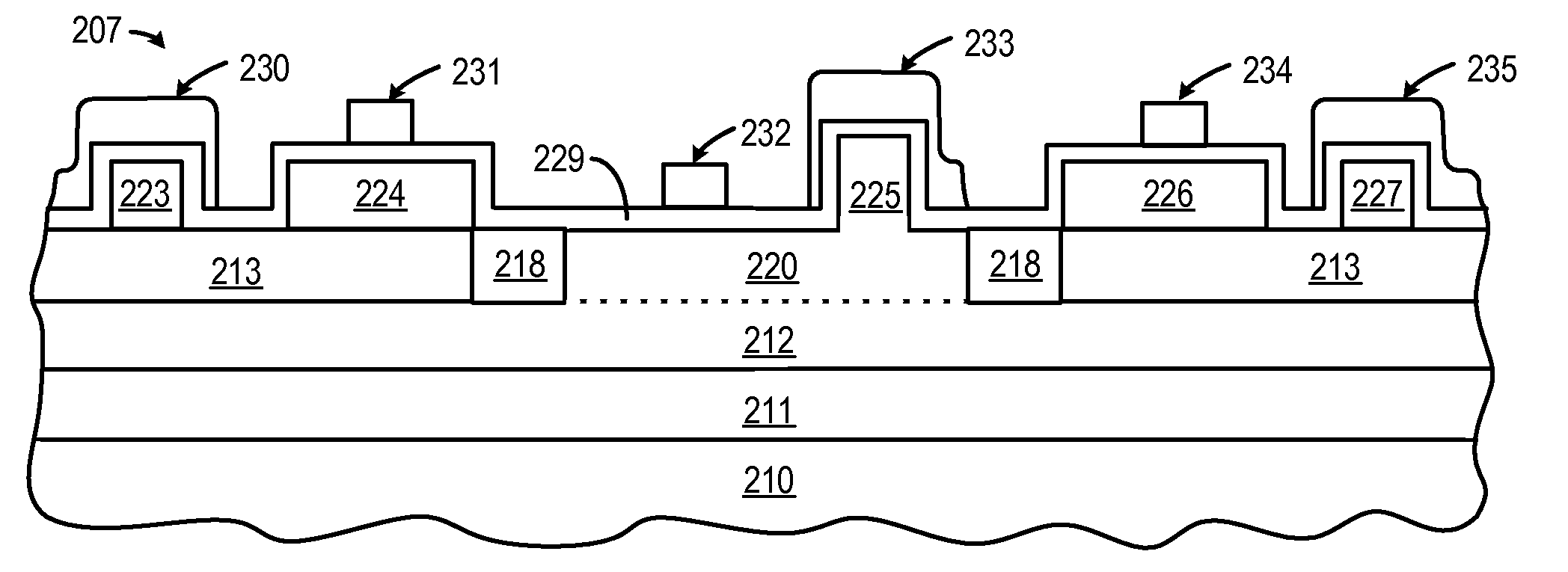

A semiconductor process and apparatus provide a dual or hybrid substrate by forming a second semiconductor layer (214) that is isolated from, and crystallographically rotated with respect to, an underlying first semiconductor layer (212) by a buried insulator layer (213); forming an STI region (218) in the second semiconductor layer (214) and buried insulator layer (213); exposing the first semiconductor layer (212) in a first area (219) of a STI region (218); epitaxially growing a first epitaxial semiconductor layer (220) from the exposed first semiconductor layer (212); and selectively etching the first epitaxial semiconductor layer (220) and the second semiconductor layer (214) to form CMOS FinFET channel regions (e.g, 223) and planar channel regions (e.g., 224) from the first epitaxial semiconductor layer (220) and the second semiconductor layer (214).

Owner:TAIWAN SEMICON MFG CO LTD

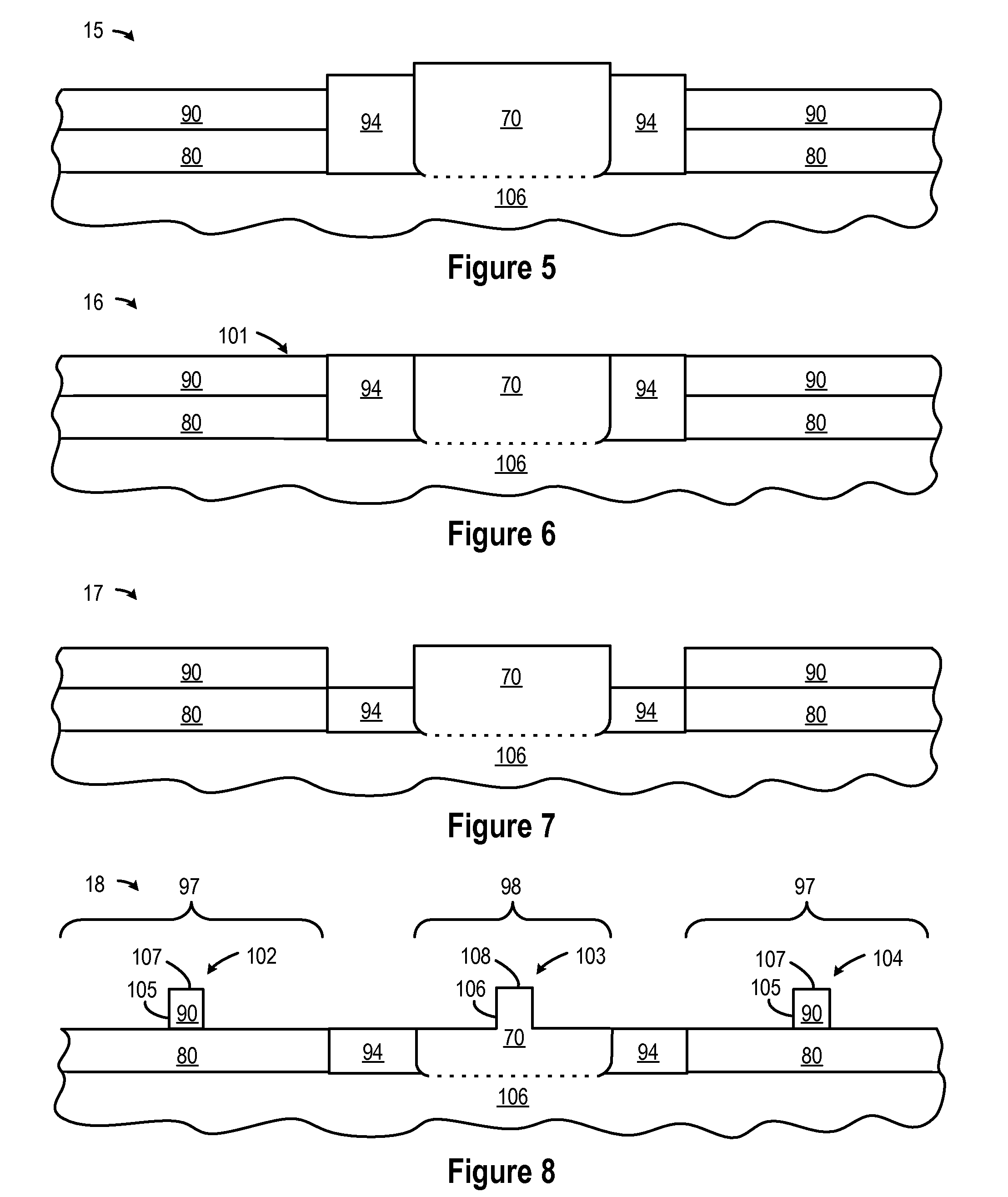

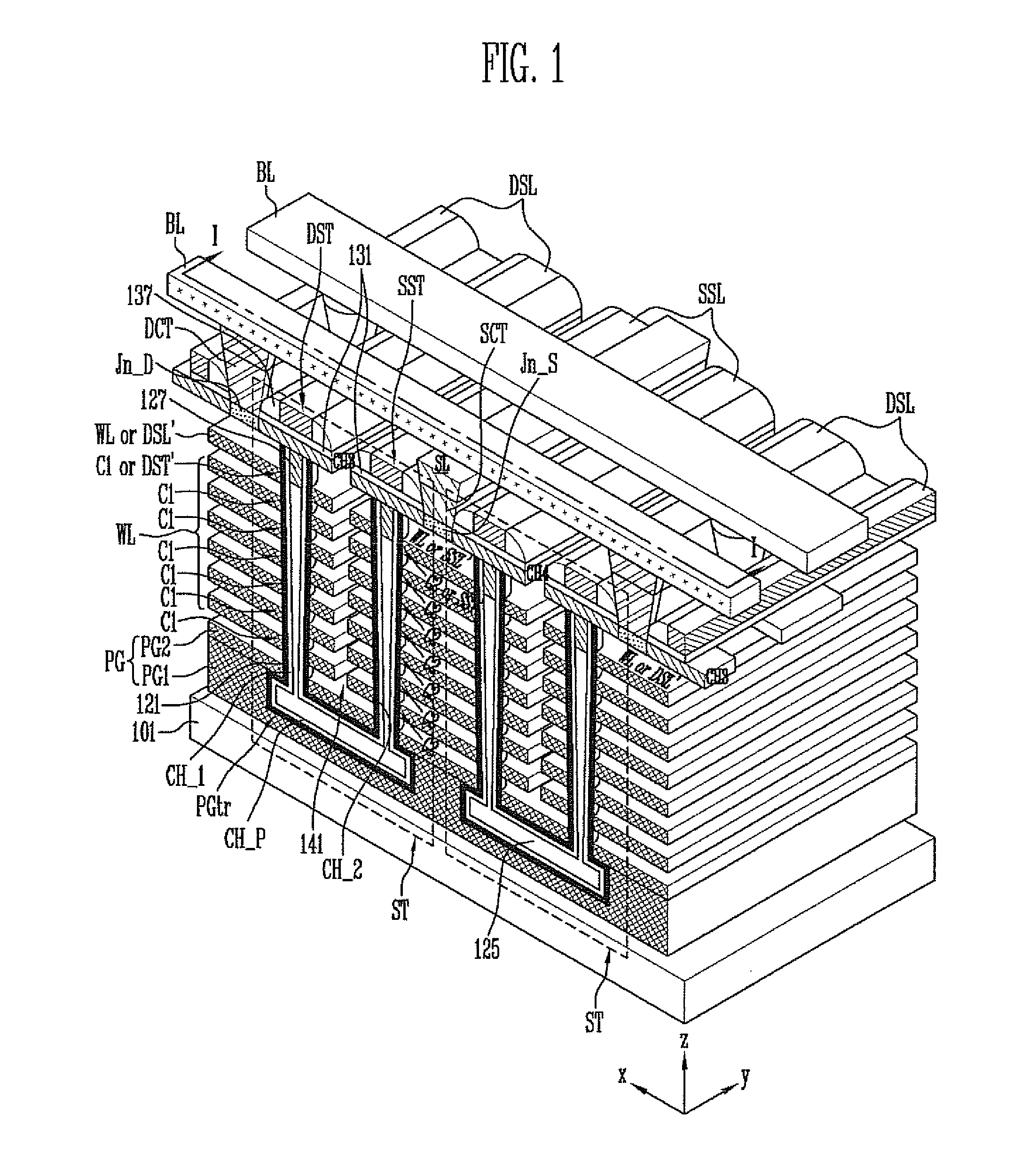

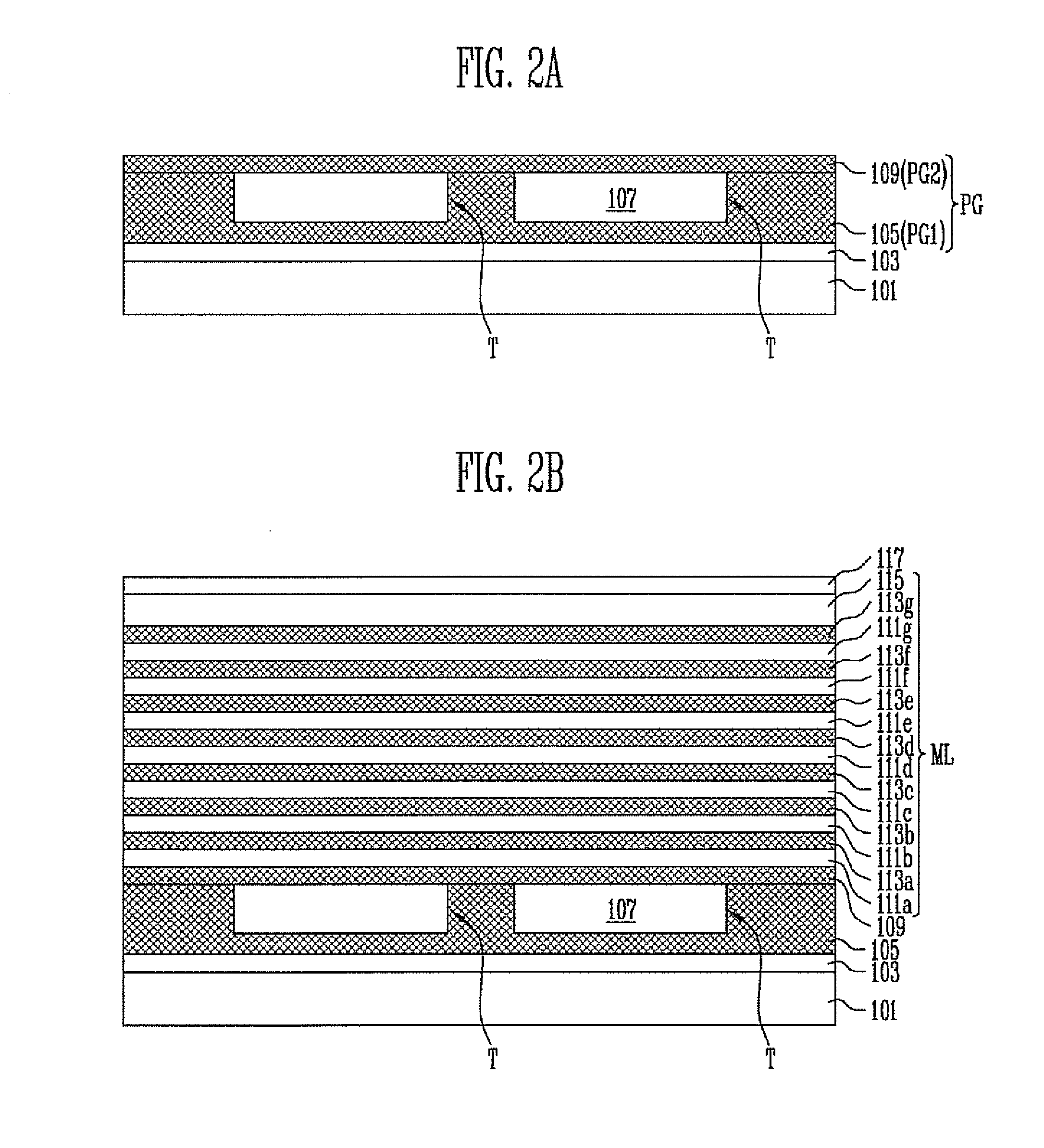

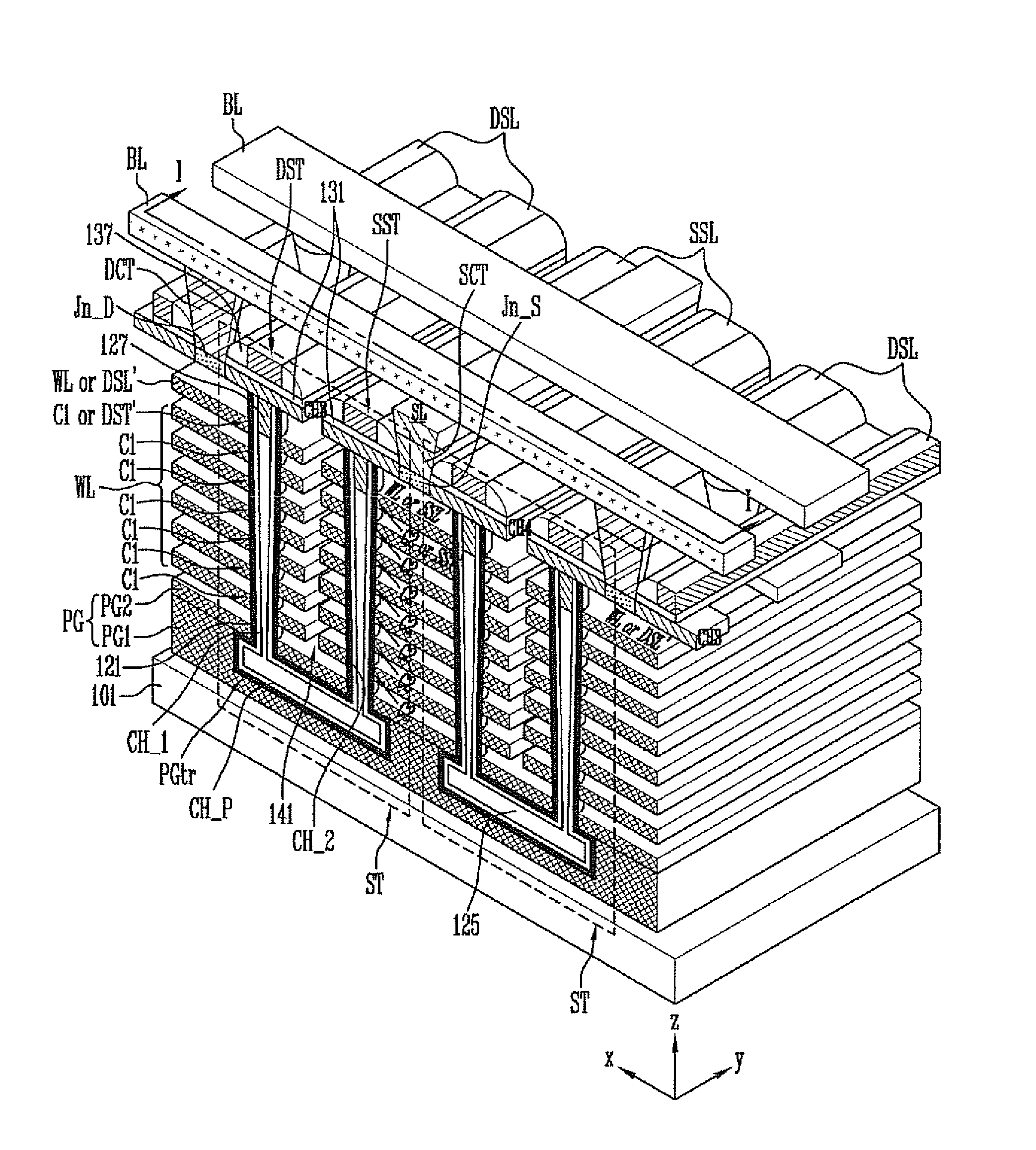

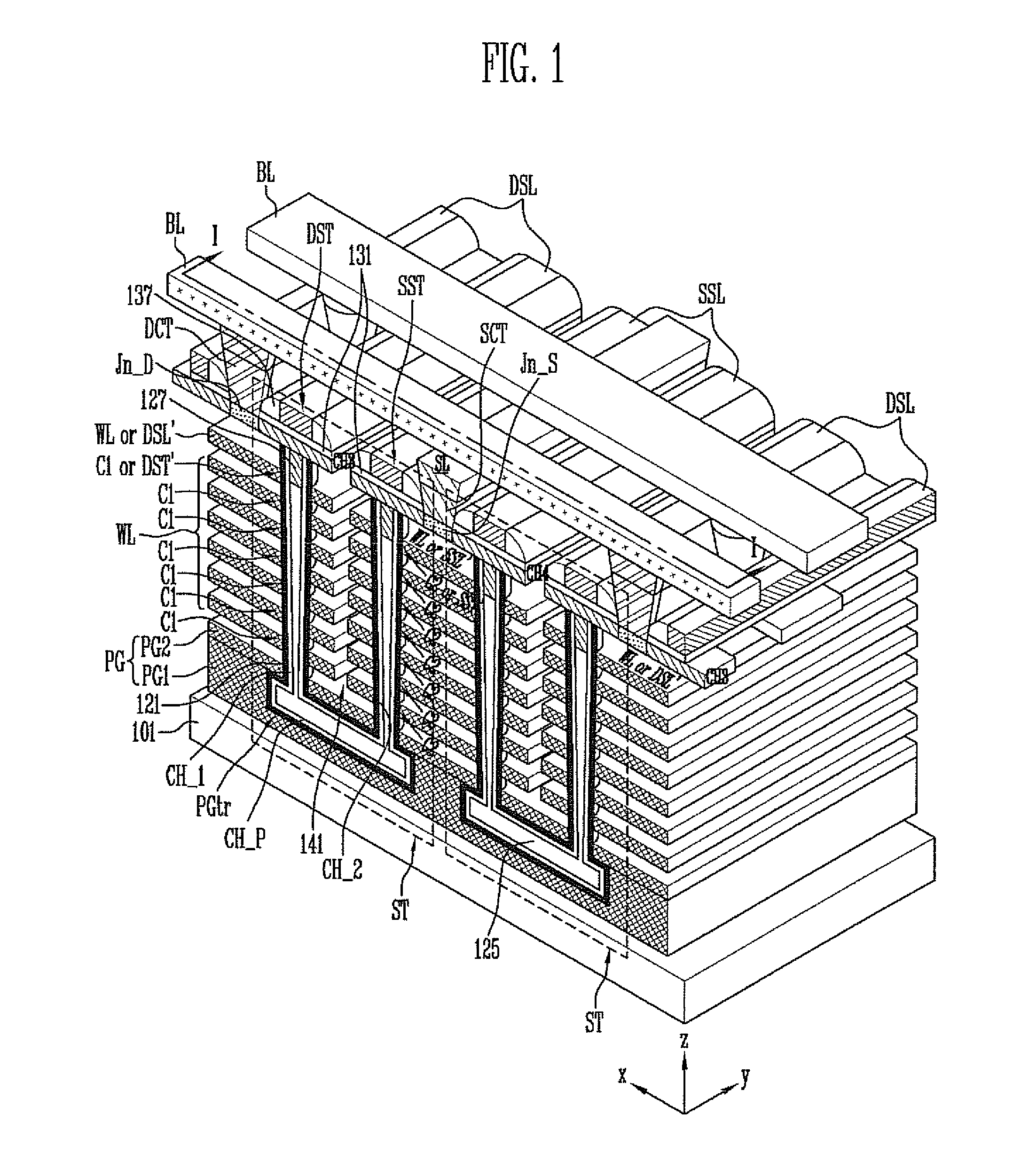

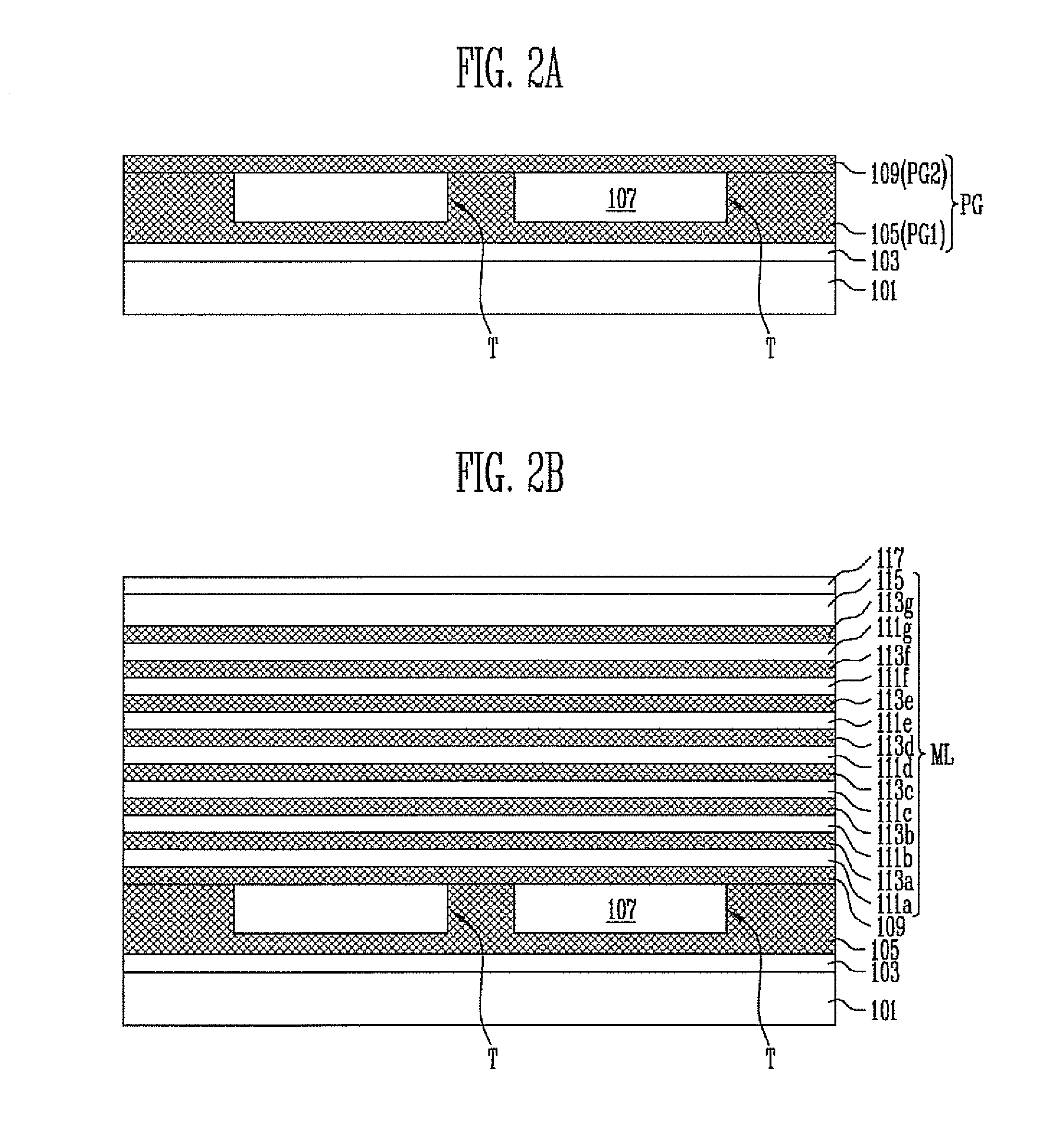

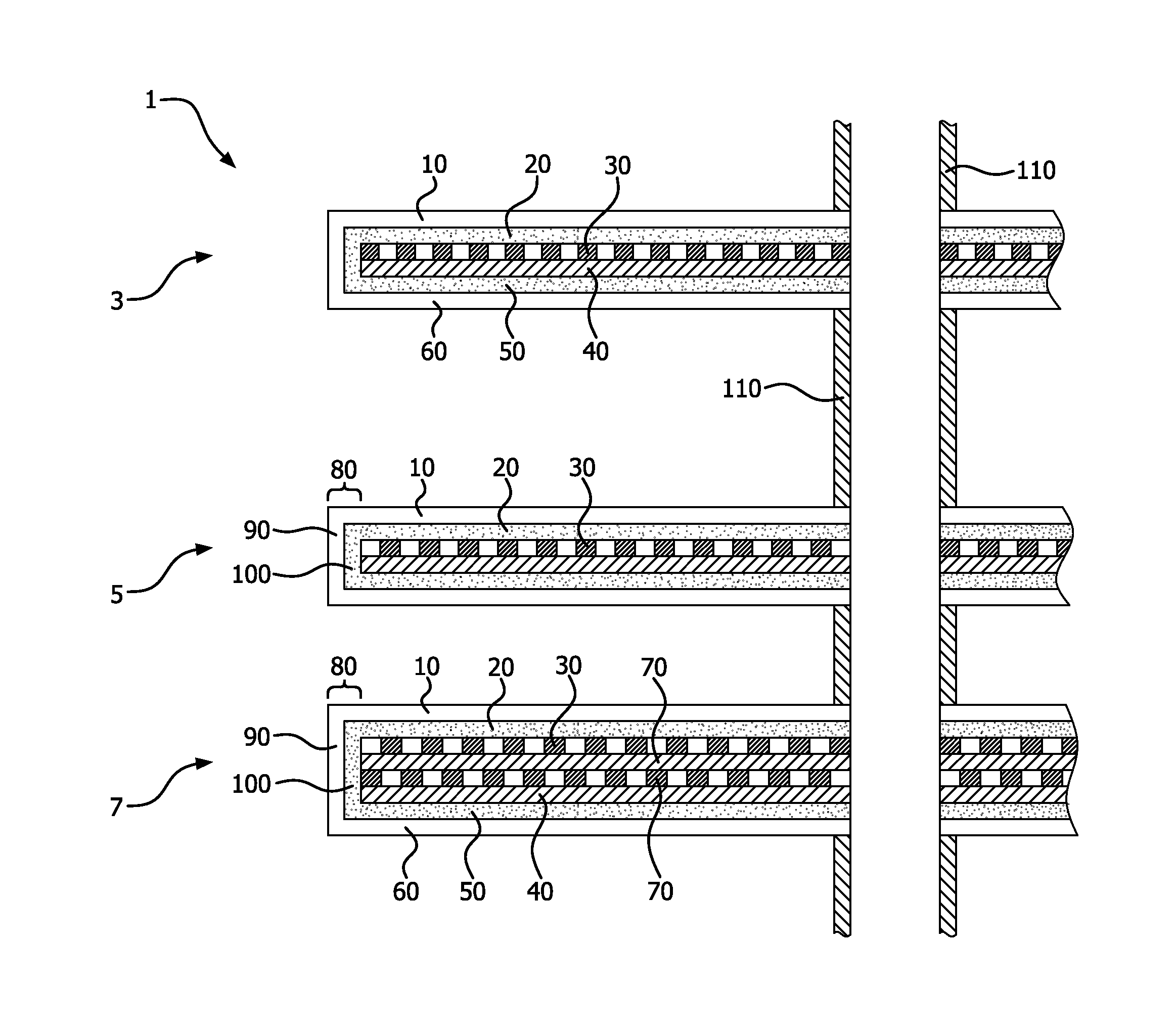

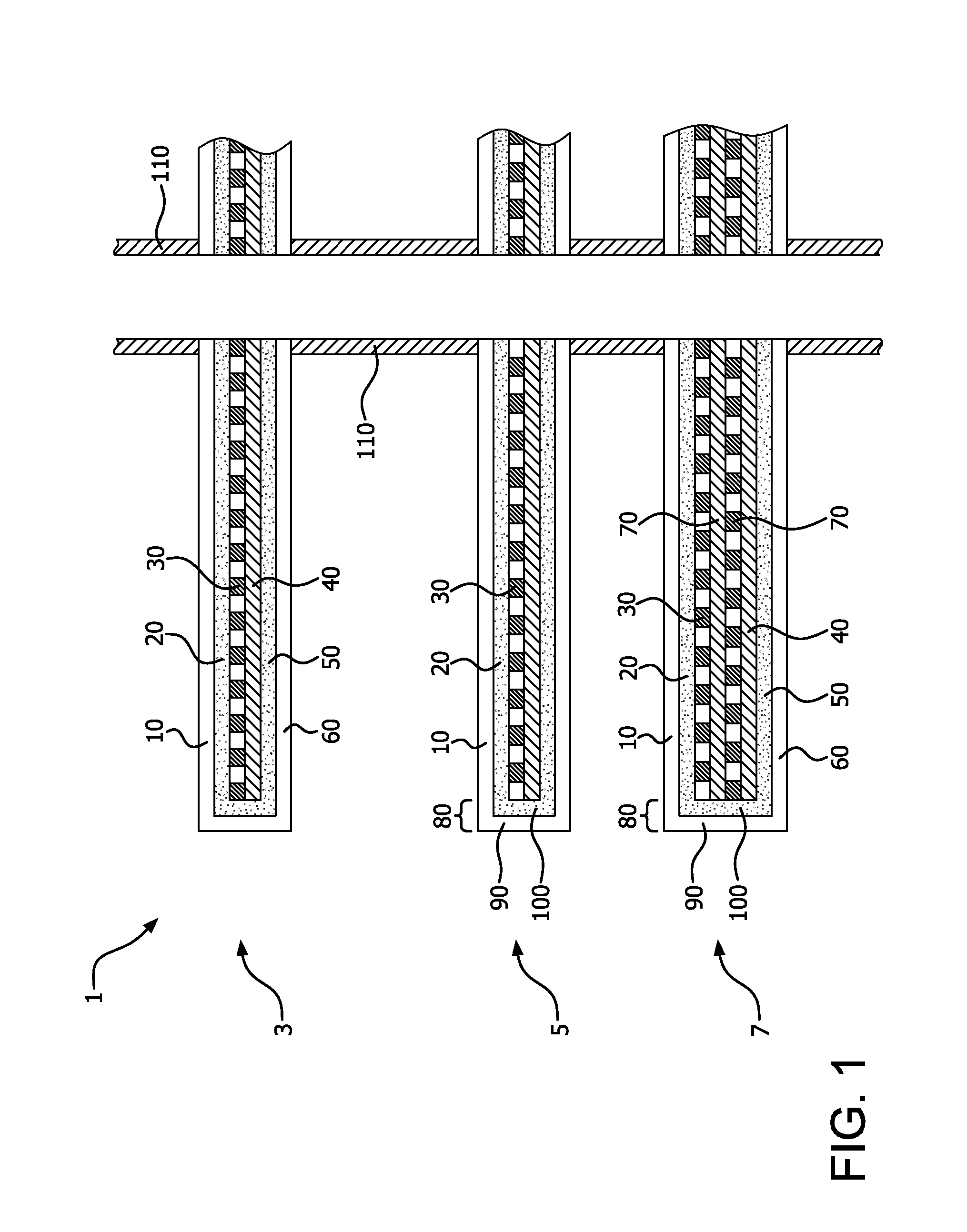

3-d nonvolatile memory device and method of manufacturing the same, and memory system including the 3-d nonvolatile memory device

A three-dimensional (3-D) nonvolatile memory device includes vertical channel layers protruded from a substrate, interlayer insulating layers and memory cells, which are alternately stacked along the vertical channel layers, and select transistors including planar channel layers, each contacted with at least one of the vertical channel layers and being parallel to the substrate, and gate insulating layers formed over the planar channel layers.

Owner:SK HYNIX INC

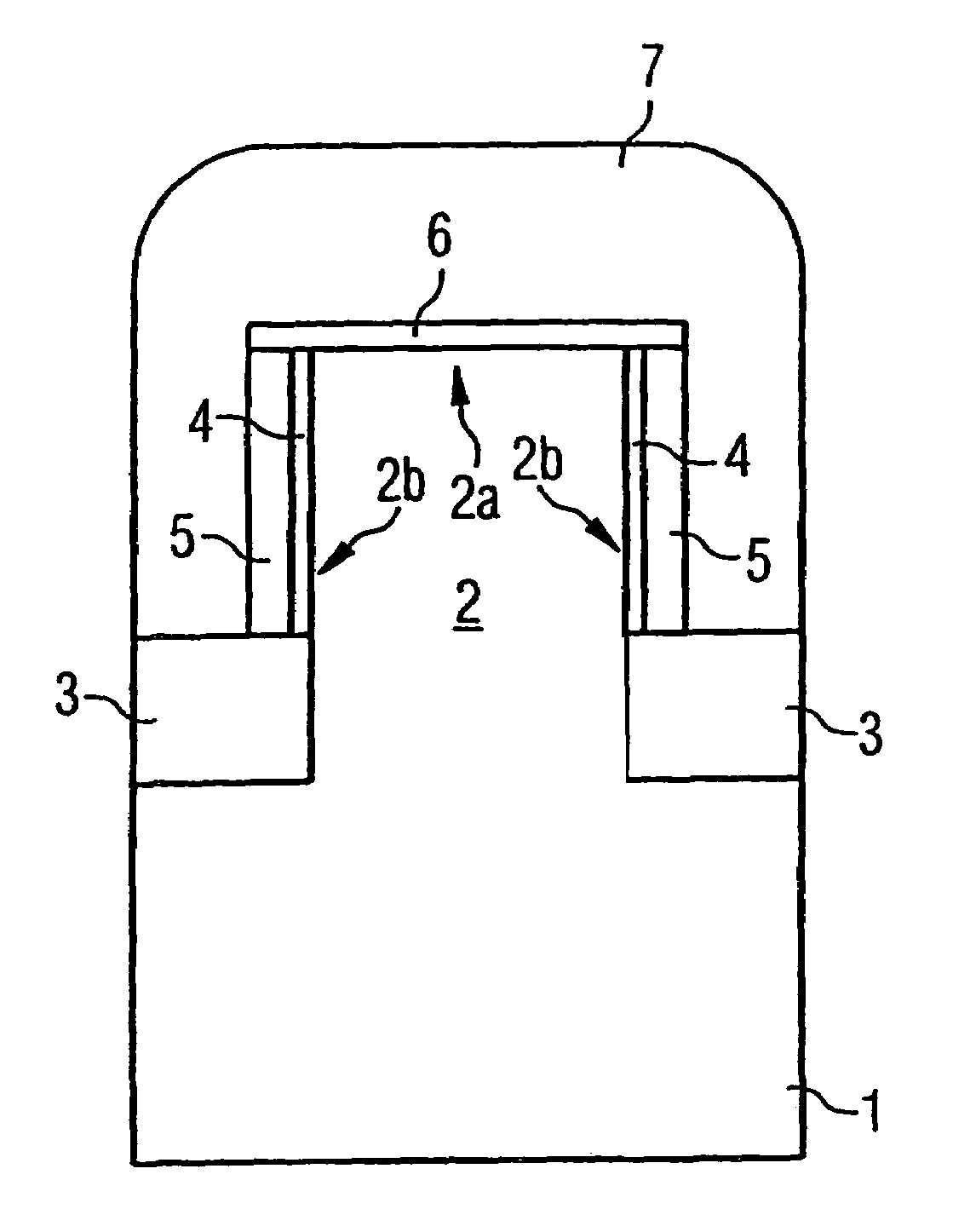

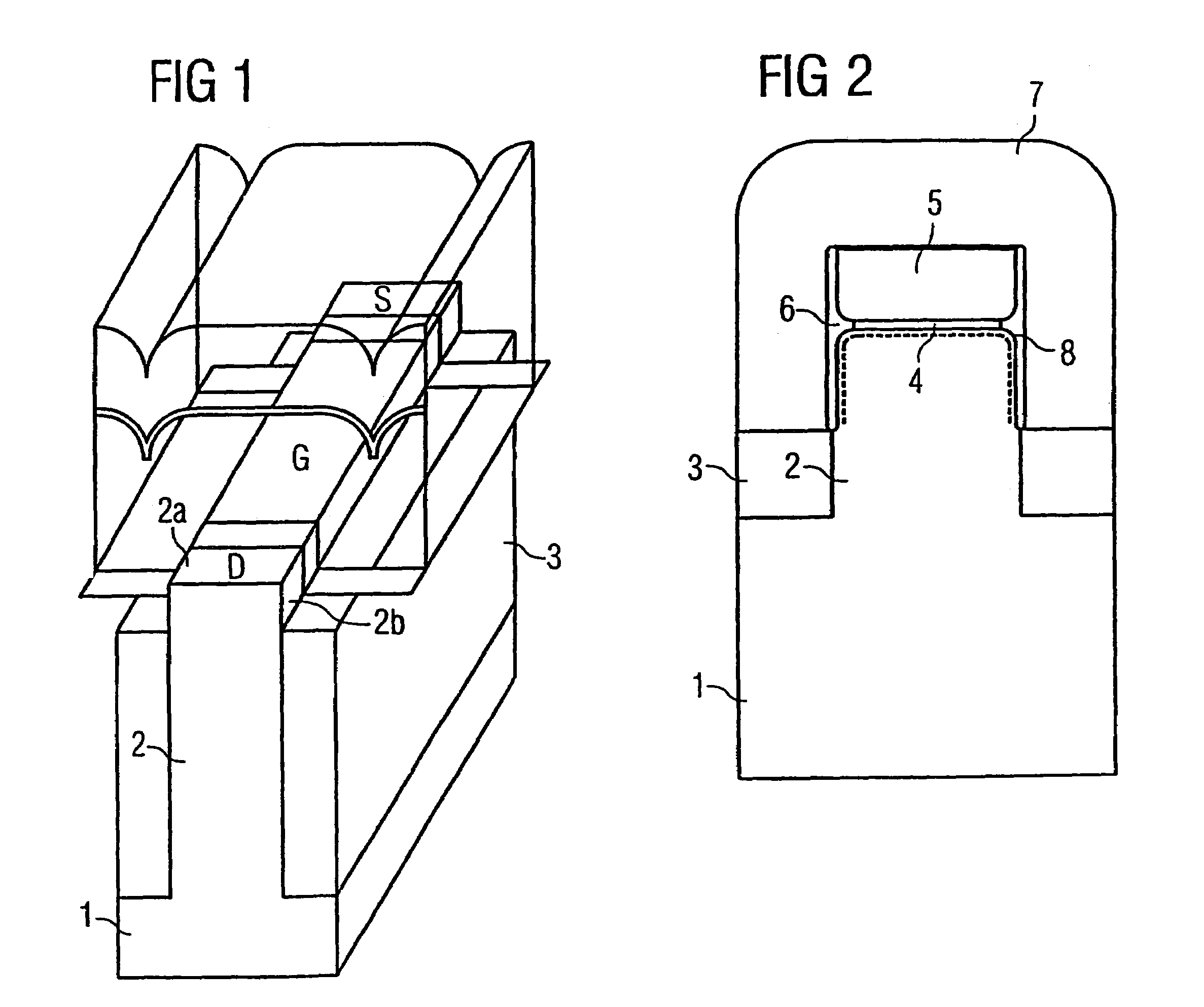

Field effect transistor and method for fabricating it

InactiveUS7119384B2Reduce spendingReduce and avoidTransistorSolid-state devicesPlanar channelReverse current

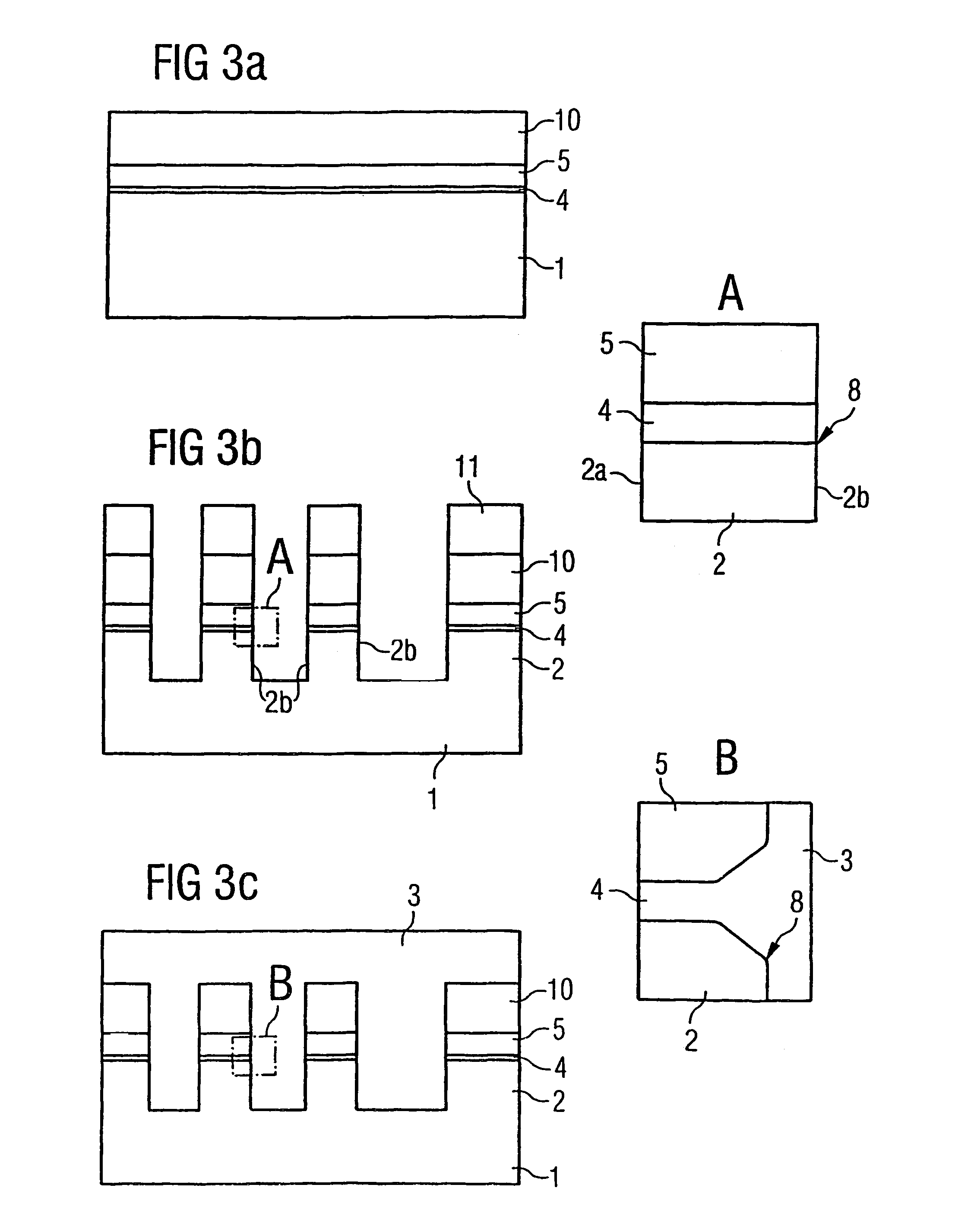

The invention relates to a field effect transistor in which the planar channel region on the upper surface of the elevation is extended in width by means of additional vertical channel regions on the lateral surfaces of the elevation. Said additional vertical channel regions connect directly to the planar channel region (vertical extended channel regions). Said field effect transistor has the advantage that a significant increase in the effective channel width for the current flow ION can be guaranteed relative to conventional transistor structures used up until the present, without having to accept a reduction in the achievable integration density. Said field effect transistor furthermore has a low reverse current IOFF. The above advantages are achieved without the thickness of the gate insulators up to the region of the charge transfer tunnels having to be reduced or a reduced stability.

Owner:POLARIS INNOVATIONS LTD

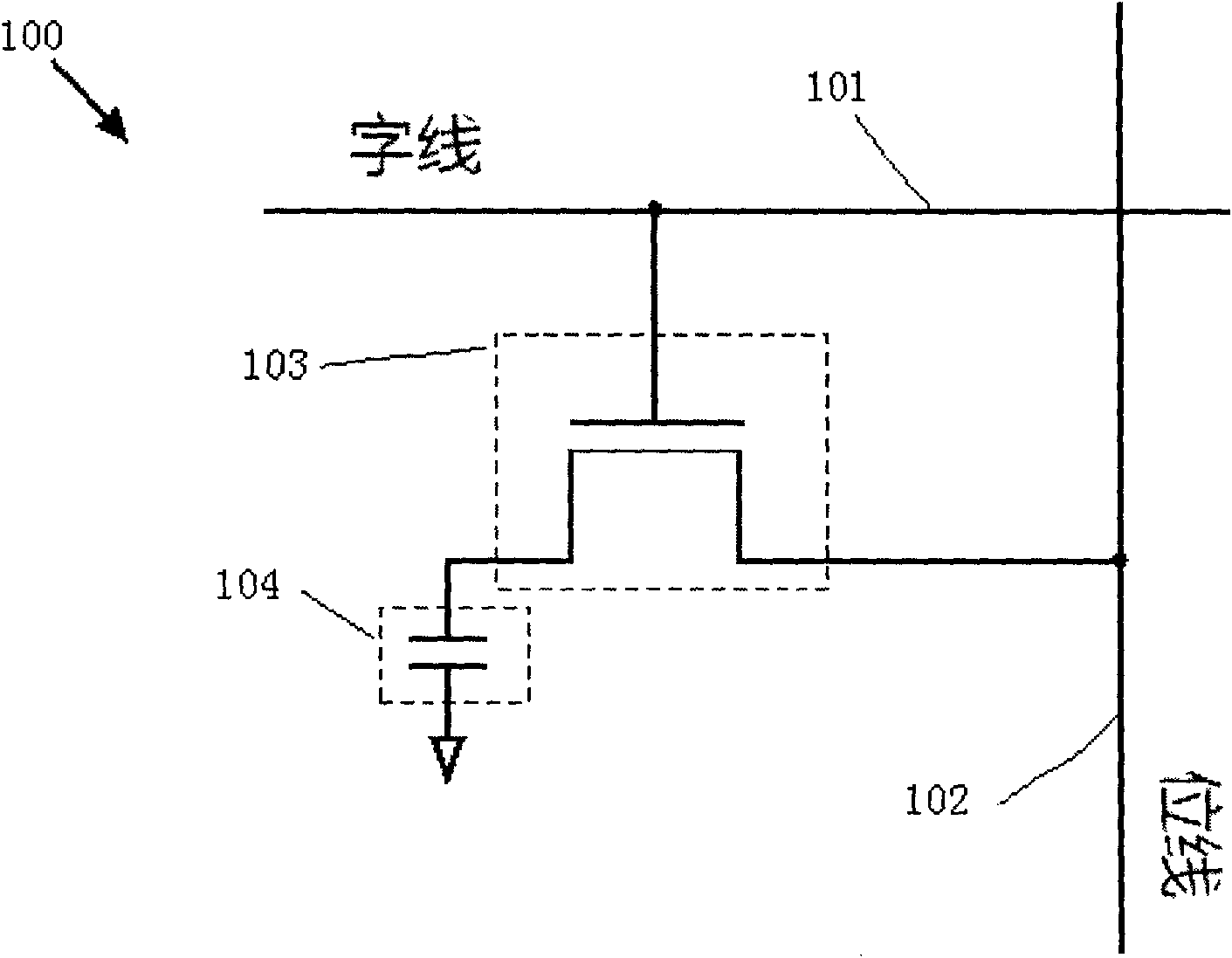

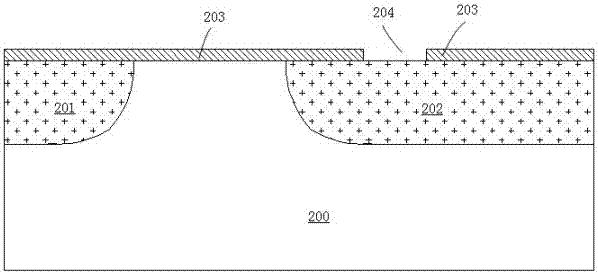

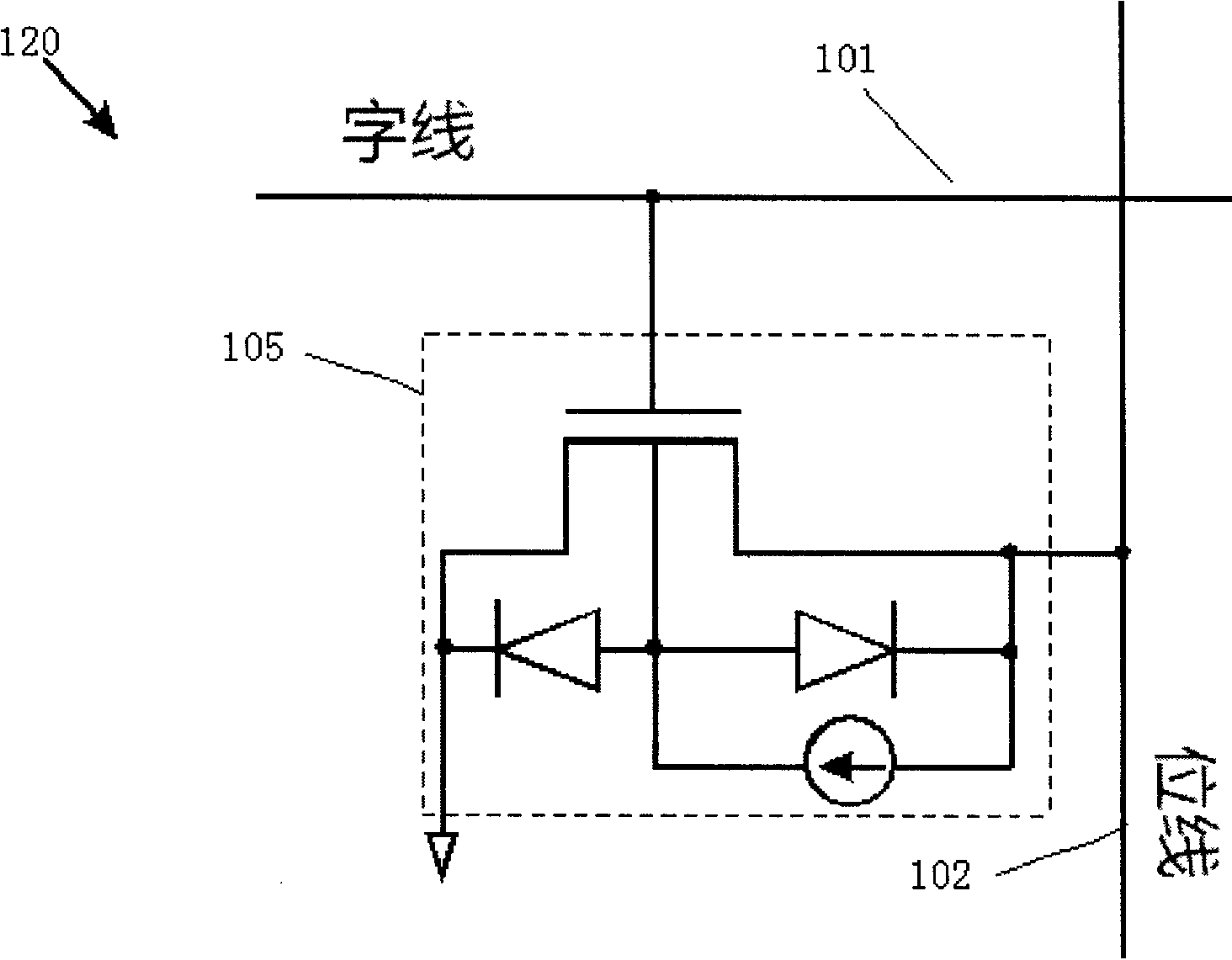

Semiconductor memory device and manufacturing method thereof

ActiveCN102169882AImprove compatibilityProcess stabilitySolid-state devicesSemiconductor/solid-state device manufacturingPlanar channelEngineering

The invention discloses a semiconductor memory device, which comprises a source, a drain, a floating gate region, a control gate, a planar channel region and a gate controlled diode, wherein the gate controlled diode is used for connecting the floating gate region and the drain; and in the semiconductor memory device, the floating gate region is used for memorizing information, the gate controlled diode is used for connecting a floating gate and a substrate, and the floating gate is charged or discharged by the gate controlled diode. The semiconductor memory device is manufactured by using a self-alignment process, and the process is simple and stable; and in the invention, manufacturing of a logic circuit and a flash memory device is compatible by using a planar channel structure.

Owner:SUZHOU ORIENTAL SEMICONDUCTOR CO LTD

Twisted dual-substrate orientation (DSO) substrates

A semiconductor process and apparatus provide a dual or hybrid substrate by forming a second semiconductor layer (214) that is isolated from, and crystallographically rotated with respect to, an underlying first semiconductor layer (212) by a buried insulator layer (213); forming an STI region (218) in the second semiconductor layer (214) and buried insulator layer (213); exposing the first semiconductor layer (212) in a first area (219) of a STI region (218); epitaxially growing a first epitaxial semiconductor layer (220) from the exposed first semiconductor layer (212); and selectively etching the first epitaxial semiconductor layer (220) and the second semiconductor layer (214) to form CMOS FinFET channel regions (e.g., 223) and planar channel regions (e.g., 224) from the first epitaxial semiconductor layer (220) and the second semiconductor layer (214).

Owner:TAIWAN SEMICON MFG CO LTD

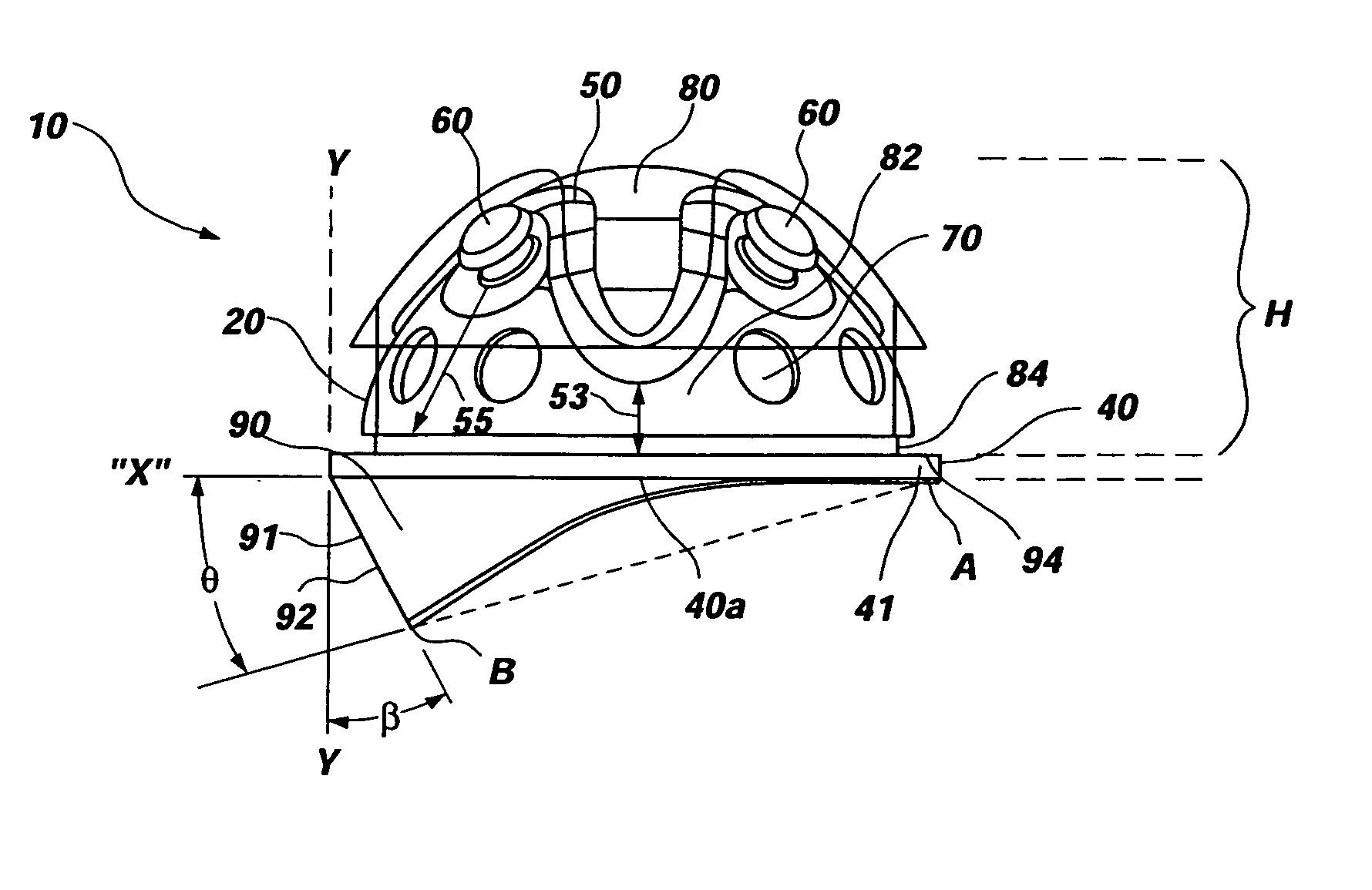

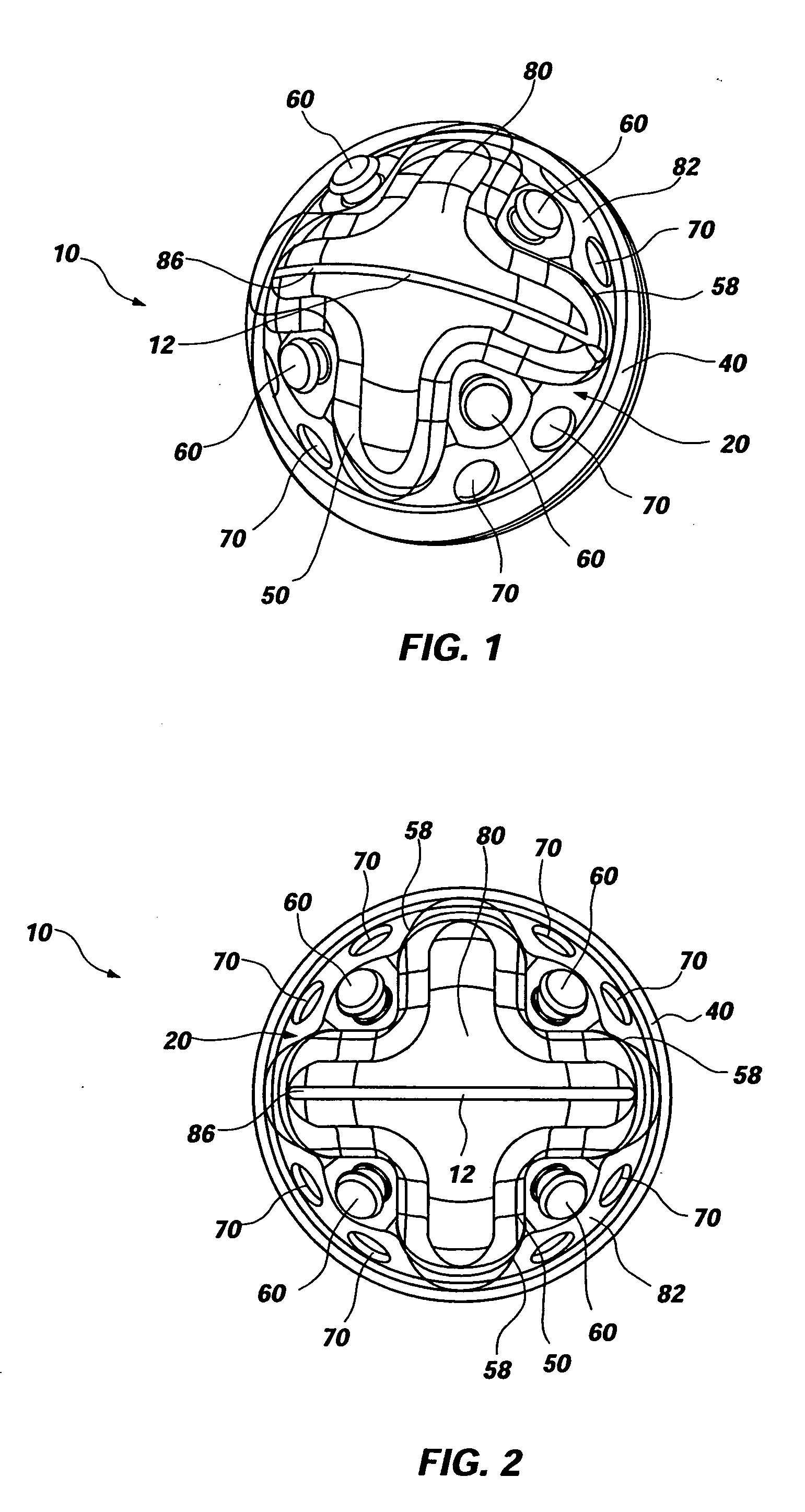

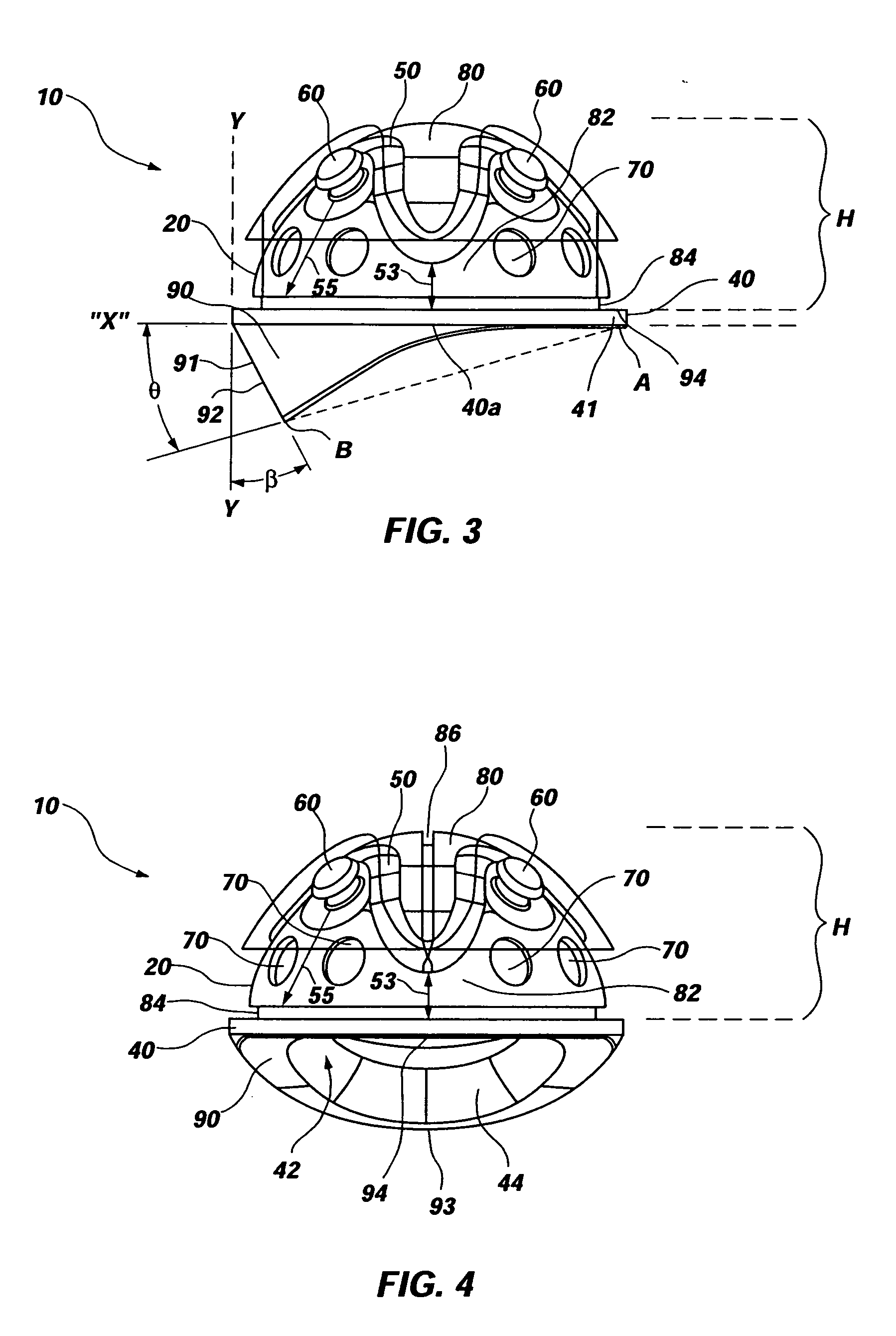

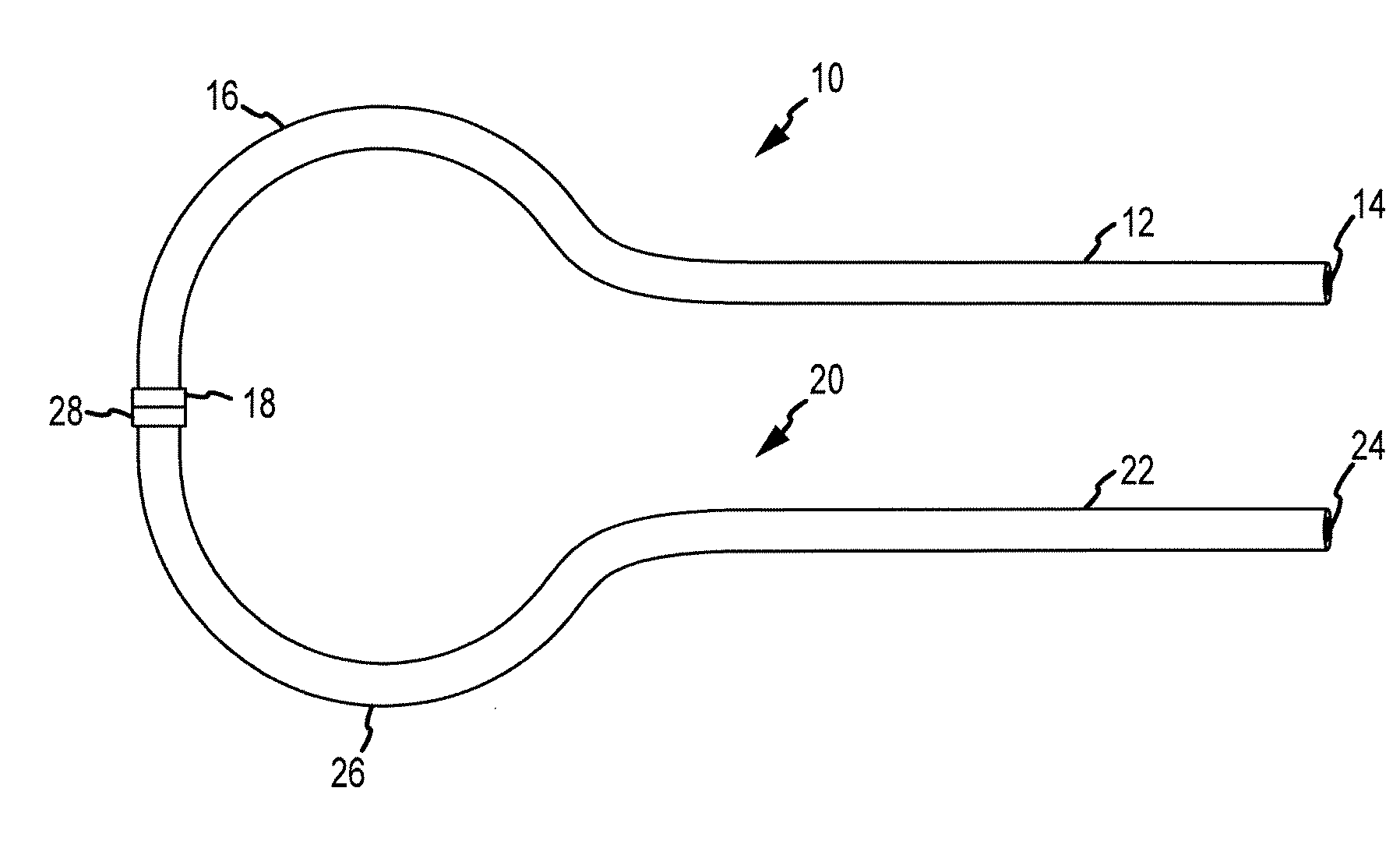

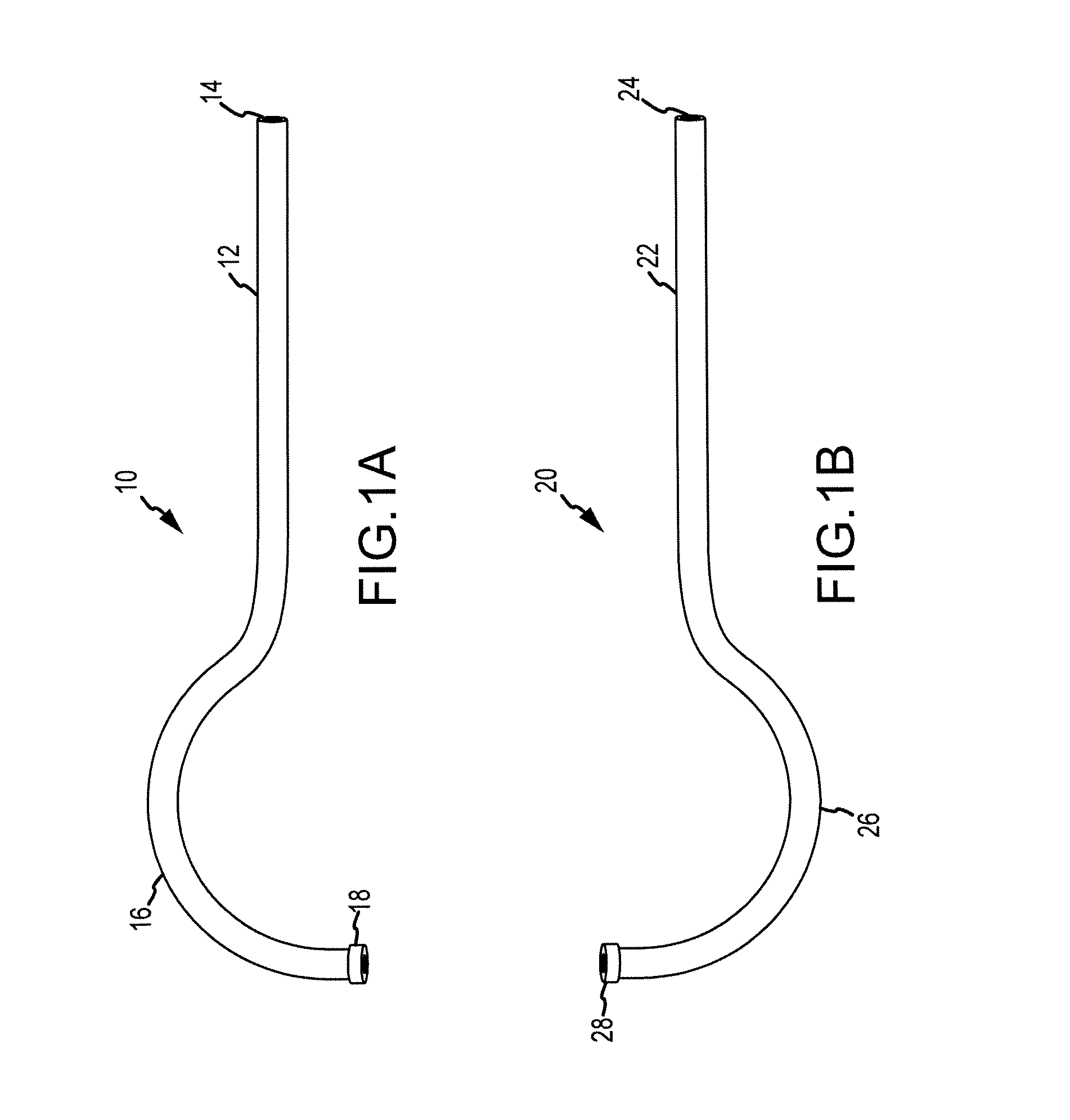

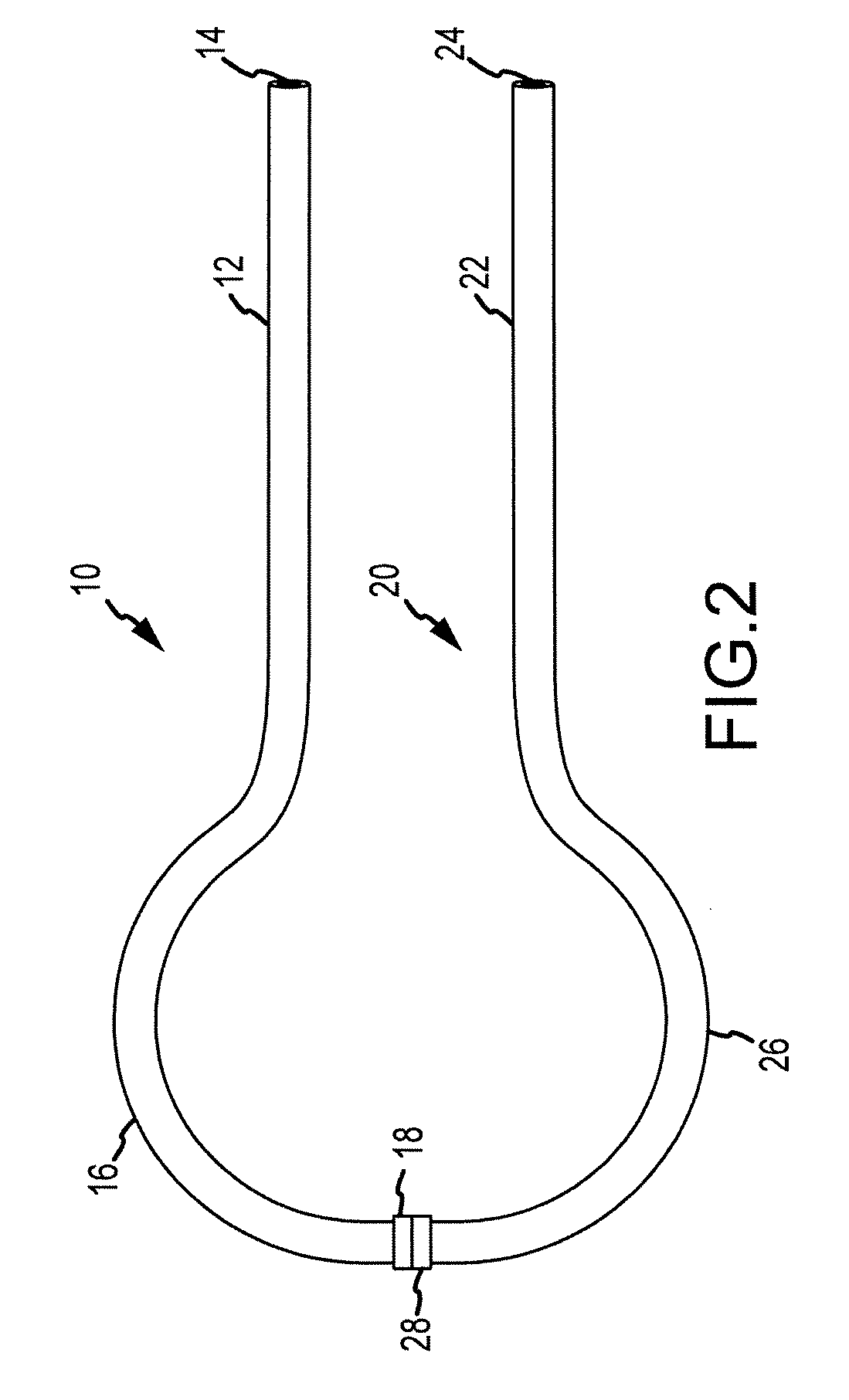

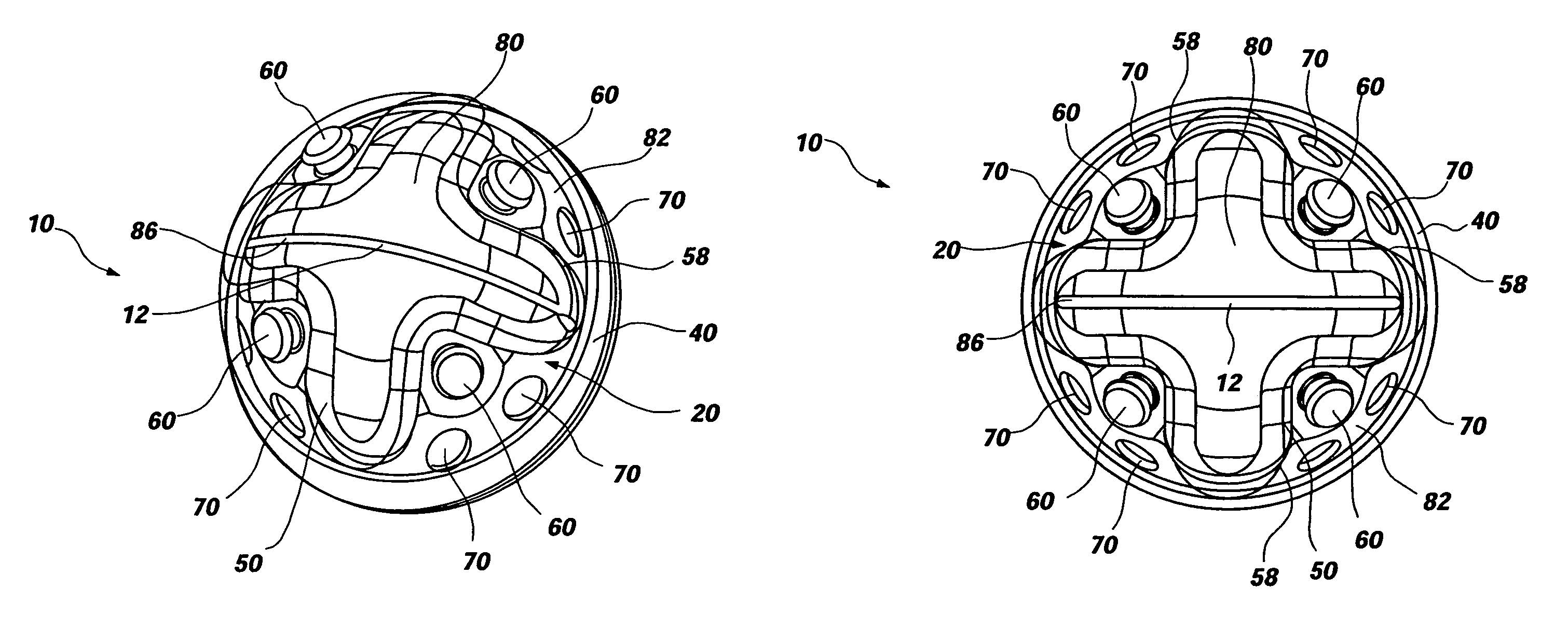

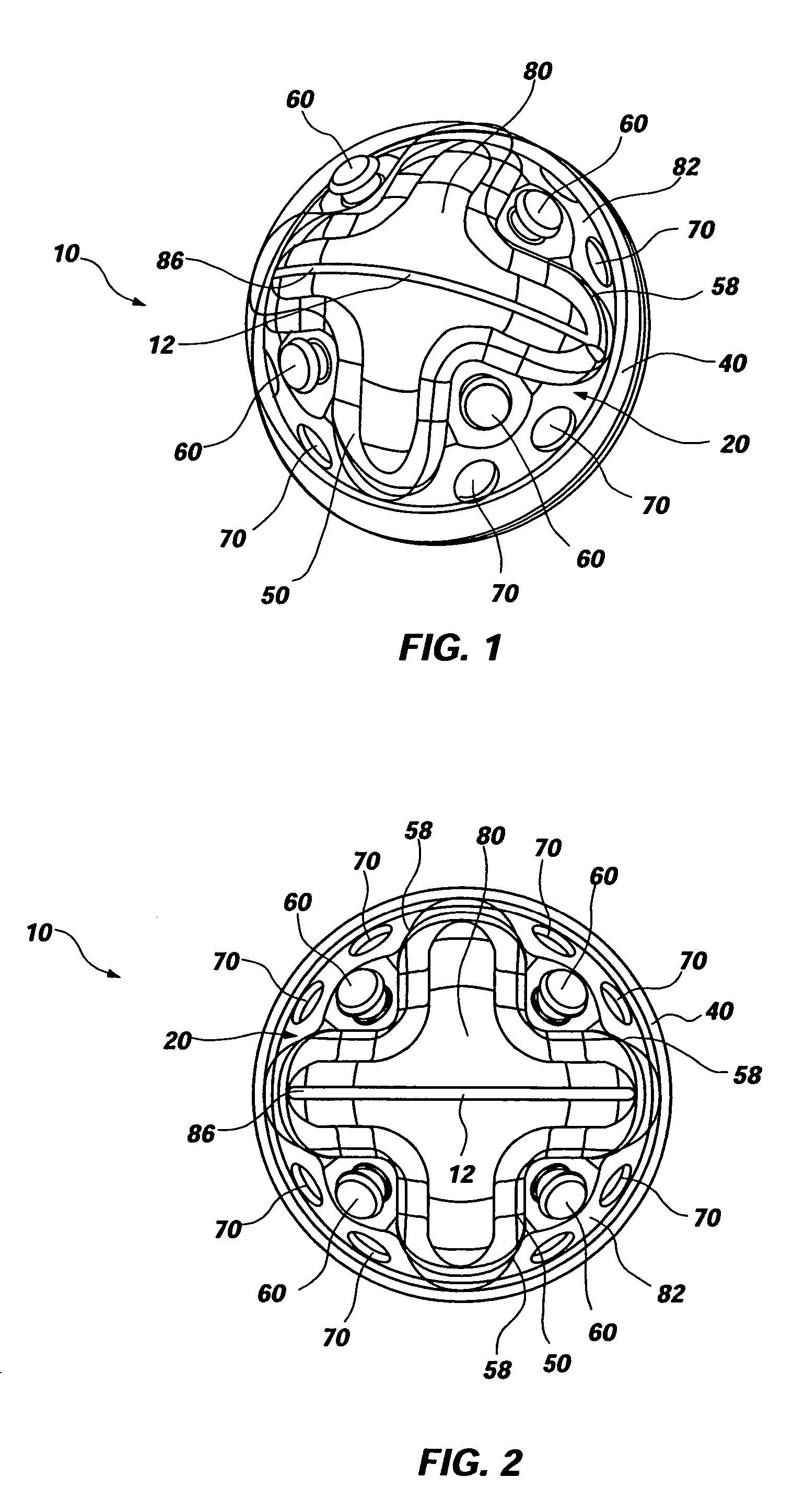

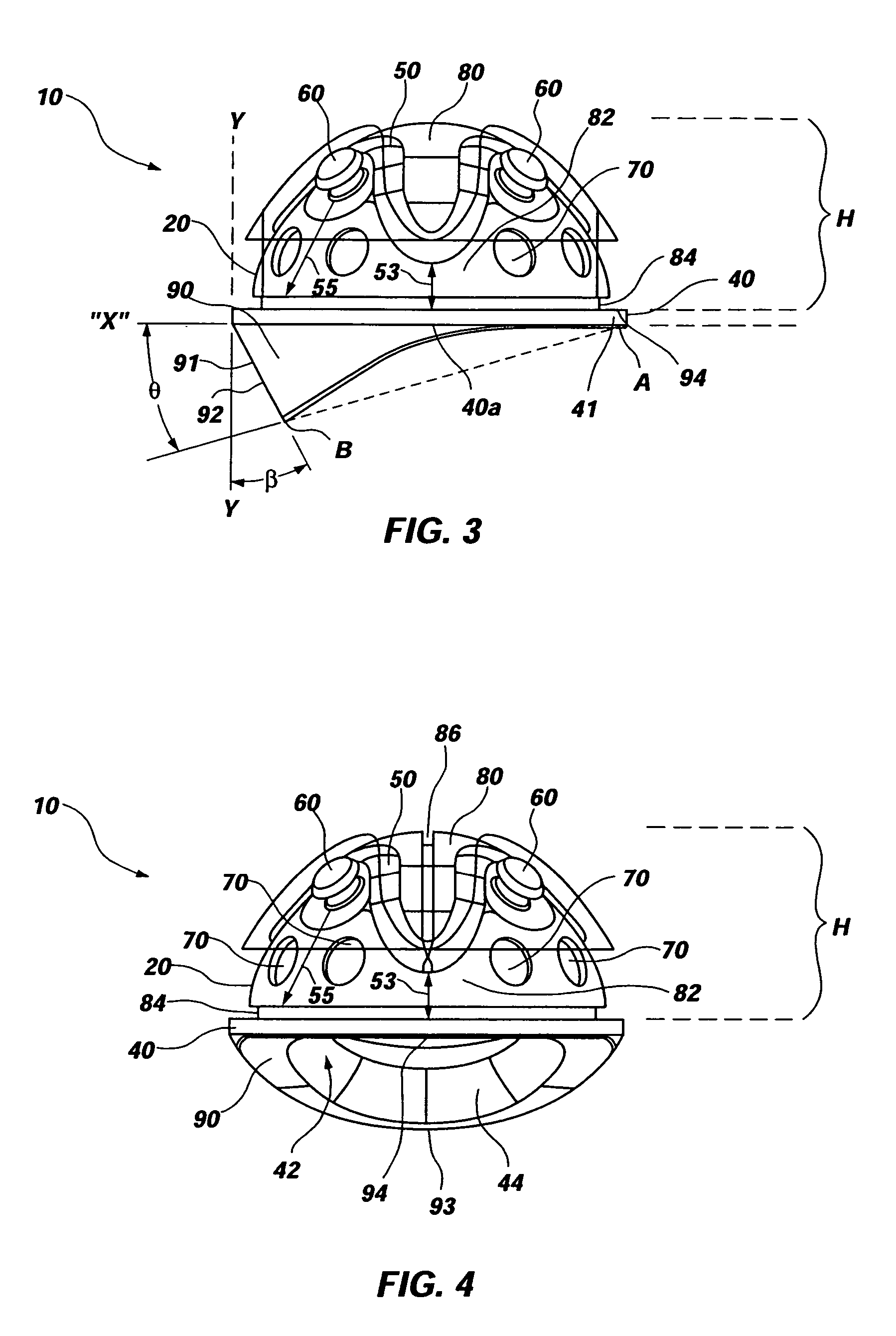

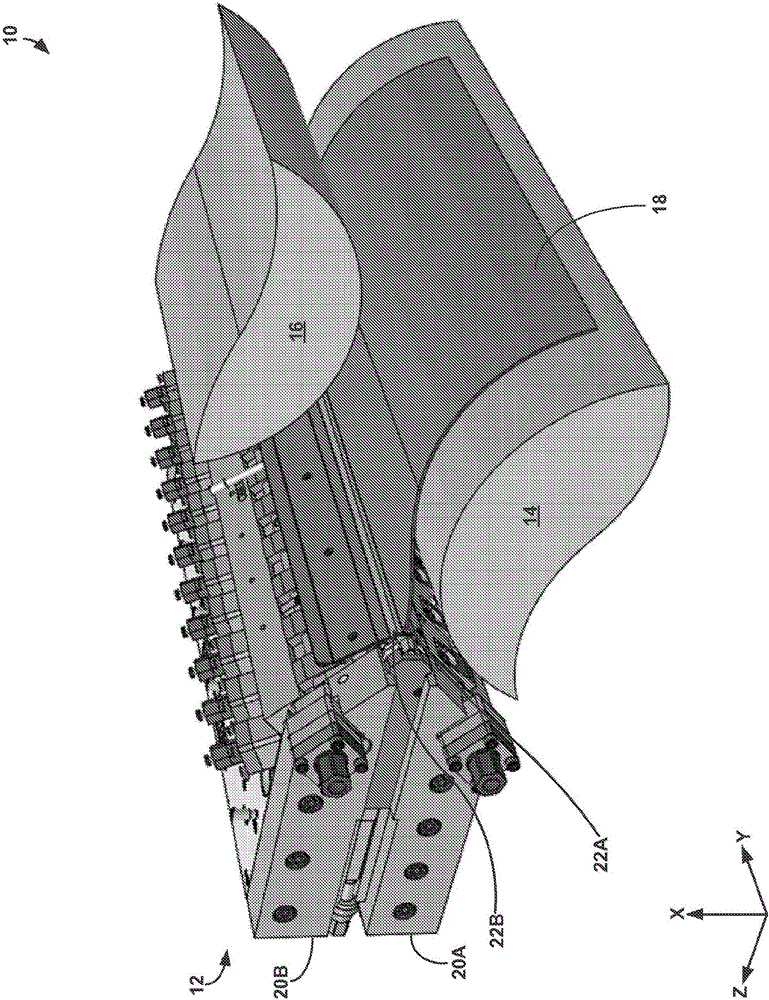

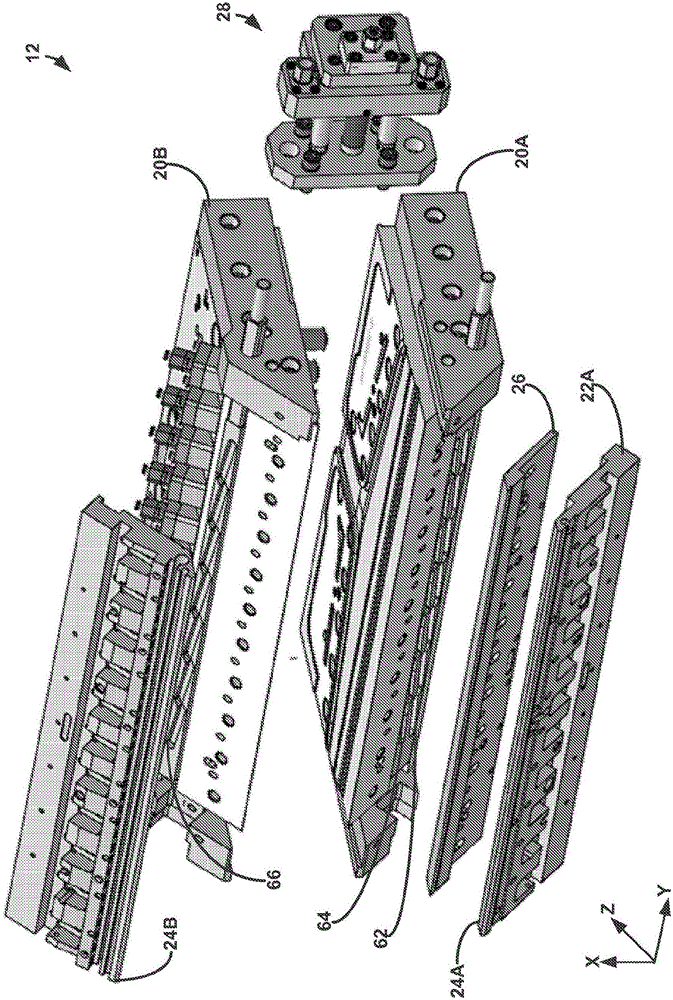

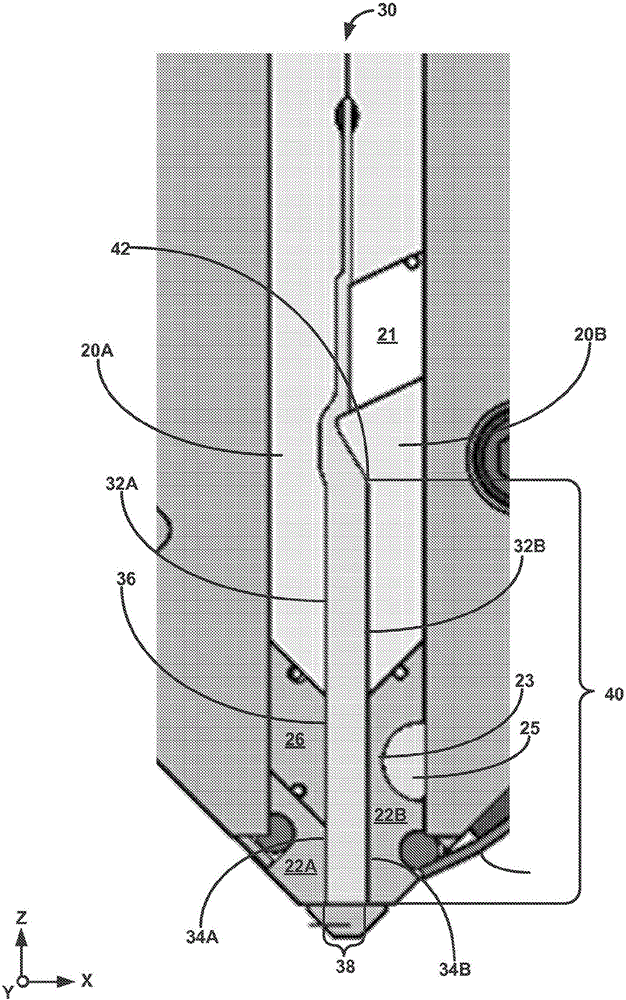

Polymeric acetabular cup

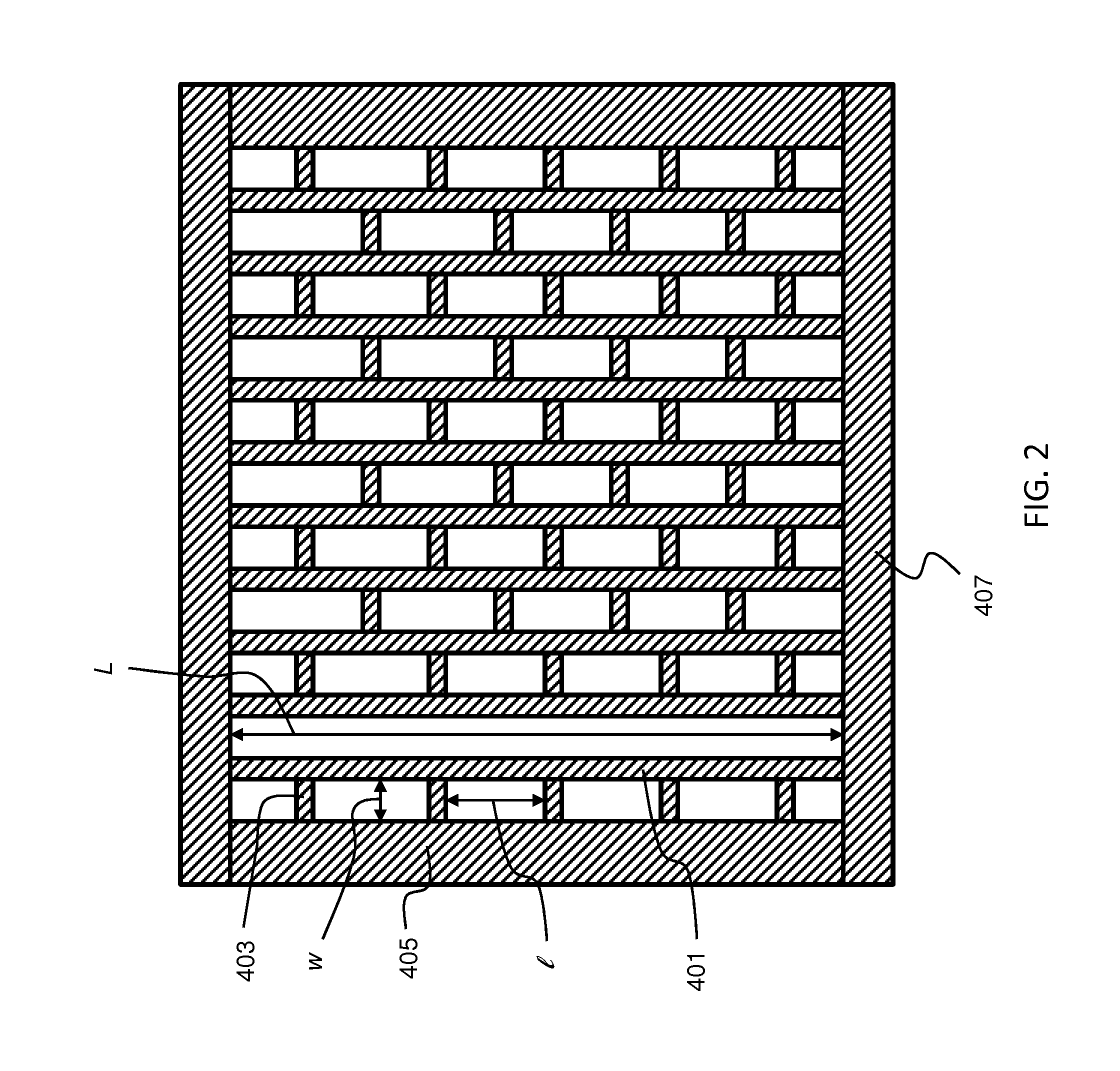

An orthopedic prosthesis comprising a polymeric cup member for use in a ball and socket joint is disclosed. The cup member may include several advantageous features such as a multi-directional and multi-planar channel having an undercut area that provides a mechanical lock between the cup member and a fixation material for enhanced fixation. The cup member may further comprise a plurality of spacers for ensuring an even mantle of fixation material between the cup member and the bone, a series of divots for enhancing fixation, a locating feature that permits a physician to visualize and locate the cup member in the socket of the patient's bone on appropriate medical equipment, and a lead-in chamfer located between a terminal edge and an interior surface of the cup member. Further, the terminal edge of the cup member may comprise a planar rim or may alternatively comprise a hood located distally from said terminal edge.

Owner:ORTHO DEV CORP

Semiconductor memory device and manufacturing method thereof

ActiveCN102376711AReduce maskReduce the number of processesSolid-state devicesSemiconductor/solid-state device manufacturingPlanar channelP–n junction

The invention discloses a semiconductor memory device, which comprises at least one semiconductor substrate, a source electrode, a drain electrode, a floating gate area, two control gate electrodes and a gate control p-n junction diode. The gate control p-n junction diode is used for connecting the floating gate area and the substrate. In the semiconductor memory device, the floating gate area is used for storing information, and charging and discharging the floating gate area through the gate control p-n junction diode is realized. Furthermore, the invention also discloses a manufacturing method of the semiconductor memory device, a self-aligning process is adopted for manufacturing, and the process is simple and stable. Moreover, a planar channel structure is adopted, and the method is compatible with manufacturing of logic devices and flash memory devices.

Owner:SUZHOU ORIENTAL SEMICONDUCTOR CO LTD

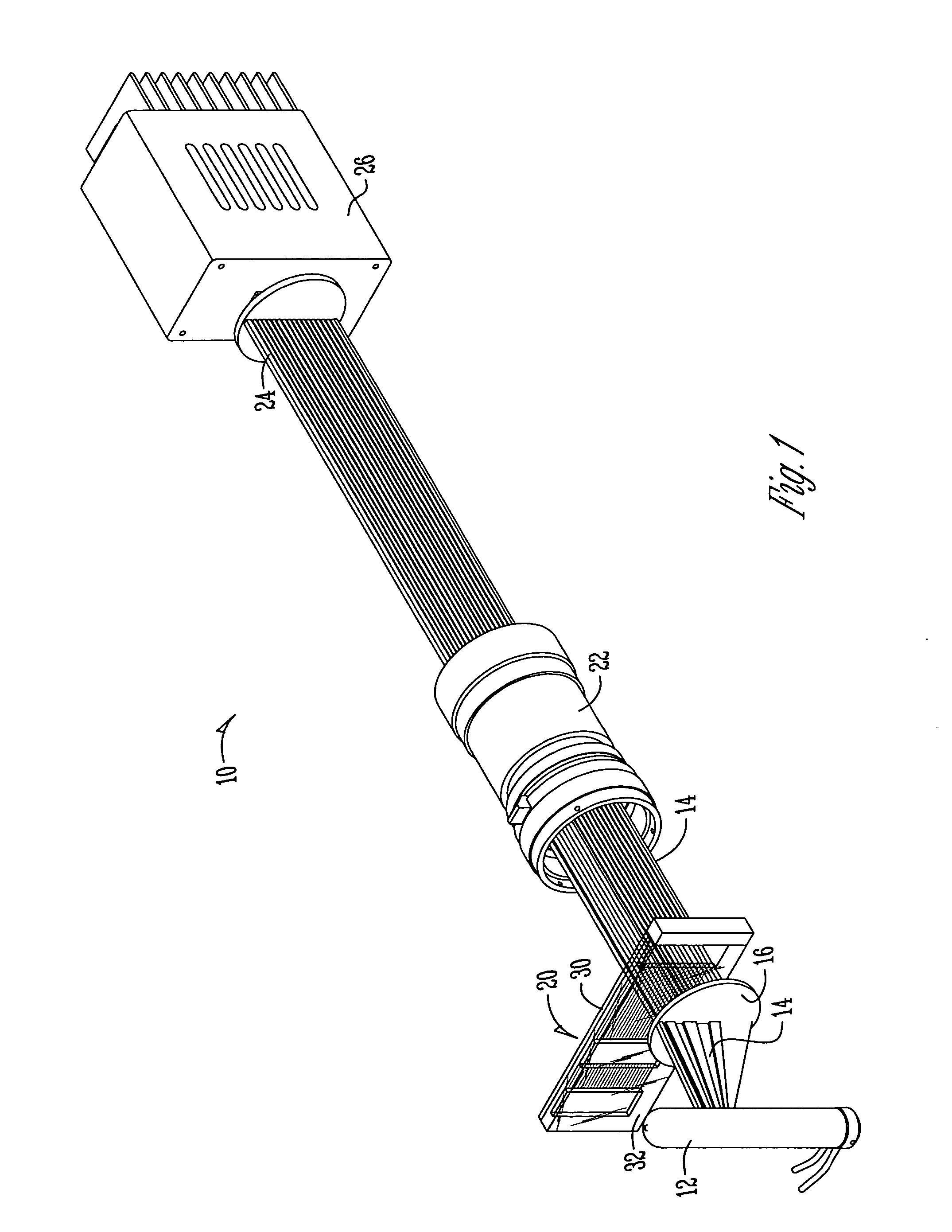

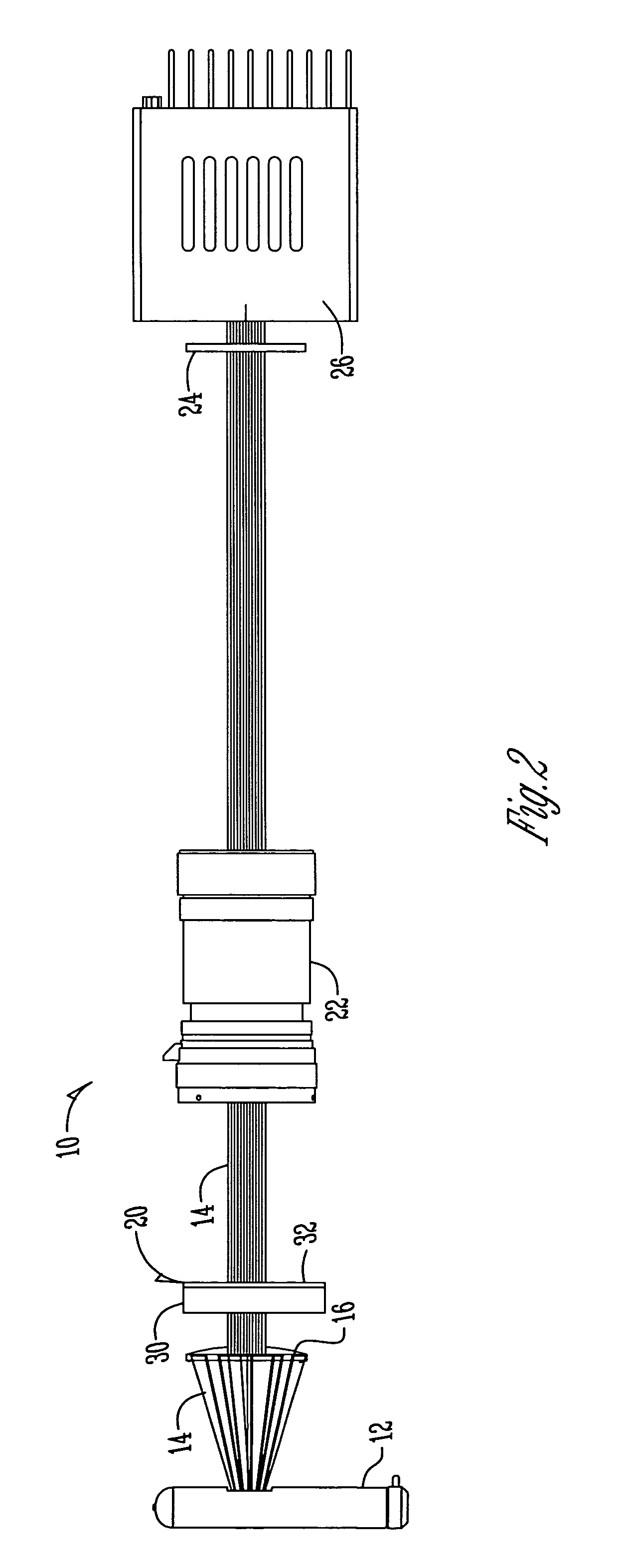

Cable clamping device and method of its use

InactiveUS20080208223A1Facilitates percutaneous near percutaneous applicationRisk minimizationInternal osteosythesisShoe lace fasteningsPlanar channelElectric cables

Owner:KRAEMER PAUL EDWARD

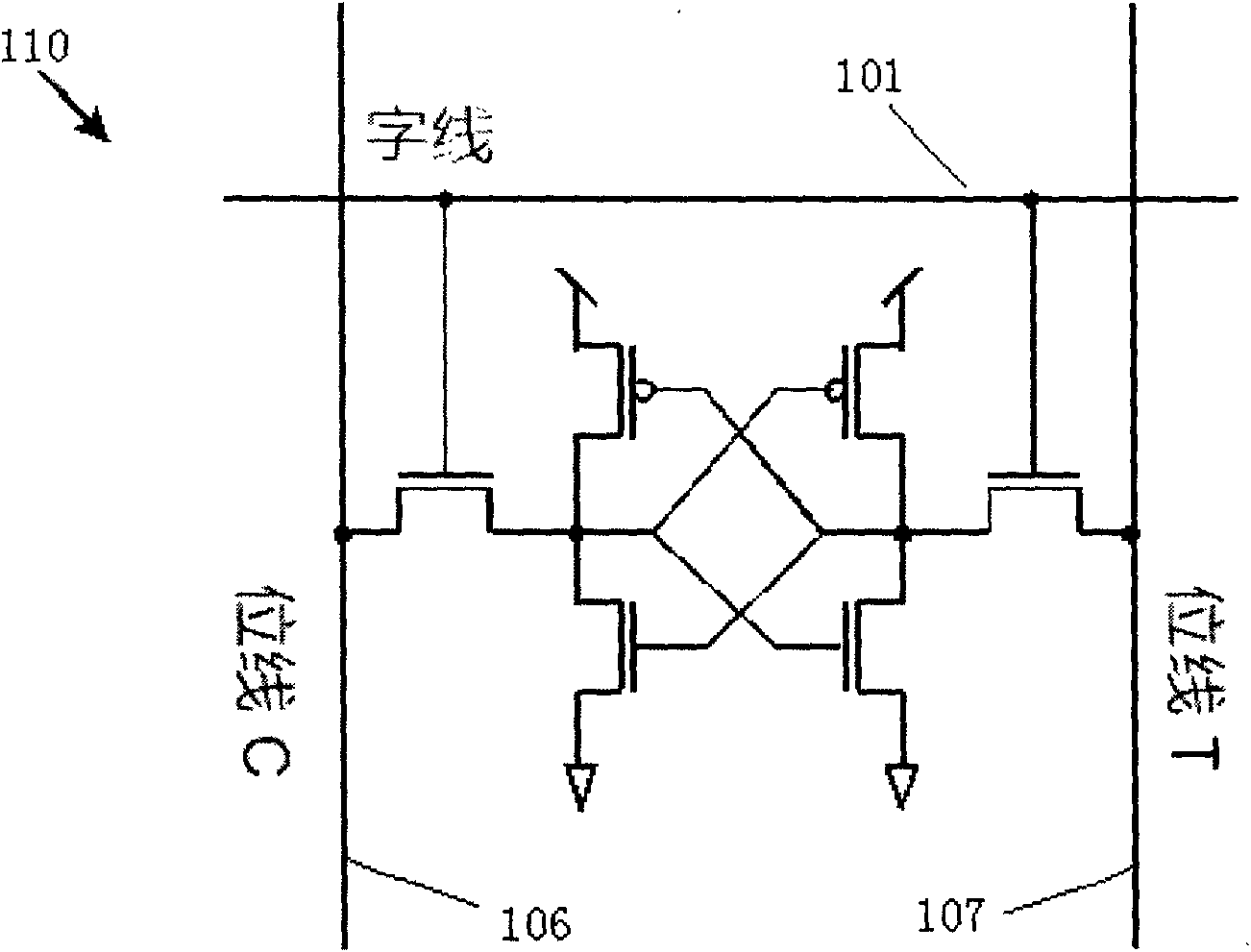

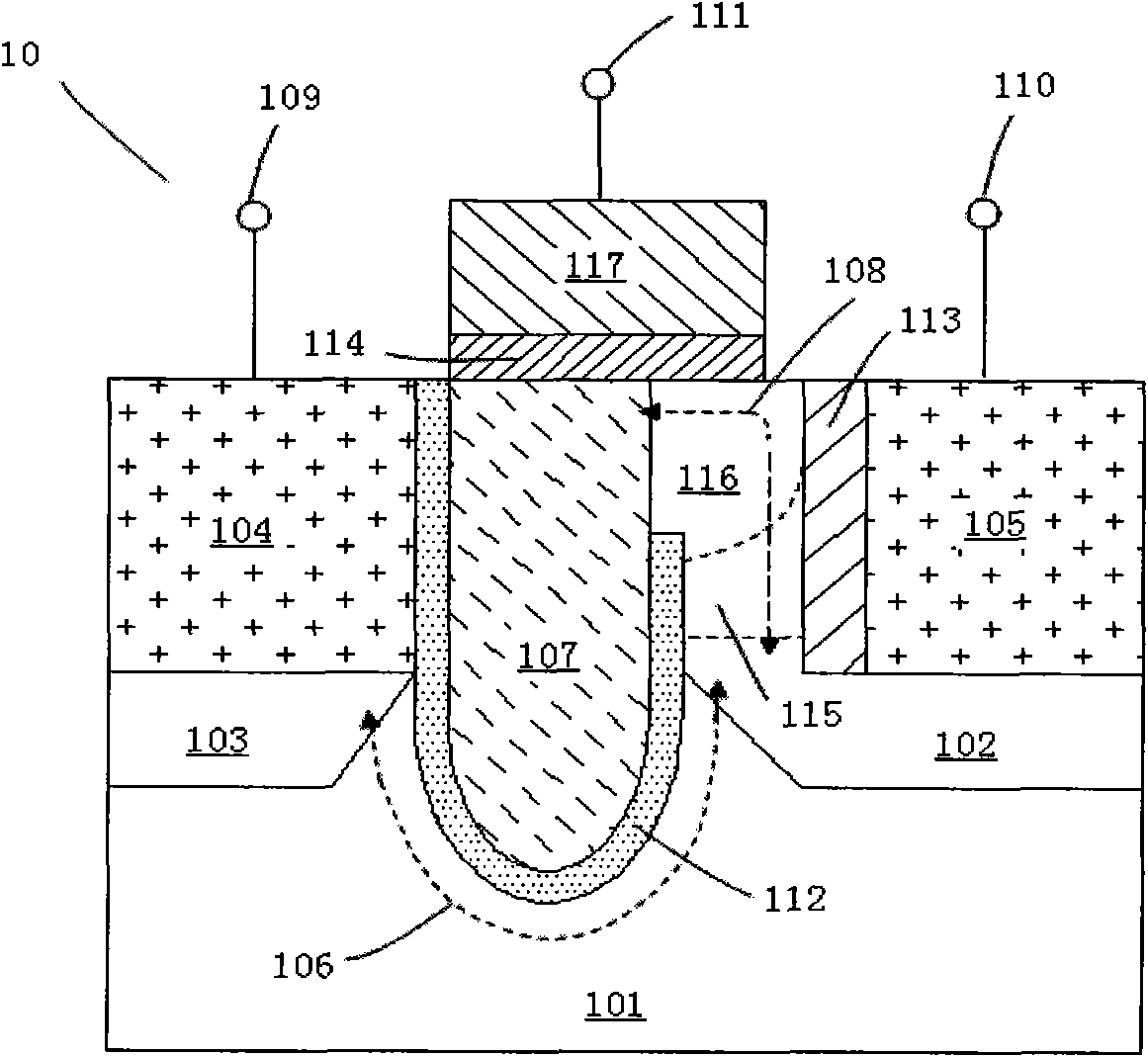

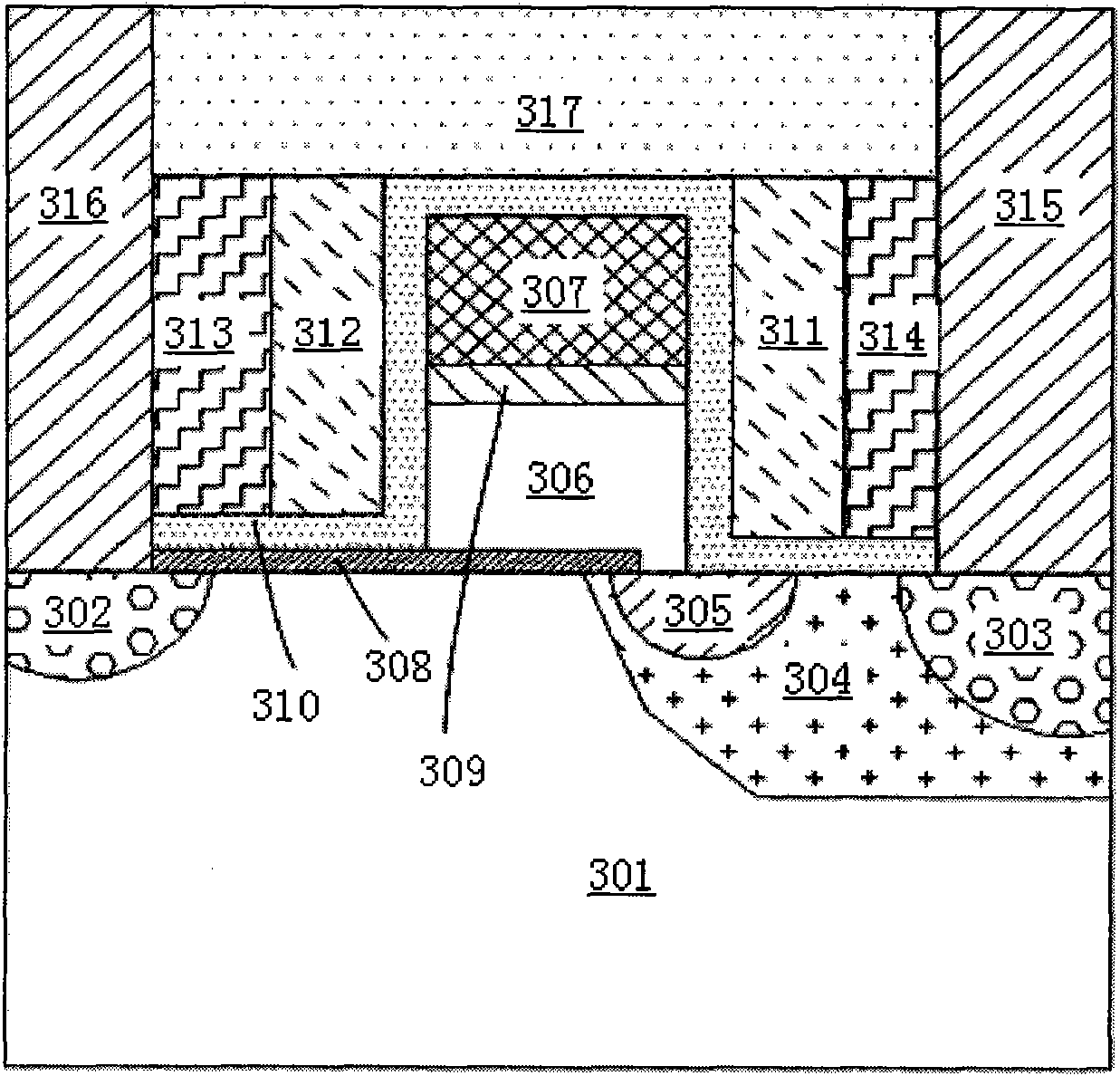

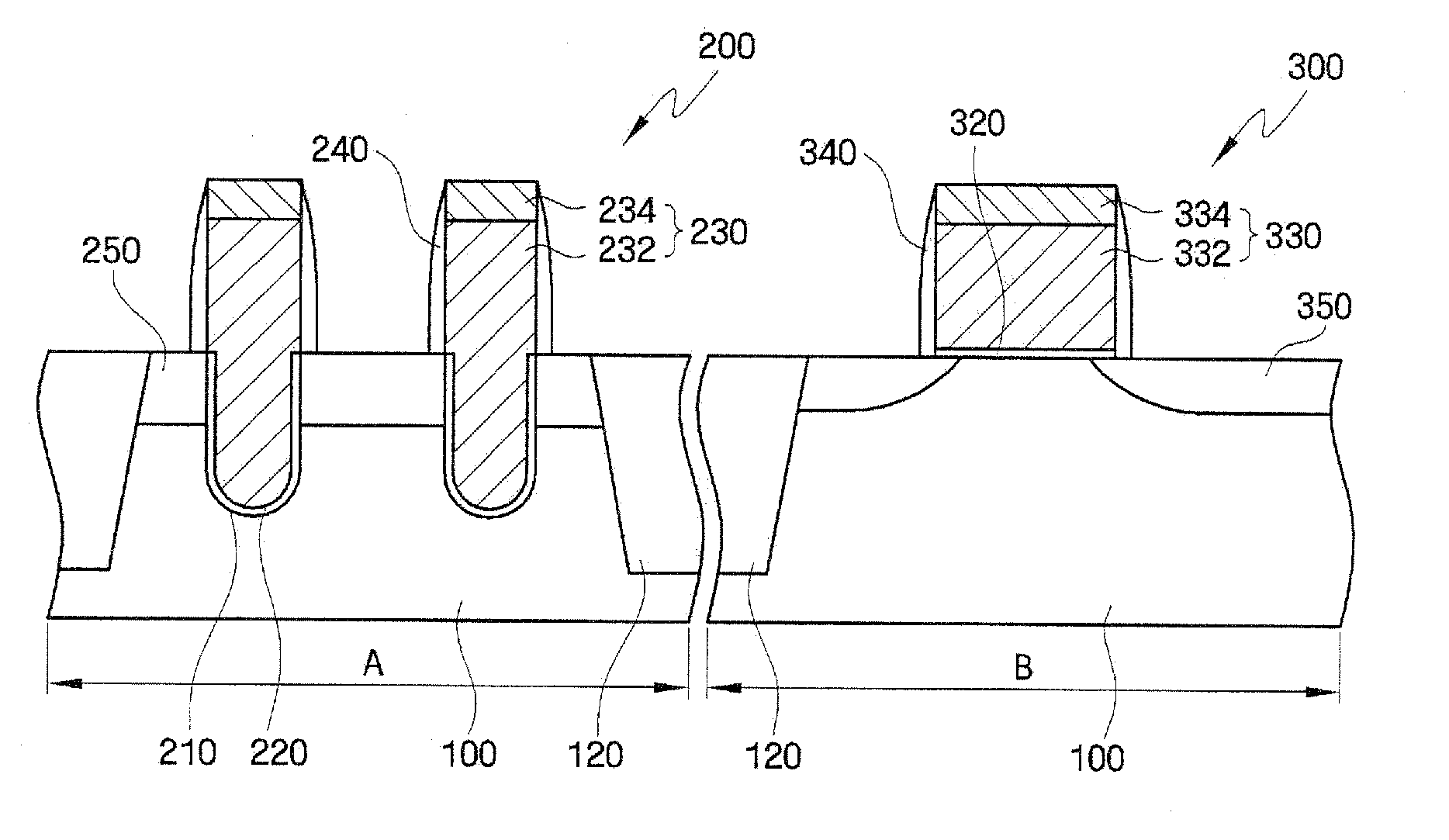

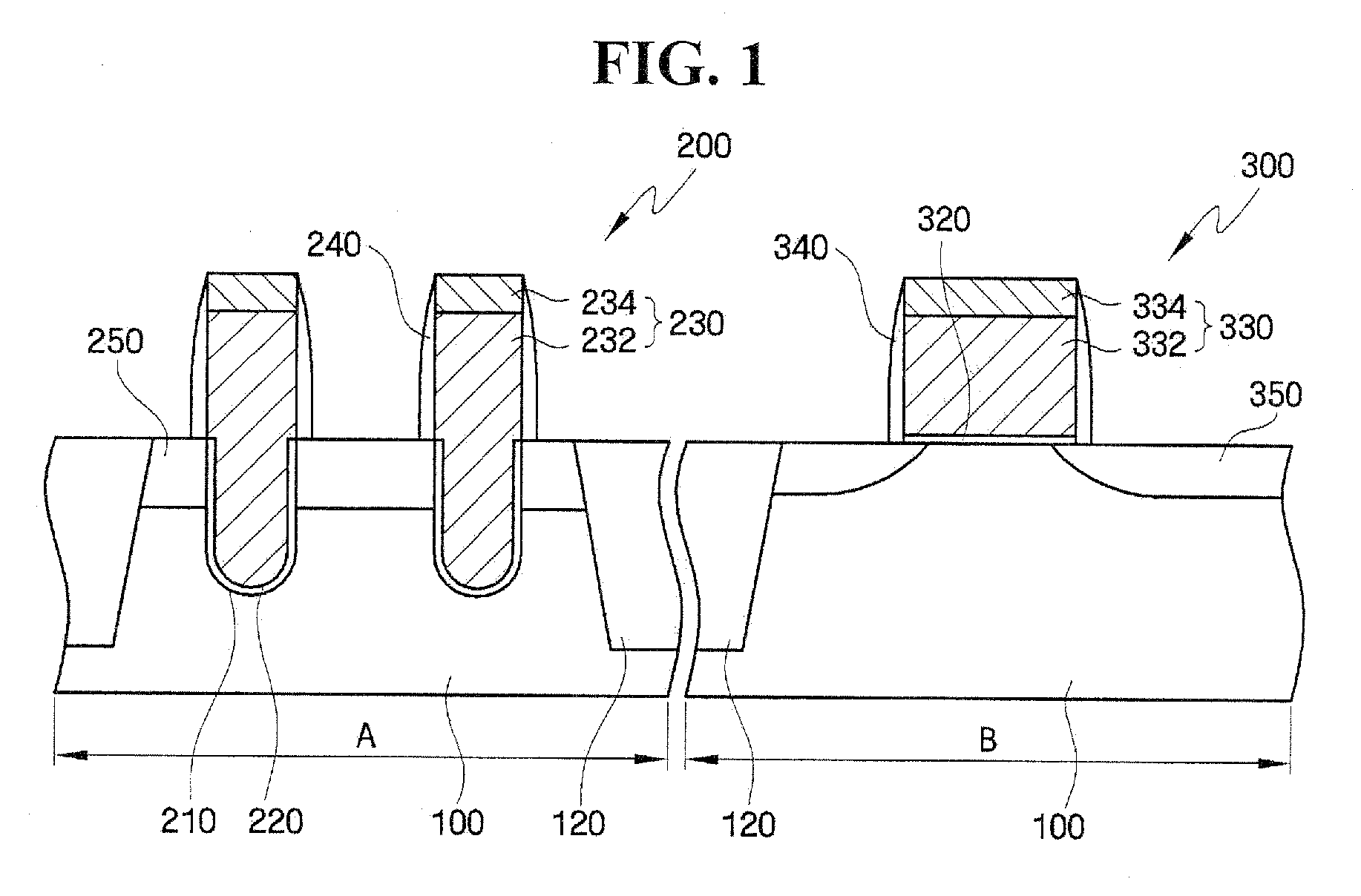

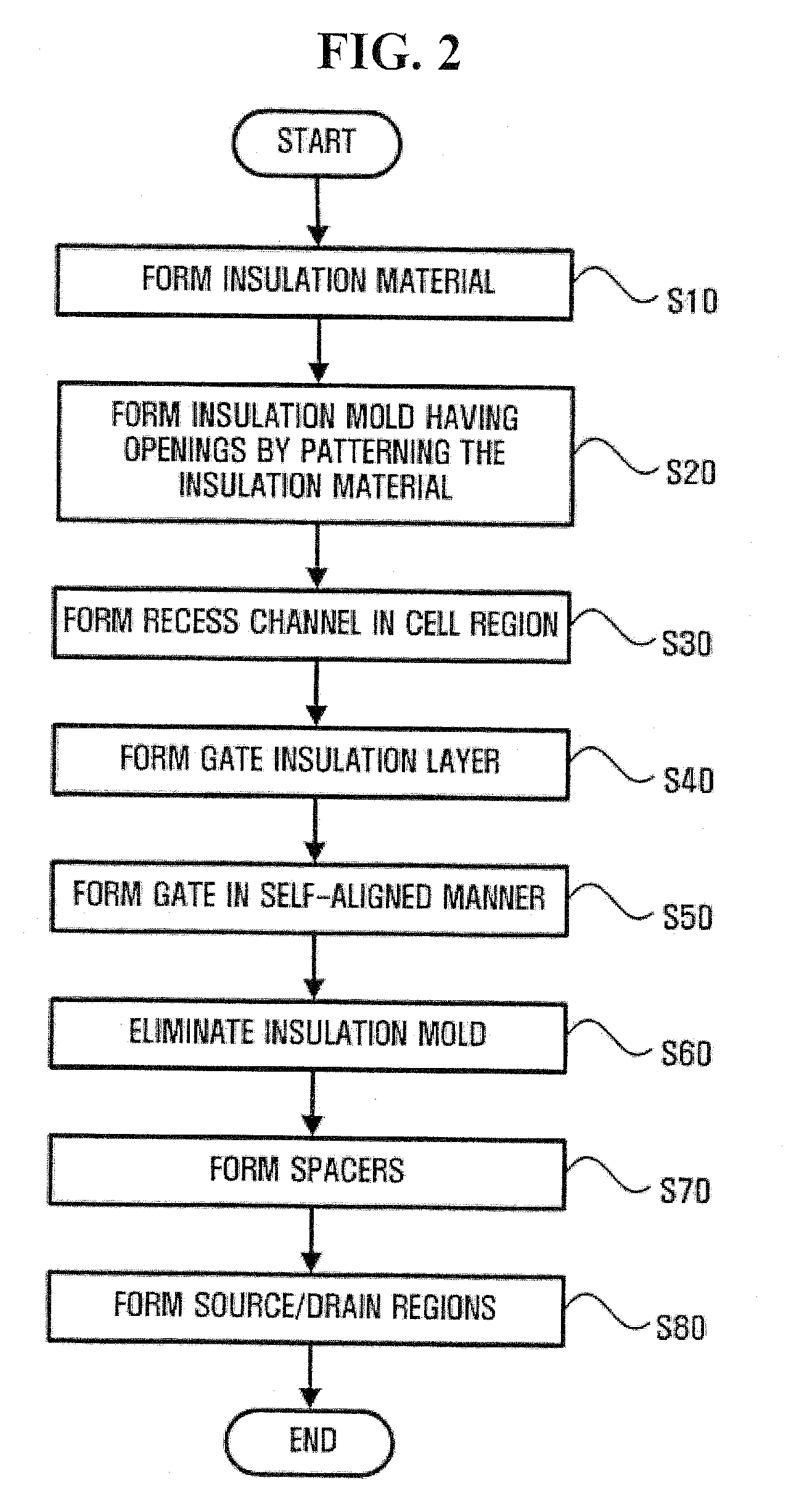

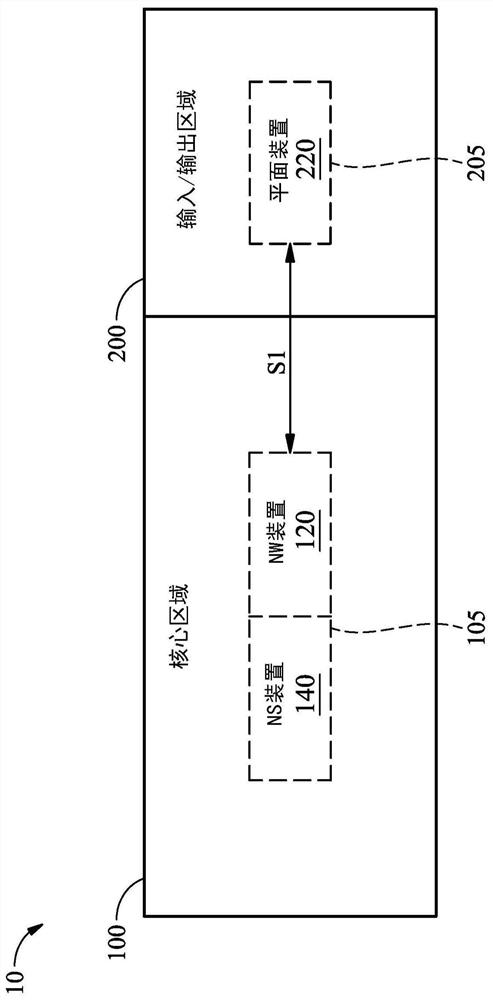

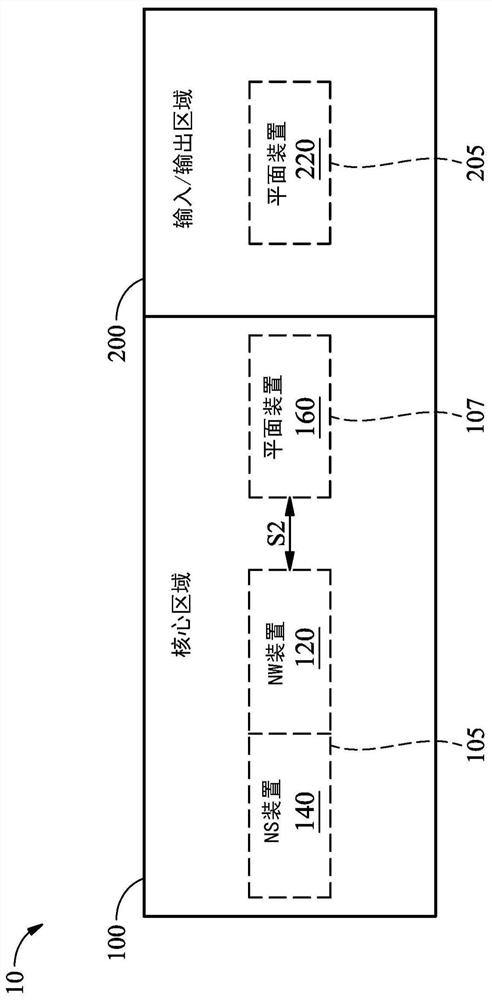

Semiconductor integrated circuit device and method of fabricating the same

InactiveUS20070029616A1Reduce power consumptionGuaranteed uptimeSolid-state devicesSemiconductor/solid-state device manufacturingInsulation layerPlanar channel

A semiconductor integrated circuit device and a method of fabricating the same are provided. An embodiment of the semiconductor integrated circuit device includes a substrate having a cell region and a peripheral circuit region. A recess channel transistor may be formed in the cell region and include a source / drain region, a recess channel formed between the source / drain region, a gate insulation layer formed in the recess channel, and a gate formed on the gate insulation layer in a self-aligned manner. A planar channel transistor may further be formed in the peripheral circuit region and include a source / drain region, a planar channel formed between the source / drain region, a gate insulation layer formed in the planar channel, and a gate formed on the gate insulation layer in a self-aligned manner.

Owner:SAMSUNG ELECTRONICS CO LTD

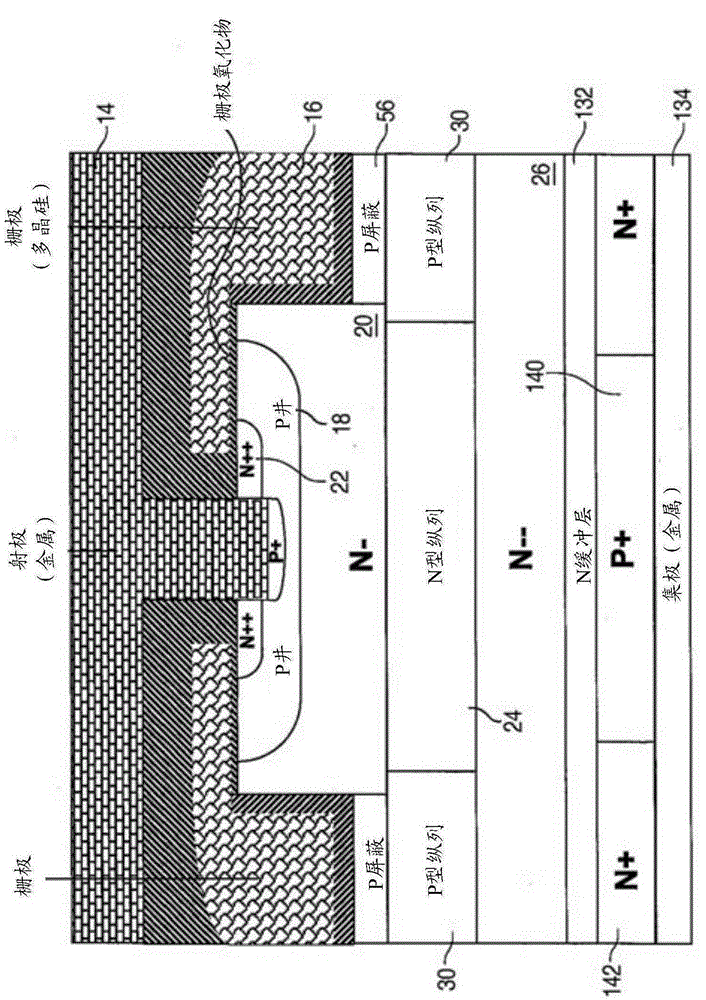

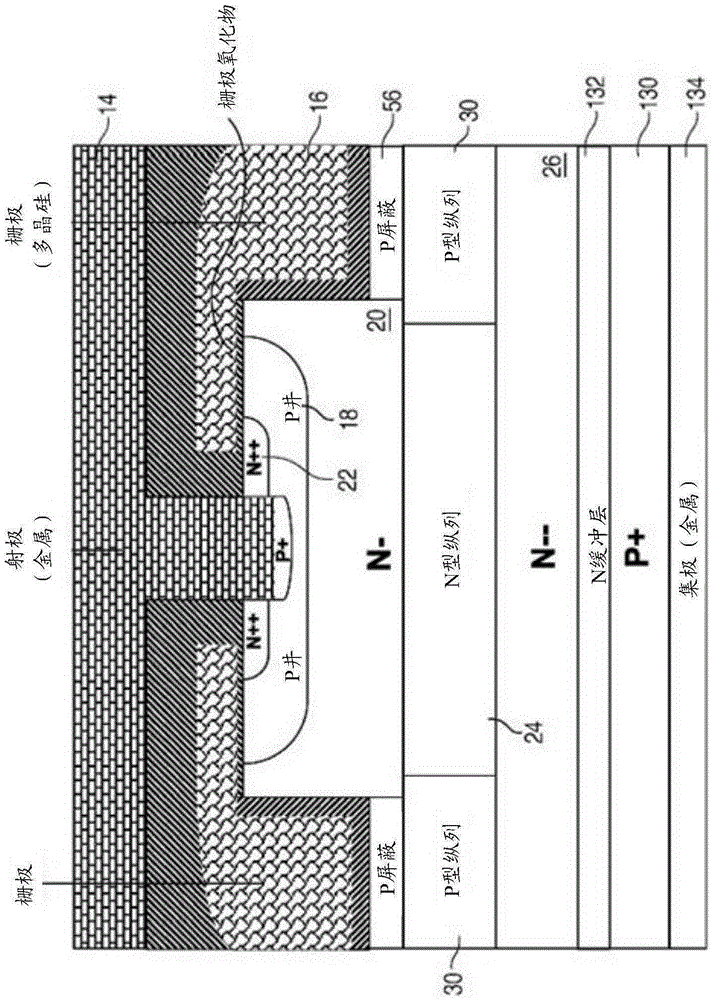

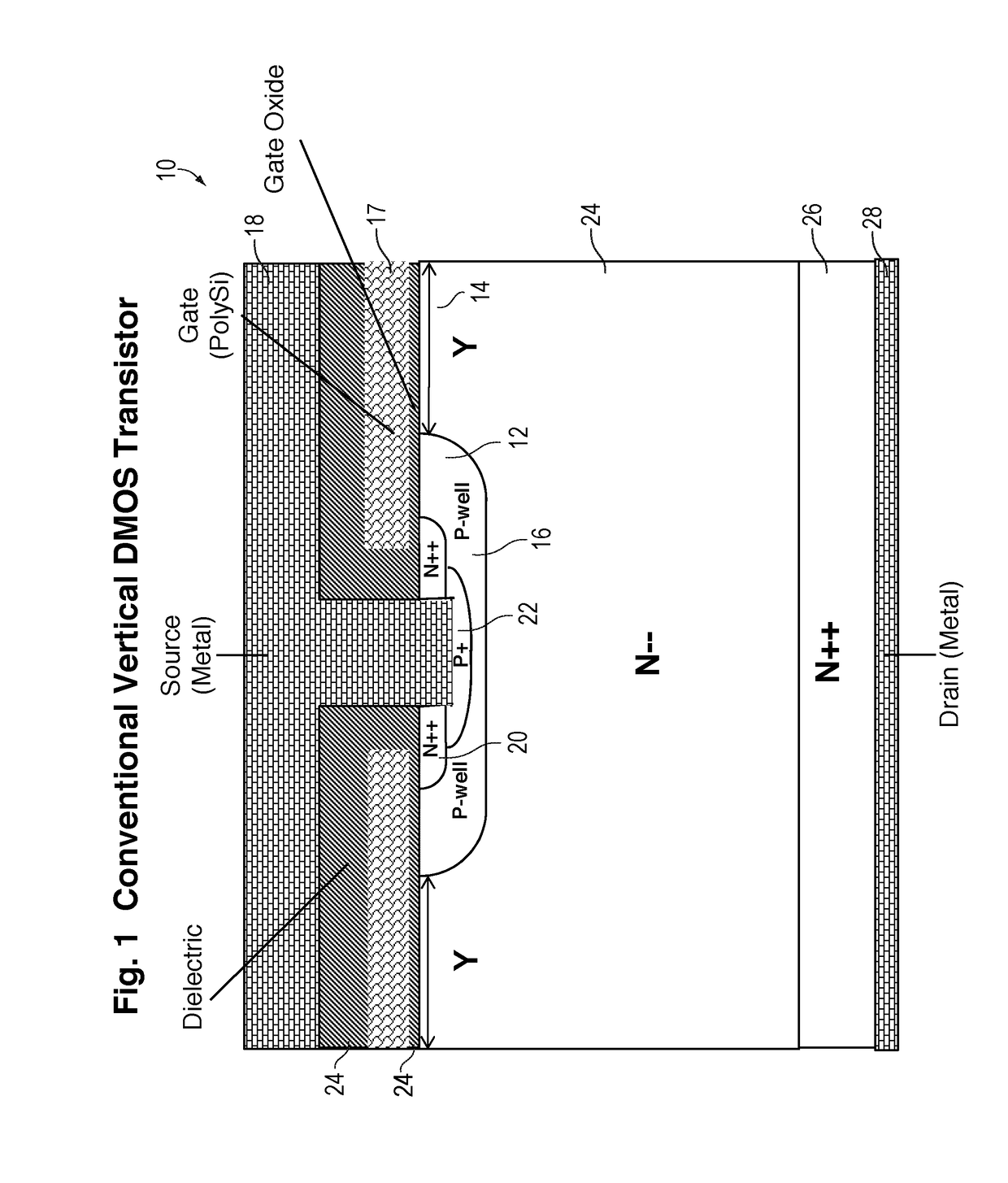

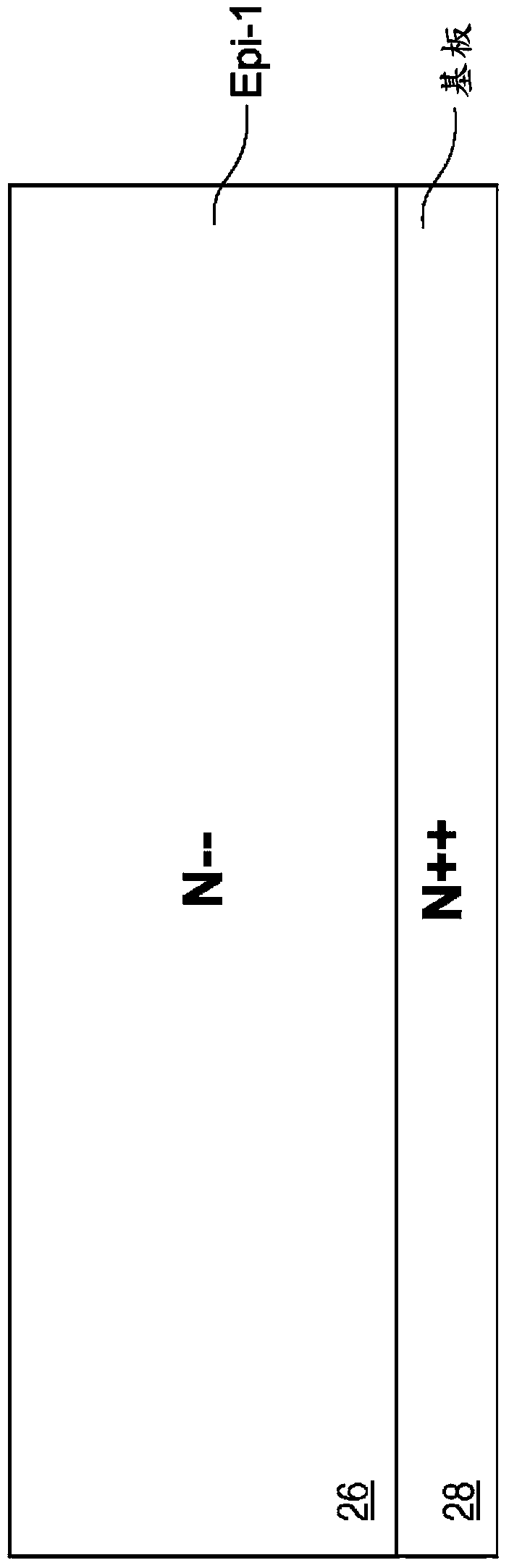

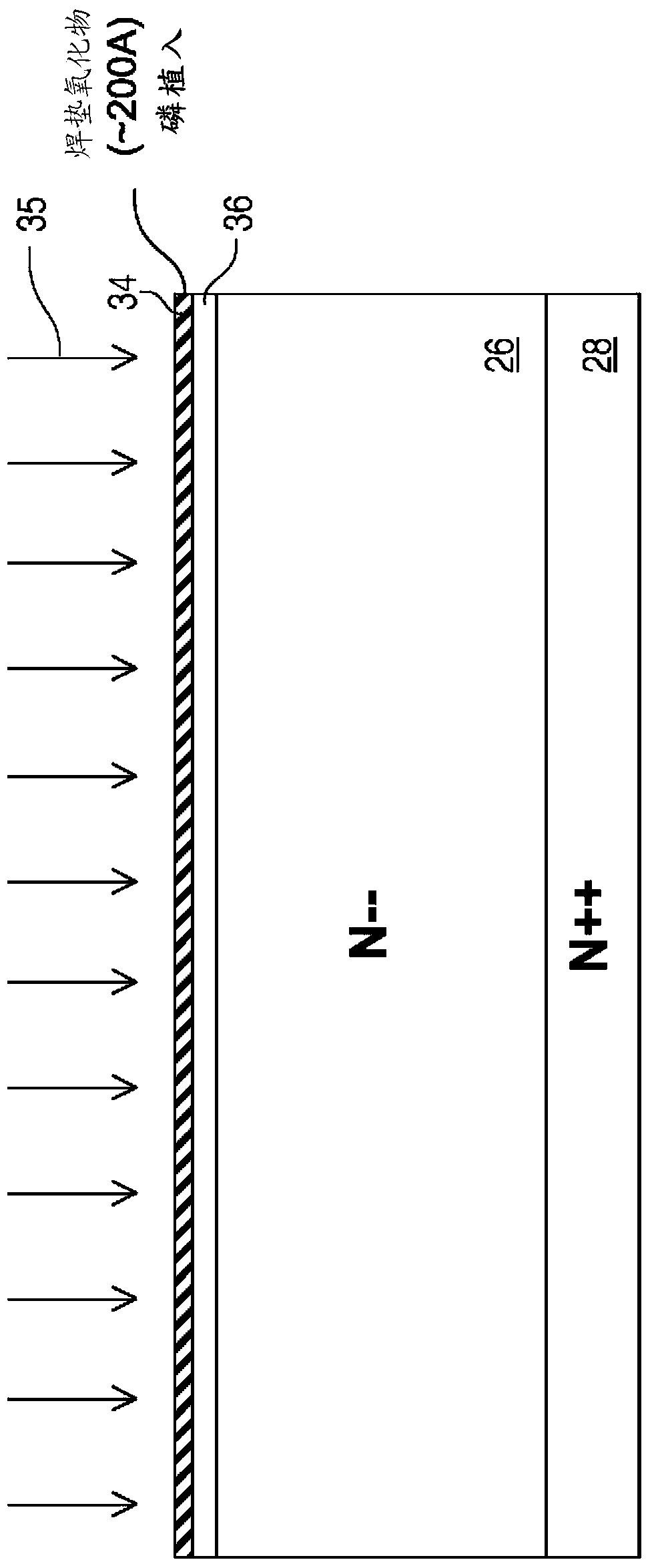

Vertical power mosfet including planar channel

ActiveCN105431946ALow costHigh dopingSemiconductor/solid-state device manufacturingSemiconductor devicesPlanar channelElectrode Contact

A power MOSFET cell includes an N+ silicon substrate having a drain electrode. A low dopant concentration N-type drift layer is grown over the substrate. Alternating N and P-type columns are formed over the drift layer with a higher dopant concentration. An N-type layer, having a higher dopant concentration than the drift region, is then formed and etched to have sidewalls. A P-well is formed in the N-type layer, and an N+ source region is formed in the P-well. A gate is formed over the P-well's lateral channel and next to the sidewalls as a vertical field plate. A source electrode contacts the P-well and source region. A positive gate voltage inverts the lateral channel and increases the conduction along the sidewalls. Current between the source and drain flows laterally and then vertically through the various N layers. On resistance is reduced and the breakdown voltage is increased.

Owner:无锡美偌科微电子有限公司

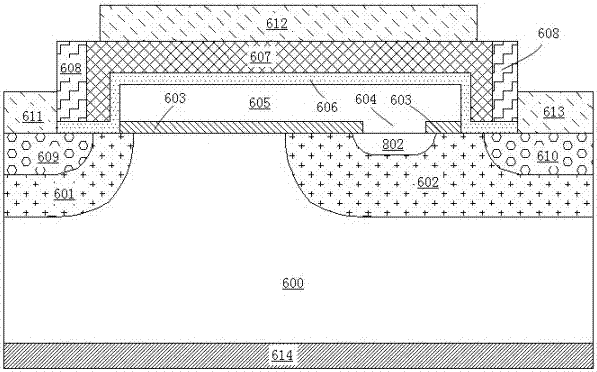

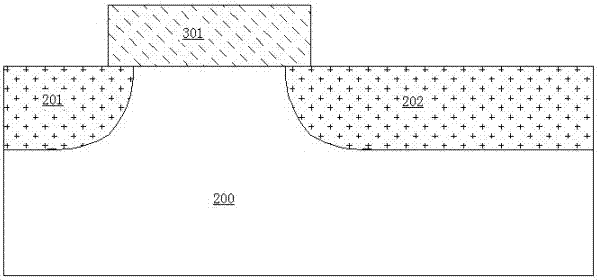

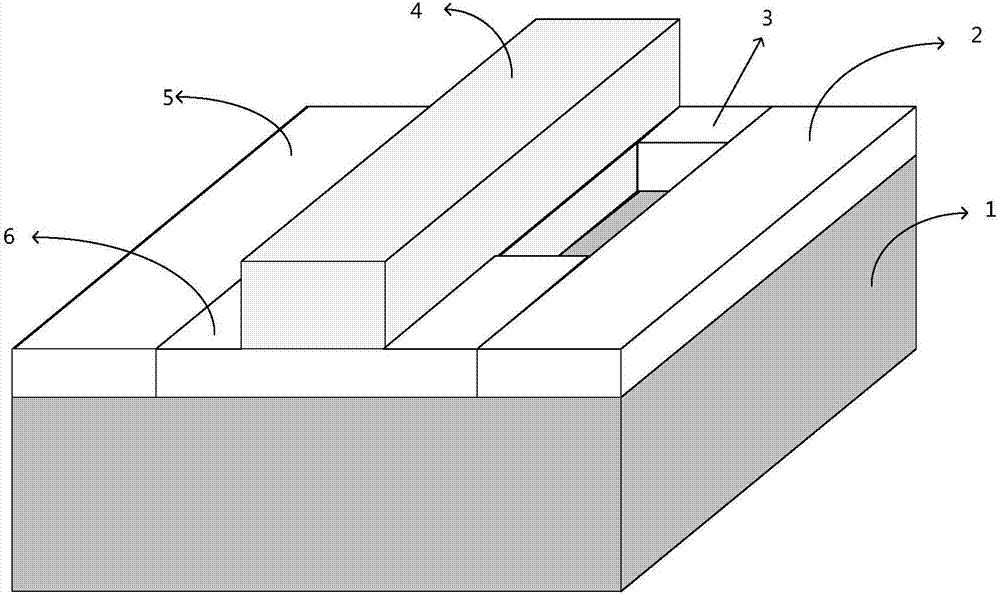

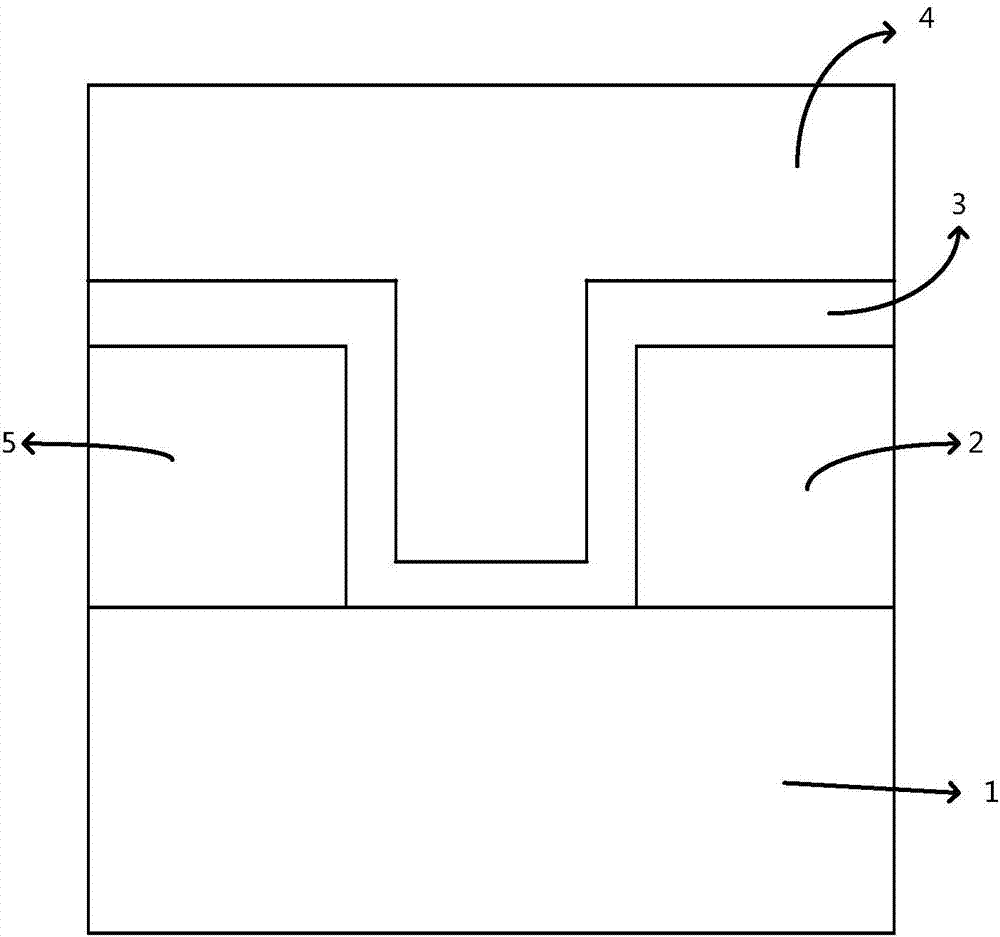

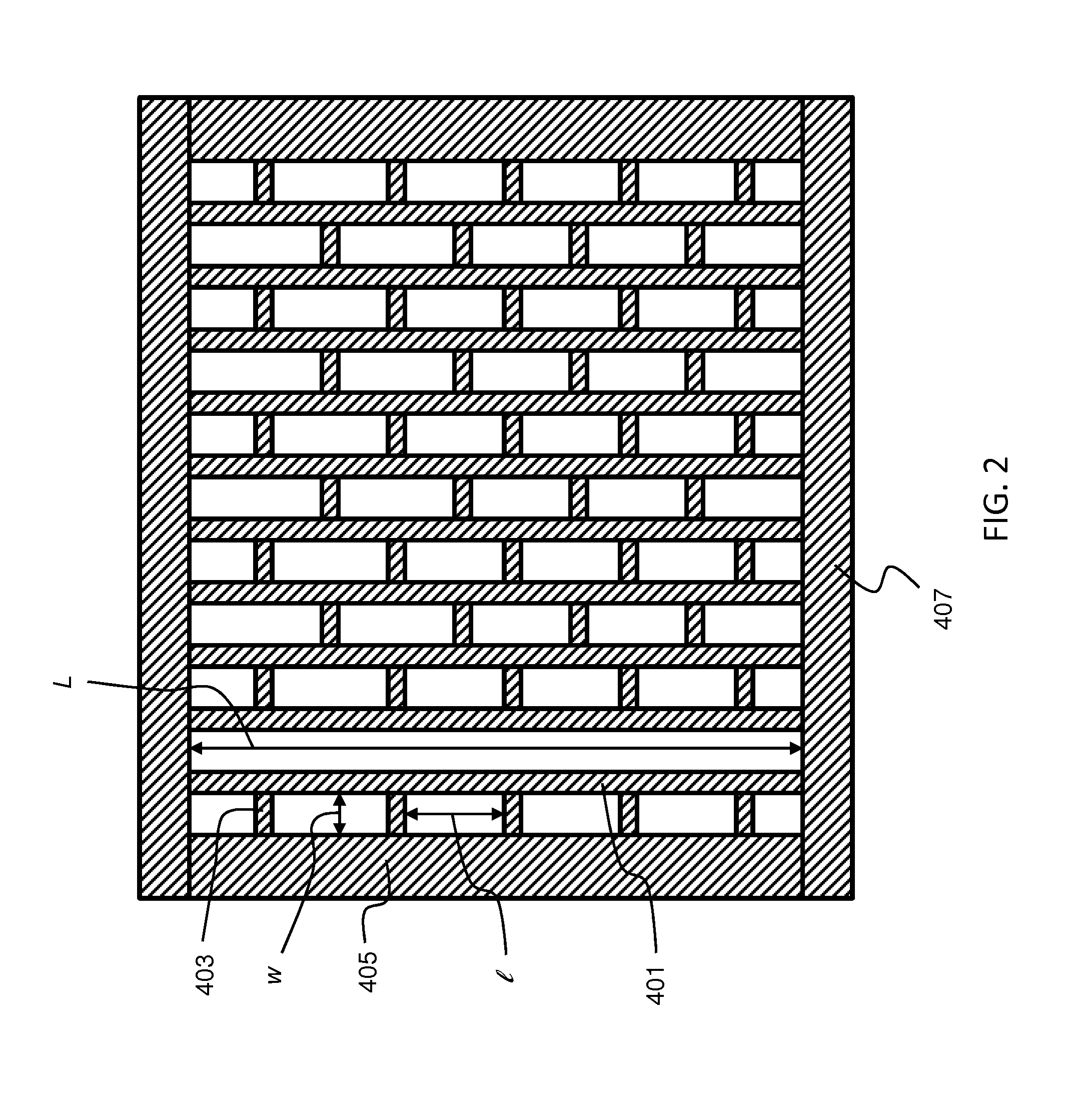

A method of manufacturing a planar channel semi-floating gate device

ActiveCN104465381BImprove performanceAvoid damageSemiconductor/solid-state device manufacturingSemiconductor devicesPlanar channelEngineering

The invention belongs to the technical field of manufacturing of semiconductor devices and particularly relates to a method for manufacturing a semi-floating gate device with planar channels. The method for manufacturing the semi-floating gate device with the planar channels comprises the steps that the semi-floating gate device with the planar channels is manufactured through a post-gate technology; after a source contact area and a drain contact area are formed, a polycrystalline silicone control gate sacrificial material is removed through etching firstly, secondly a metal control gate material occupies the position originally occupied by the polycrystalline silicone control gate sacrificial material, and then a metal control gate is formed. The metal control gate can be prevented from being damaged in a high-temperature annealing process of a source contact area and a drain contact area, and the performance of the semi-floating gate device with the planar channels is improved. In addition, according to the method, self-alignment technology is adopted to manufacture the source contact area and the drain contact area of the semi-floating gate device, the technology process is simple and stable, and production cost is reduced.

Owner:SUZHOU ORIENTAL SEMICONDUCTOR CO LTD

Microfabricated chip and method of use

ActiveUS7497937B2Easy to analyzeSludge treatmentVolume/mass flow measurementElectrophoresisProtein species

A multiplexed, absorbance-based microfabricated chip electrophoresis system, microfabricated chip, and method of use are included for the detection and identification of protein species. The microfabricated chip electrophoresis system capable of analyzing multiple samples simultaneously. The system uses a microfabricated chip having a sample chamber for first dimension separation of a sample, a first planar array of channels for second dimension separation of the sample approximately perpendicular the sample chamber, and a barrier separating the sample chamber from the first planar array of channels during the first dimension separation. In use, the sample is placed into a sample chamber, a barrier is established around the sample chamber, the sample is isoelectric focused within the sample chamber, the barrier is then removed, and the sample separated in the first array of channels by molecular weight.

Owner:AGILENT TECH INC

3-D nonvolatile memory device and method of manufacturing the same, and memory system including the 3-D nonvolatile memory device

ActiveUS8717814B2Improve reliabilitySolid-state devicesRead-only memoriesPlanar channelVertical channel

A three-dimensional (3-D) nonvolatile memory device includes vertical channel layers protruded from a substrate, interlayer insulating layers and memory cells, which are alternately stacked along the vertical channel layers, and select transistors including planar channel layers, each contacted with at least one of the vertical channel layers and being parallel to the substrate, and gate insulating layers formed over the planar channel layers.

Owner:SK HYNIX INC

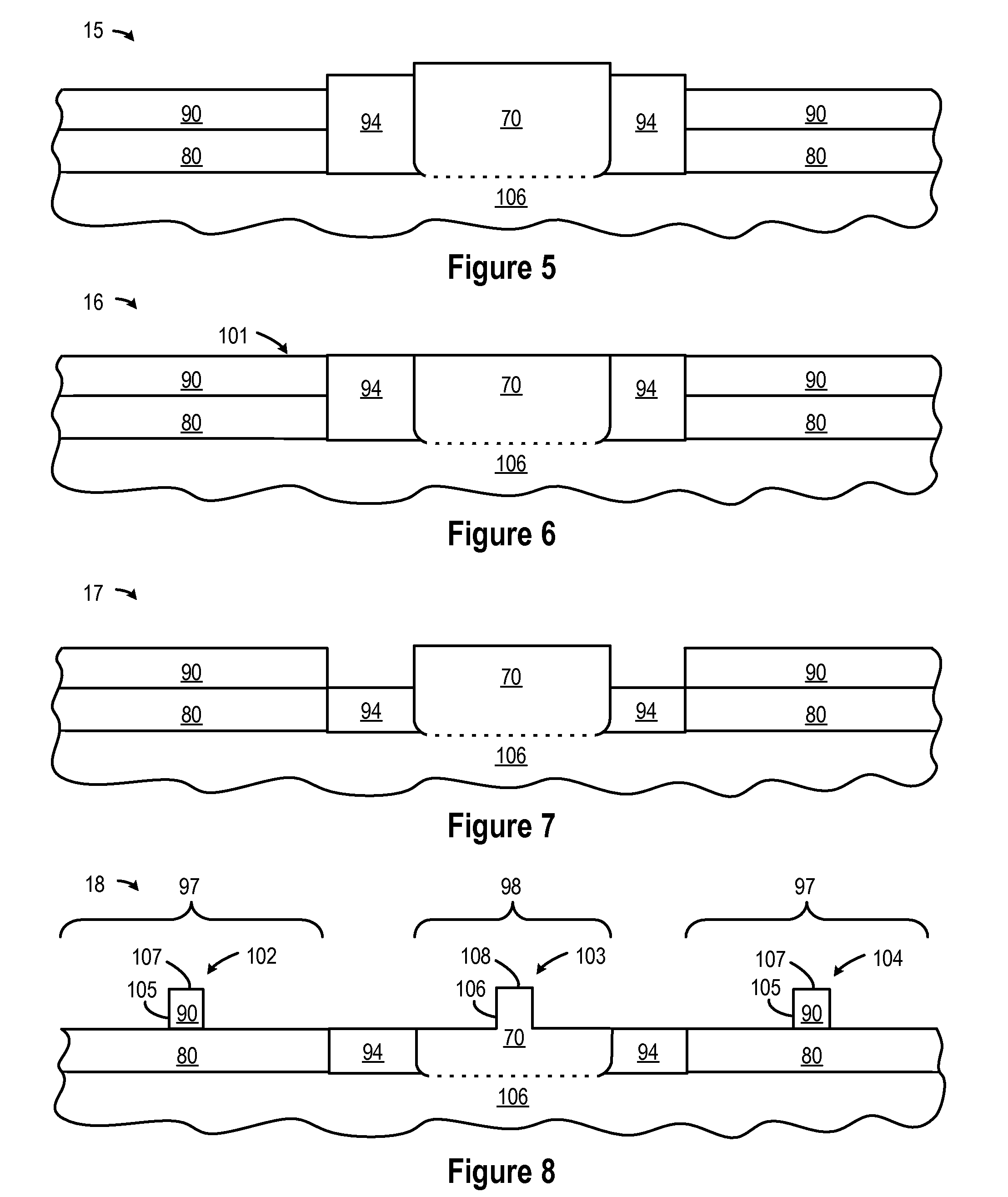

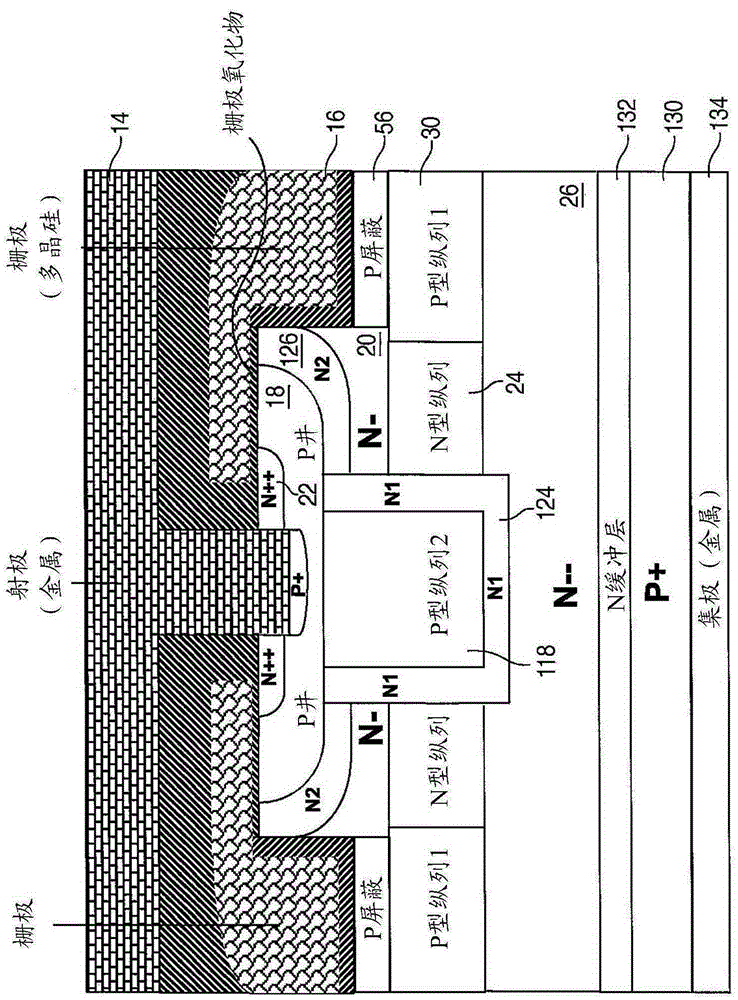

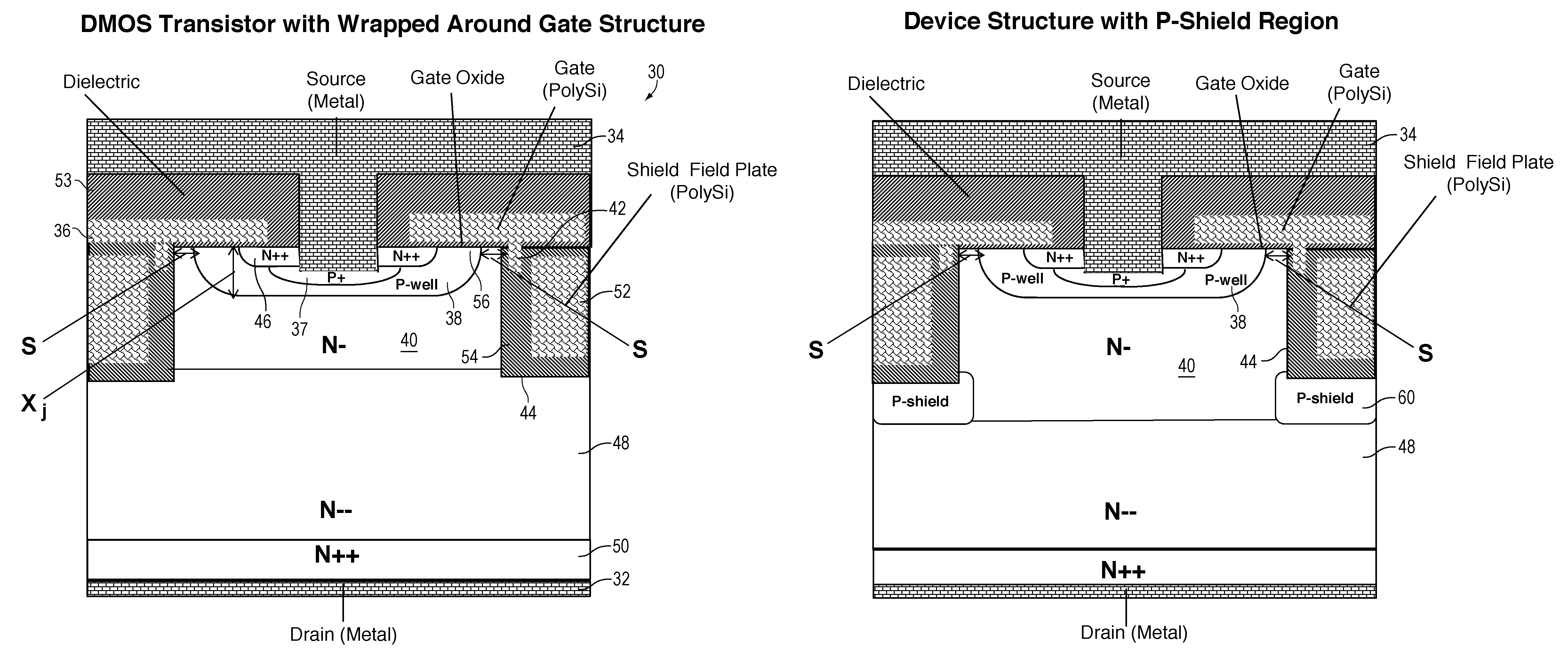

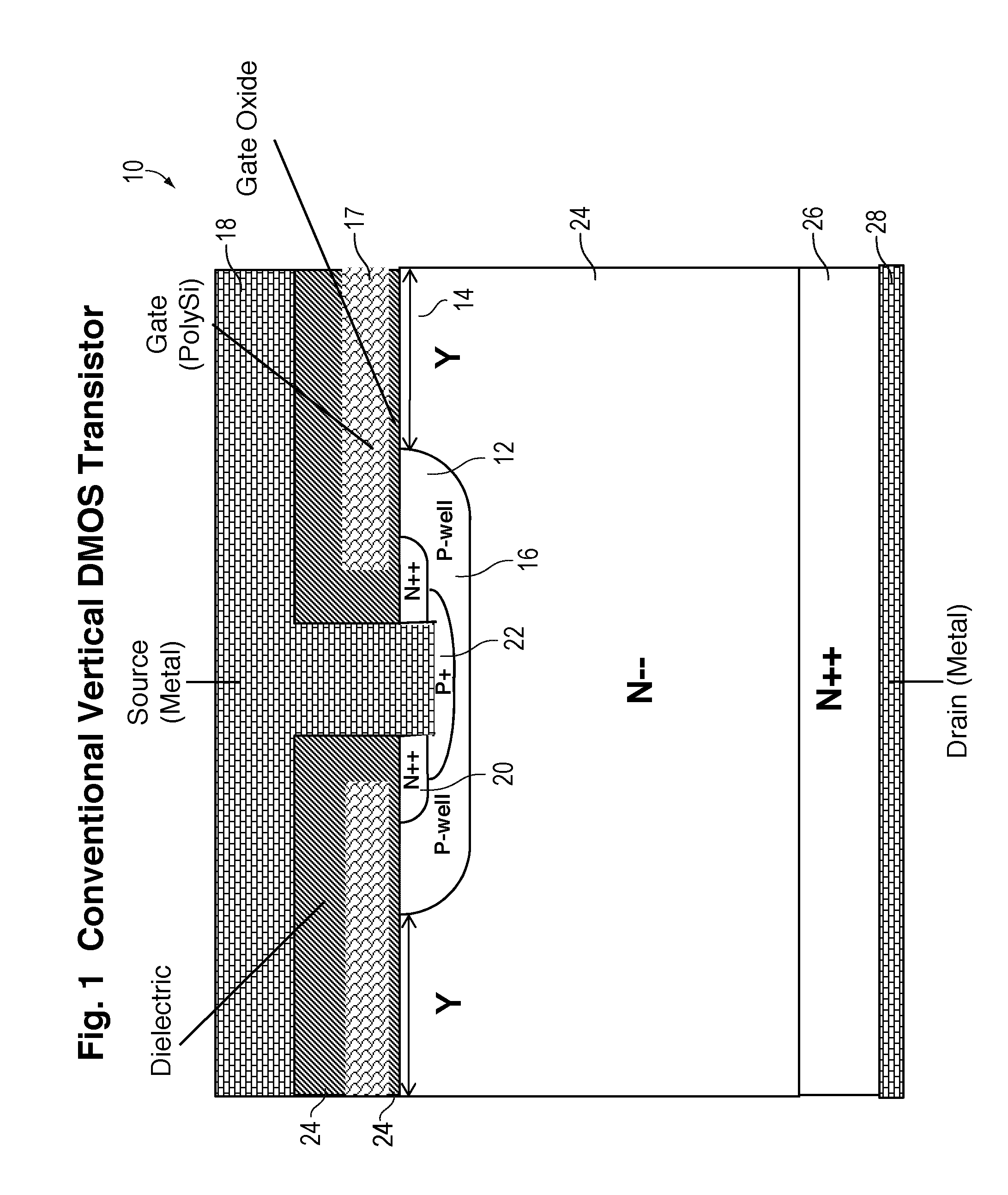

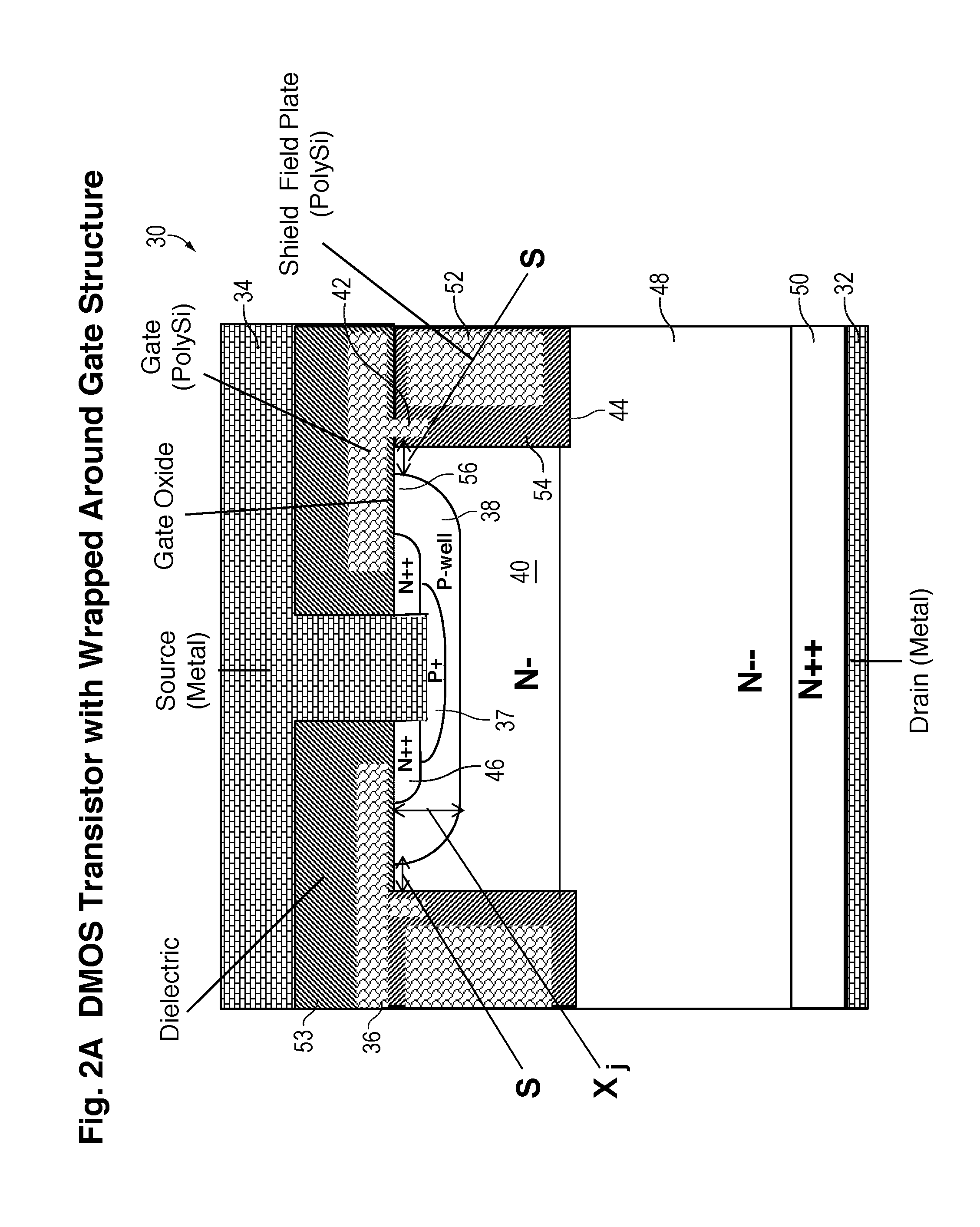

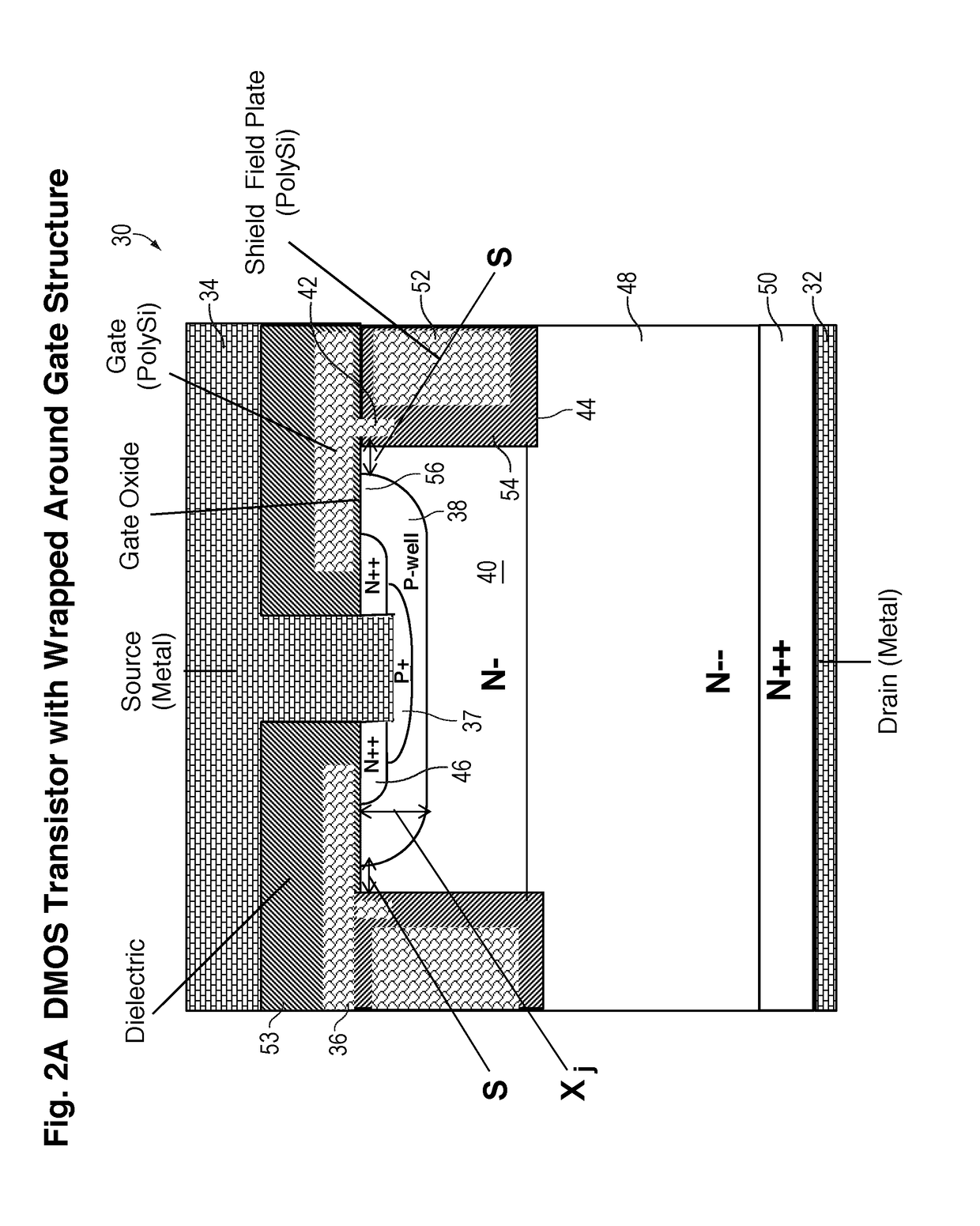

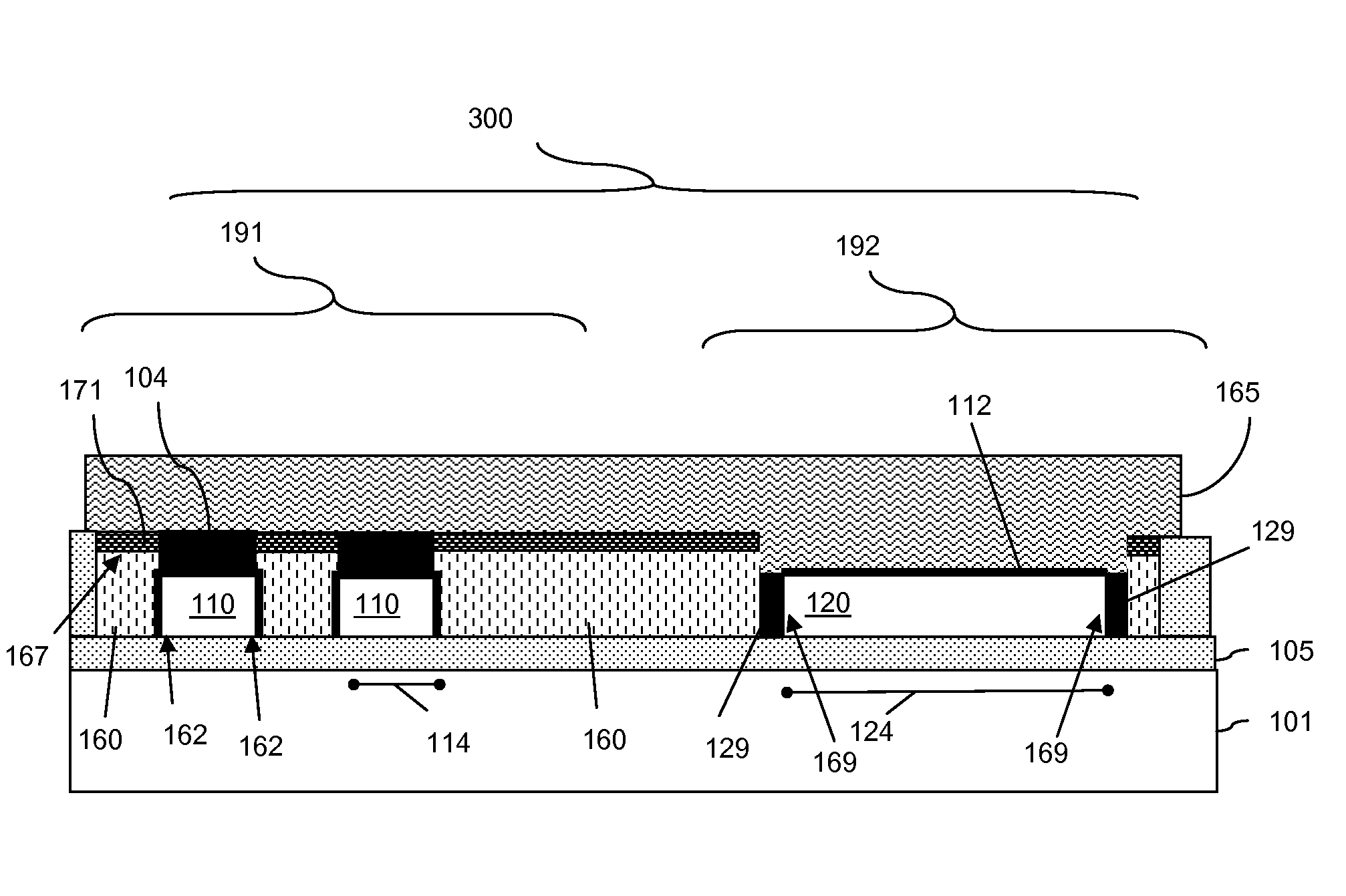

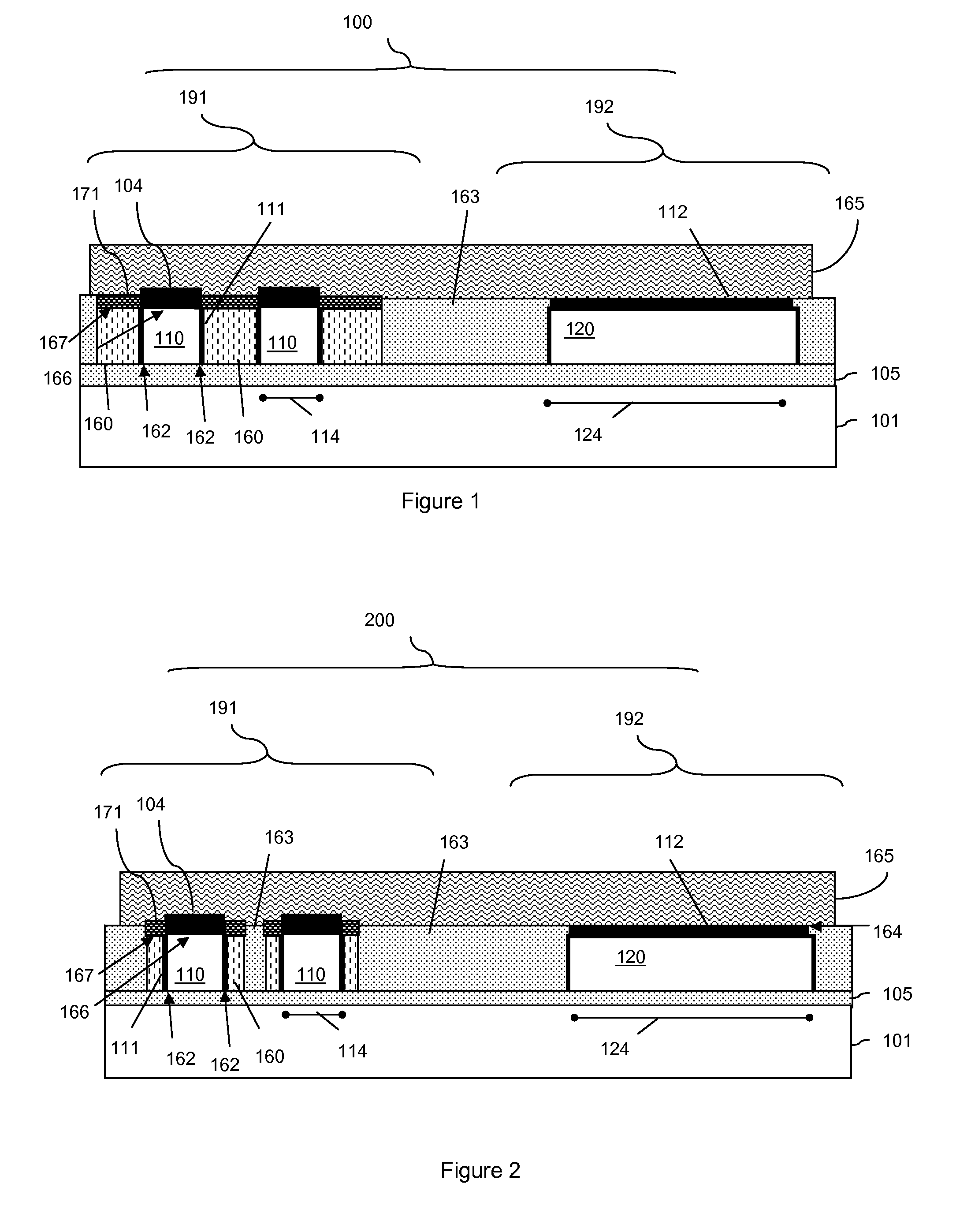

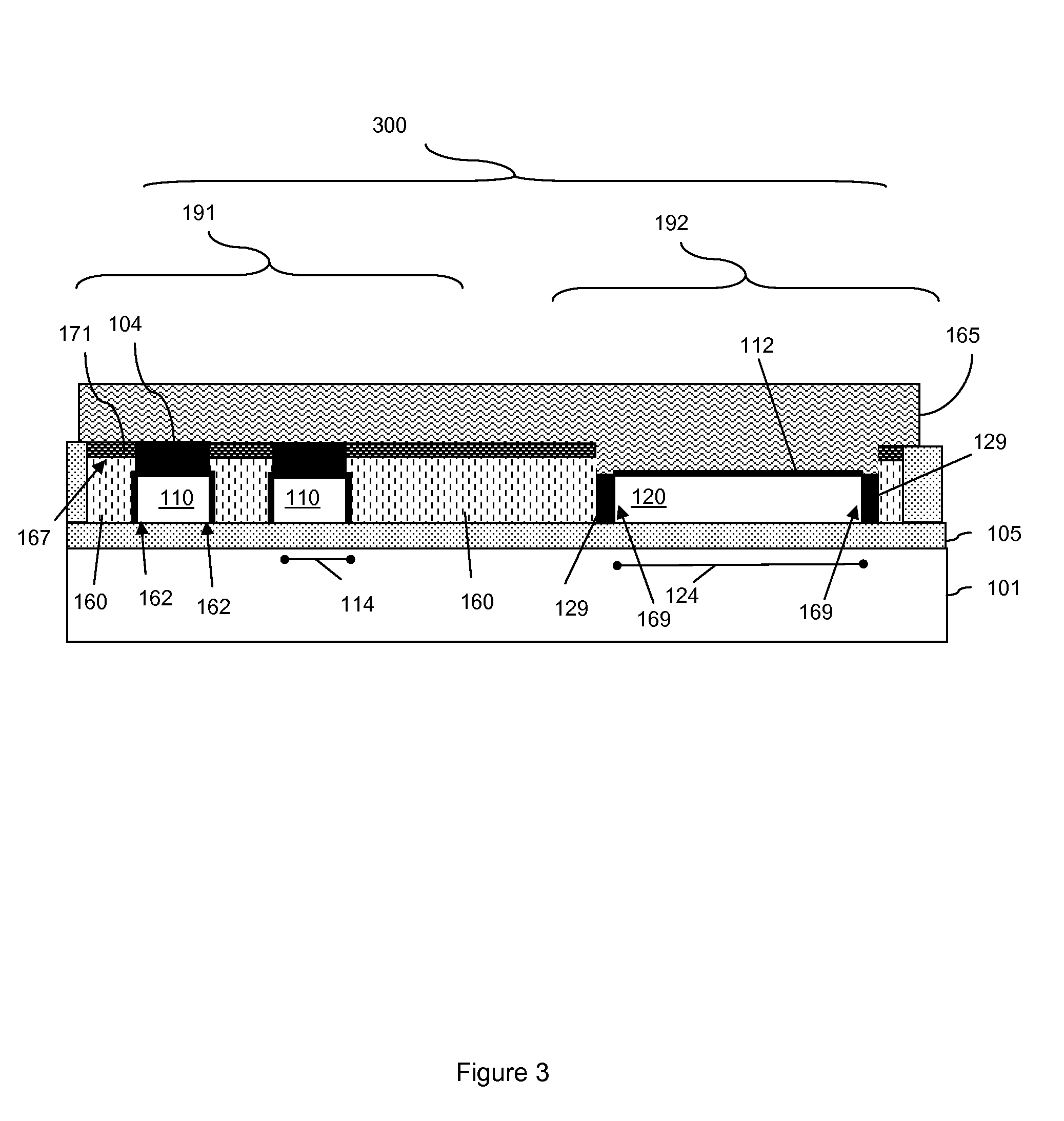

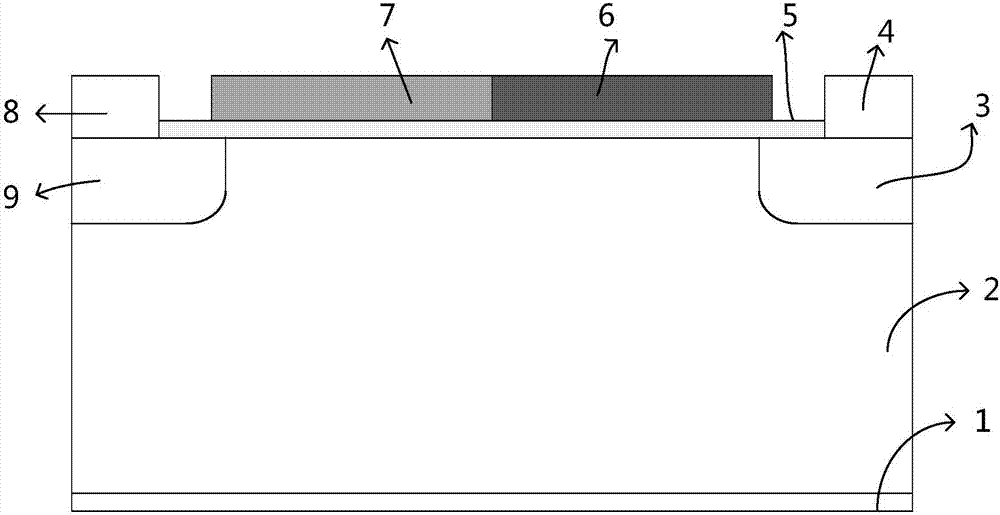

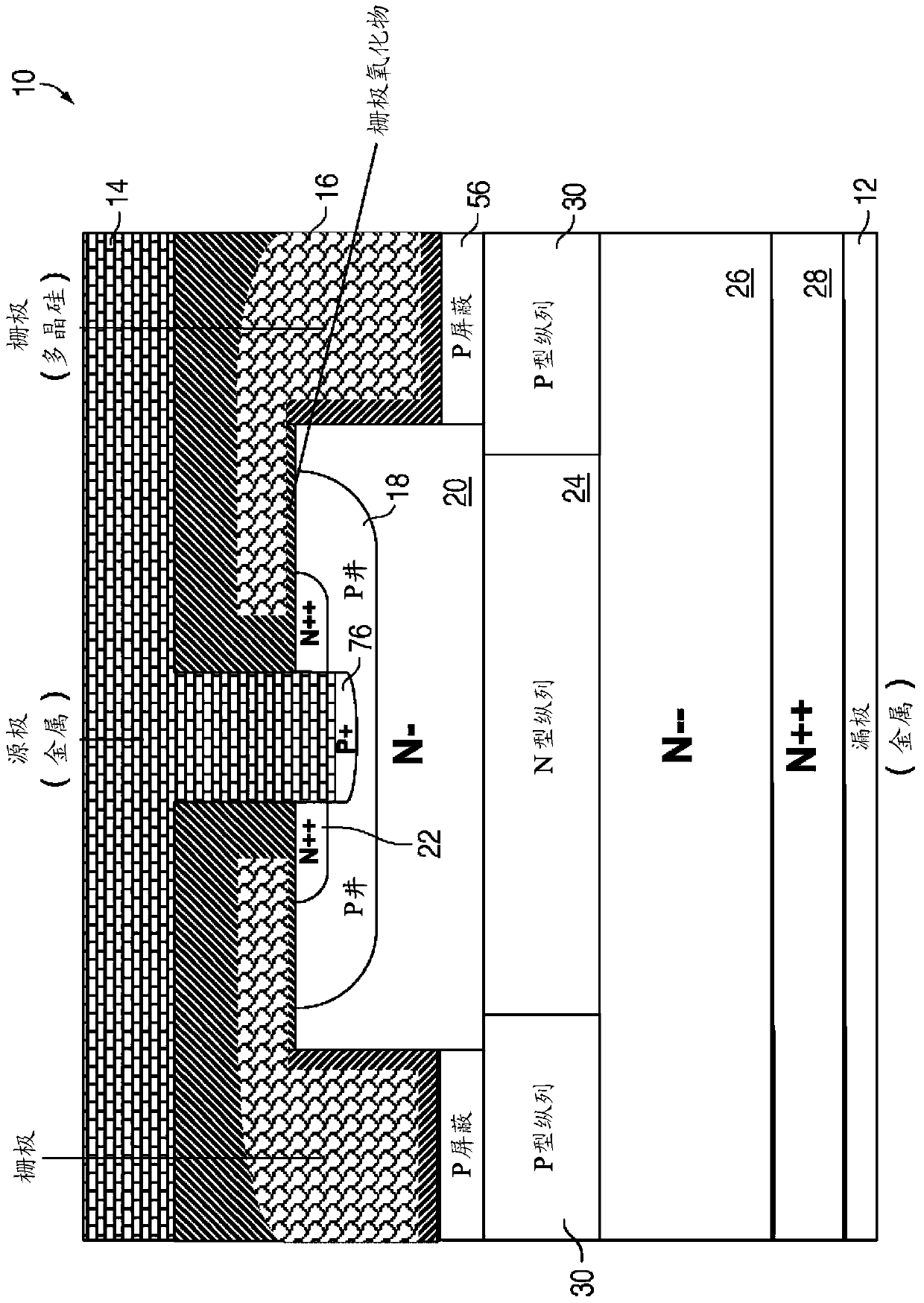

Vertical power MOSFET having planar channel and its method of fabrication

ActiveUS9184248B2Increase cell densityImprove breakdown voltageSemiconductor devicesDopantPlanar channel

A power MOSFET cell includes an N+ silicon substrate having a drain electrode. A low dopant concentration N-type drift layer is grown over the substrate. An N-type layer, having a higher dopant concentration than the drift region, is then formed and etched to have sidewalls. A P-well is formed in the N-type layer, and an N+ source region is formed in the P-well. A gate is formed over the P-well's lateral channel and has a vertical extension next to the top portion of the sidewalls. A positive gate voltage inverts the lateral channel and increases the conduction along the sidewalls to reduce on-resistance. A vertical shield field plate is also located next to the sidewalls and extends virtually the entire length of the sidewalls. The field plate laterally depletes the N-type layer when the device is off to increase the breakdown voltage.

Owner:MAXPOWER SEMICON INC

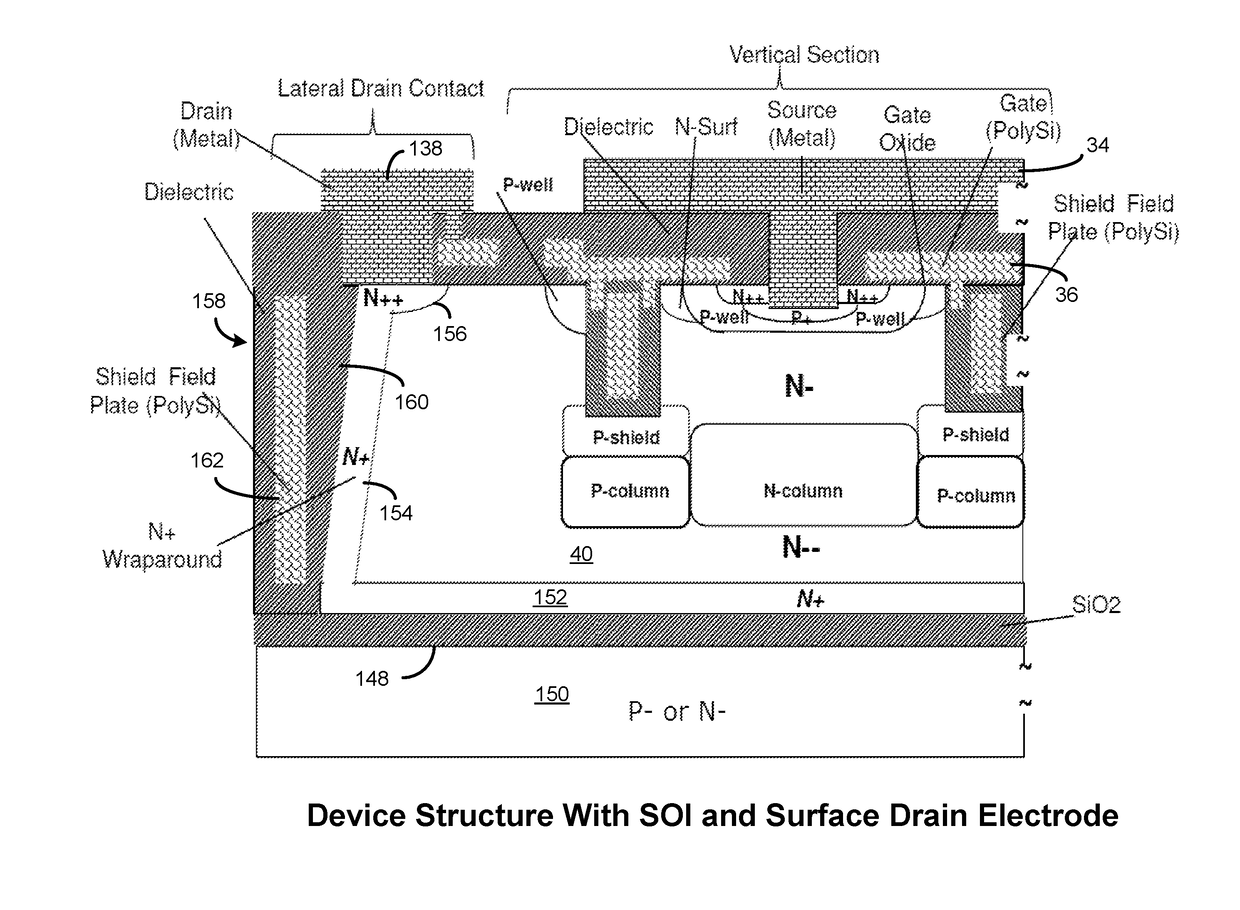

Power MOSFET having planar channel, vertical current path, and top drain electrode

ActiveUS9761702B2Increase cell densityImprove breakdown voltageSemiconductor devicesDopantPlanar channel

In one embodiment, a power MOSFET cell includes an N+ silicon substrate having a drain electrode. An N-type drift layer is grown over the substrate. An N-type layer, having a higher dopant concentration than the drift region, is then formed along with a trench having sidewalls. A P-well is formed in the N-type layer, and an N+ source region is formed in the P-well. A gate is formed over the P-well's lateral channel and has a vertical extension into the trench. A positive gate voltage inverts the lateral channel and increases the vertical conduction along the sidewalls to reduce on-resistance. A vertical shield field plate is also located next to the sidewalls and may be connected to the gate. The field plate laterally depletes the N-type layer when the device is off to increase the breakdown voltage. A buried layer and sinker enable the use of a topside drain electrode.

Owner:MAXPOWER SEMICON INC

Polymeric acetabular cup

An orthopedic prosthesis comprising a polymeric cup member for use in a ball and socket joint is disclosed. The cup member may include several advantageous features such as a multi-directional and multi-planar channel having an undercut area that provides a mechanical lock between the cup member and a fixation material for enhanced fixation. The cup member may further comprise a plurality of spacers for ensuring an even mantle of fixation material between the cup member and the bone, a series of divots for enhancing fixation, a locating feature that permits a physician to visualize and locate the cup member in the socket of the patient's bone on appropriate medical equipment, and a lead-in chamfer located between a terminal edge and an interior surface of the cup member. Further, the terminal edge of the cup member may comprise a planar rim or may alternatively comprise a hood located distally from said terminal edge.

Owner:ORTHO DEV CORP

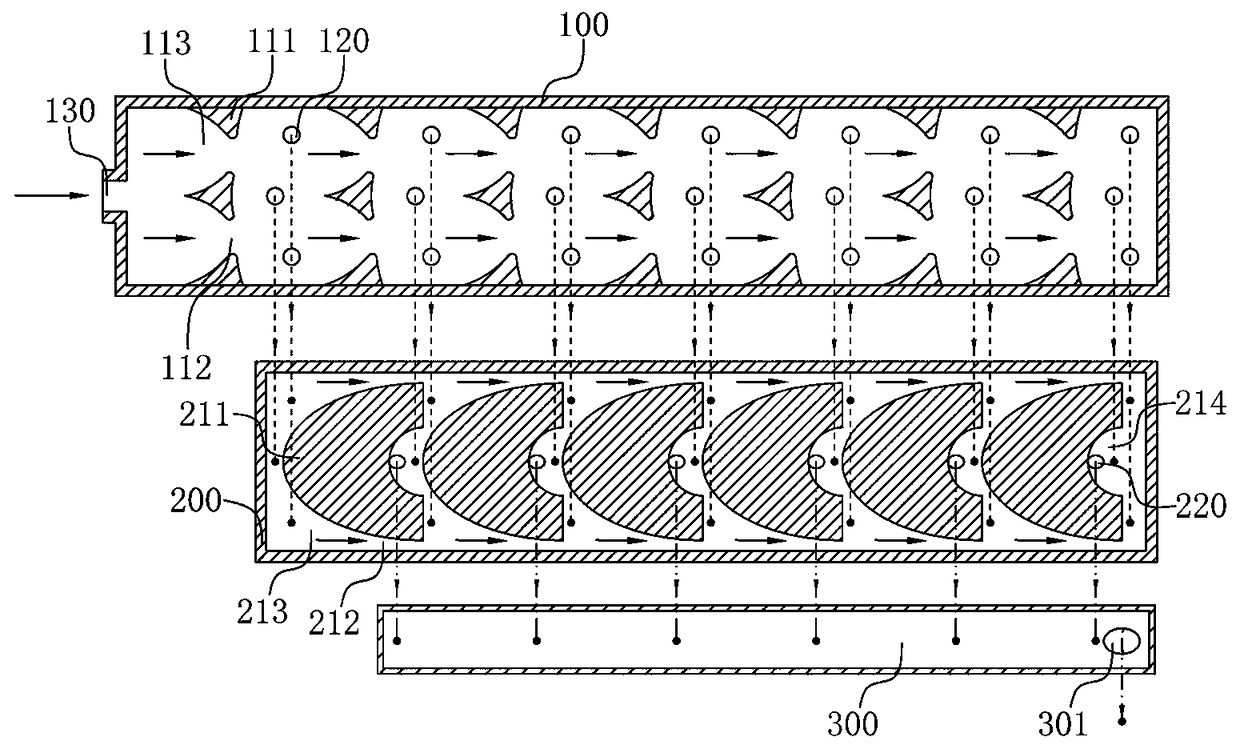

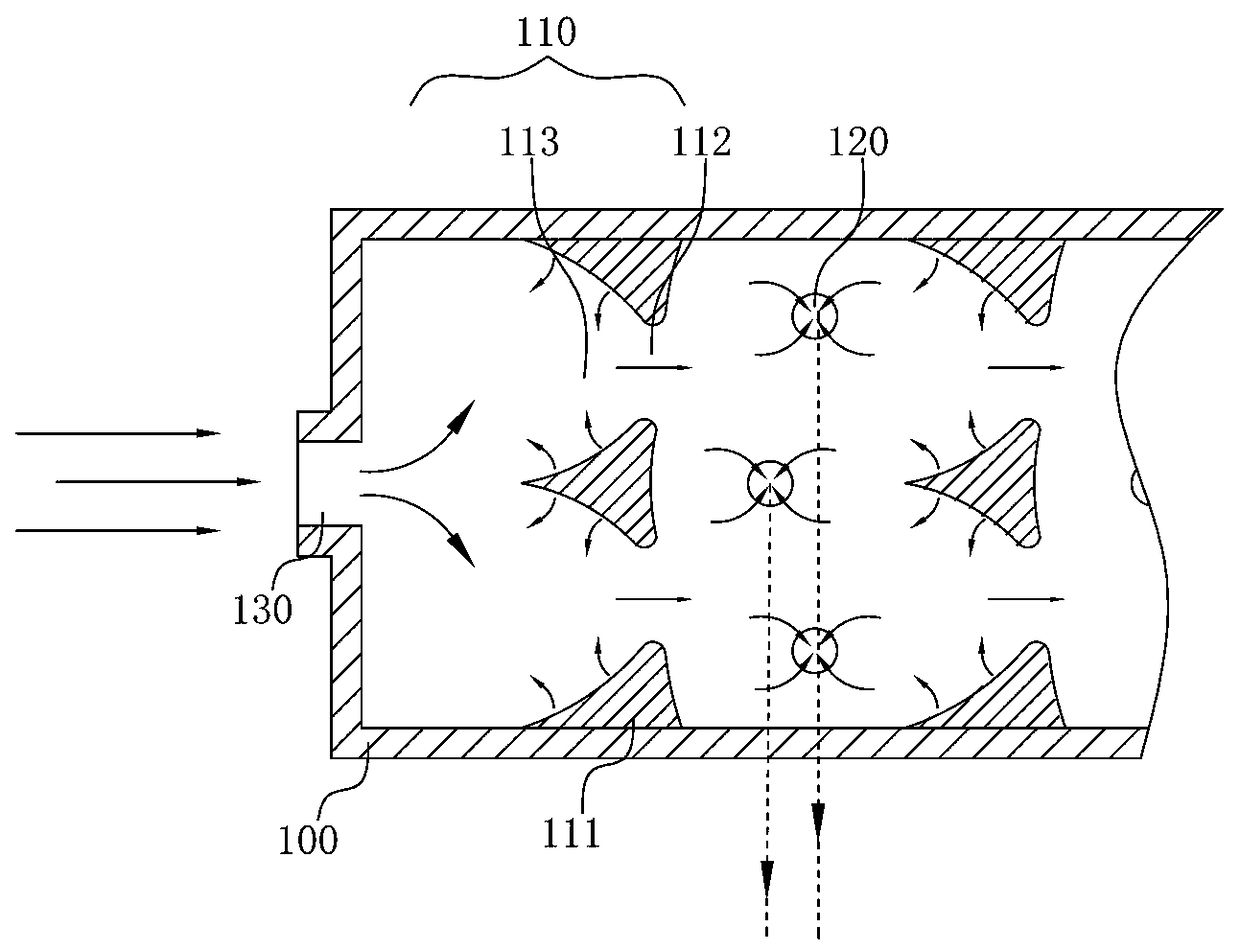

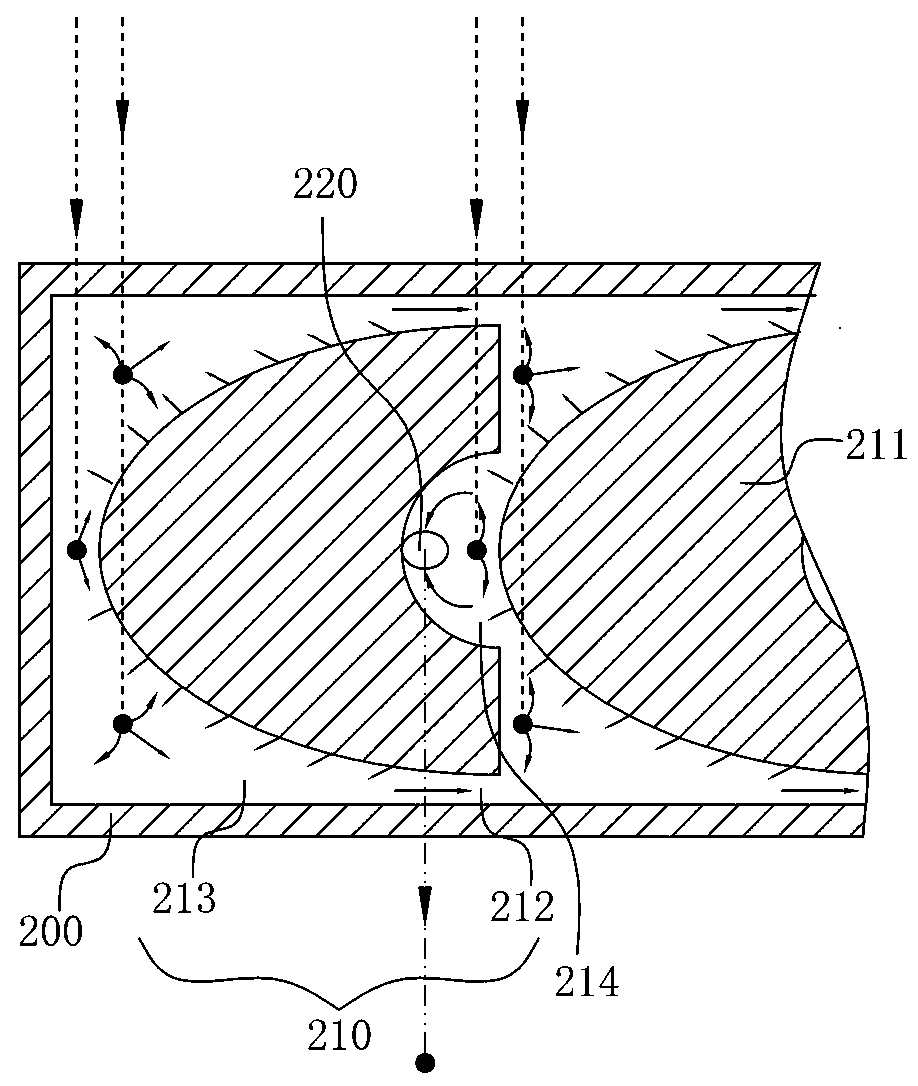

Outflow constant method and structure

PendingCN109324642AAvoid cloggingAvoid aging problemsFlow control using electric meansPlanar channelEngineering

The invention belongs to the technology field of irrigation. The outflow constant structure comprises: an upper plane channel, wherein a plurality of primary energy dissipating units are arranged in sequence inside the upper plane channel and a water inlet is arranged at the front end of the upper planar channel; a lower plane channel, wherein a plurality of secondary energy dissipating units arearranged in sequence inside the lower plane channel, a plurality of primary energy dissipating units are respectively arranged corresponding to the plurality of the secondary energy dissipating units,and corresponding communication holes are arranged between the corresponding primary energy dissipating units and the secondary energy dissipating units; and an outlet channel, wherein each of the secondary energy dissipating units is connected to the outlet channel through an outlet and a constant flow port is arranged on the outlet channel. The invention further discloses an outflow constant method. The overall structure of the outflow constant structure has no moving parts, the energy dissipating path is automatically selected according to the water inlet pressure through the four-dimensional energy dissipation, thereby realizing constant flow and constant pressure on the outlet.

Owner:NORTH CHINA UNIV OF WATER RESOURCES & ELECTRIC POWER

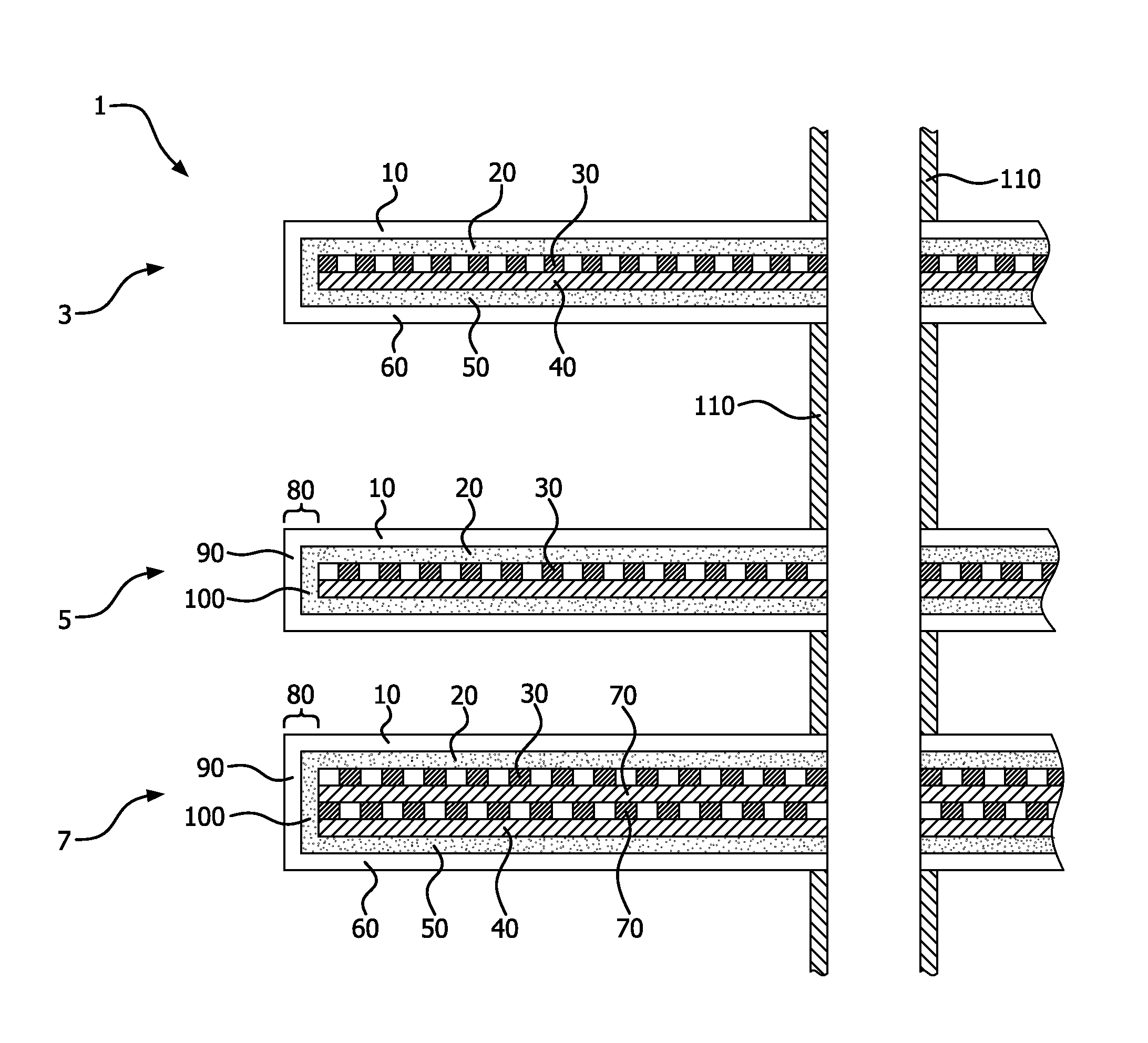

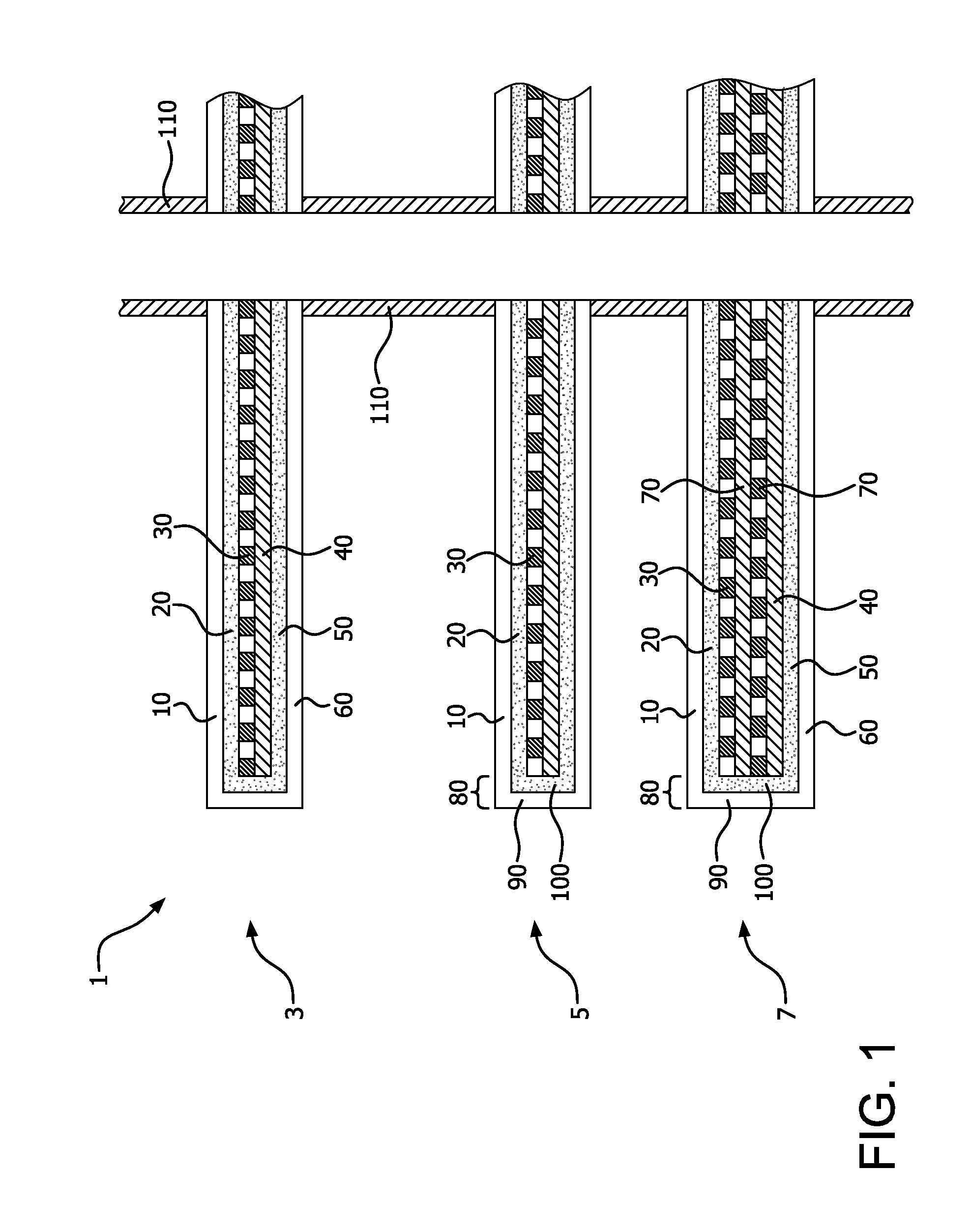

Solid-State Membrane Module

InactiveUS20150209721A1Improve component reliabilityRelieve pressureMembranesSemi-permeable membranesPlanar channelOxygen

A module for separating oxygen from an oxygen-containing gaseous mixture comprising planar solid-state membrane units, each membrane unit comprising planar dense mixed conducting oxides layers, planar channel-free porous support layers, and one or more planar intermediate support layers comprising at least one channeled porous support layer. The outer rim circumscribing the planar solid-state membrane units comprises a dense mixed conducting oxide layer and a channel-free porous support layer.

Owner:AIR PROD & CHEM INC

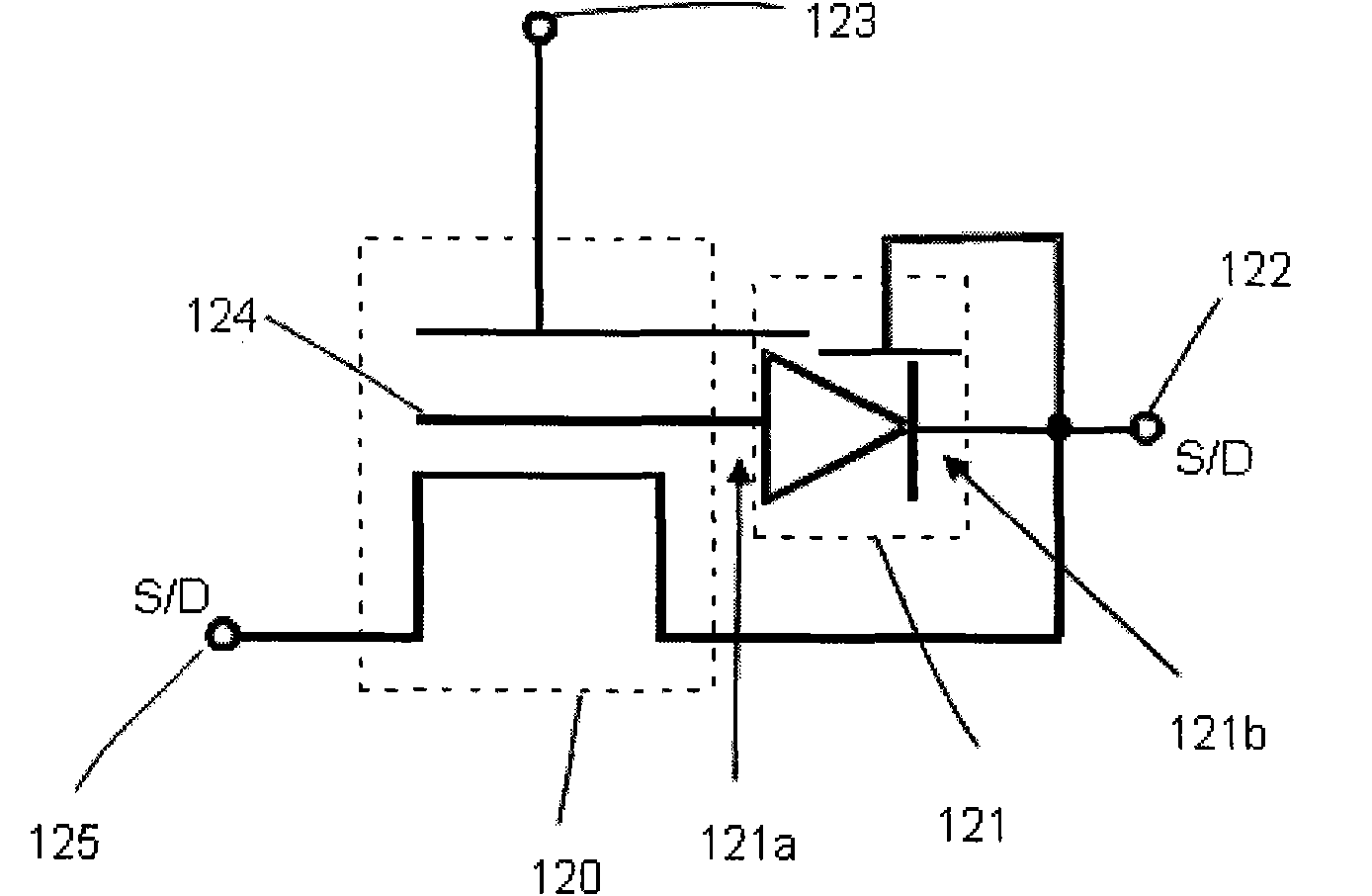

Dual work-function single gate stack

InactiveUS7449735B2Improve mobilitySolid-state devicesSemiconductor/solid-state device manufacturingCMOSValence band

Disclosed is a complementary CMOS device having a first FET with sidewall channels and a second FET with a planar channel. The first FET can be a p-FET and the second FET can be an n-FET or vice versa. The conductor used to form the gate electrodes of the different type FETs is different and is pre-selected to optimize performance. For example, a p-FET gate electrode material can have a work function near the valence band and an n-FET gate electrode material can have a work function near the conduction band. The first gate electrodes of the first FET are located adjacent to the sidewall channels and the second gate electrode of the second FET is located above the planar channel. However, the device structure is unique in that the second gate electrode extends laterally above the first FET and is electrically coupled to the first gate electrodes.

Owner:ALSEPHINA INNOVATIONS INC

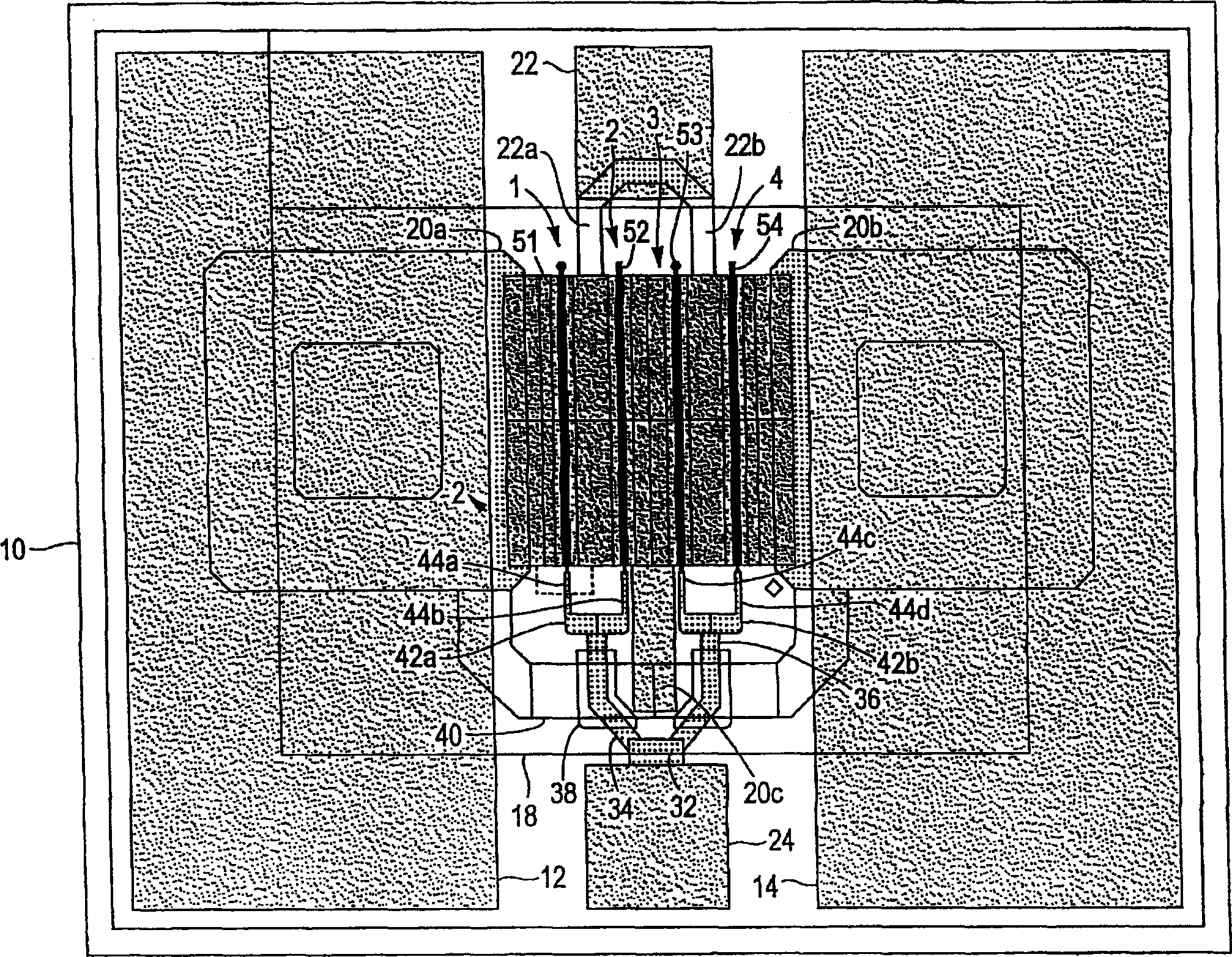

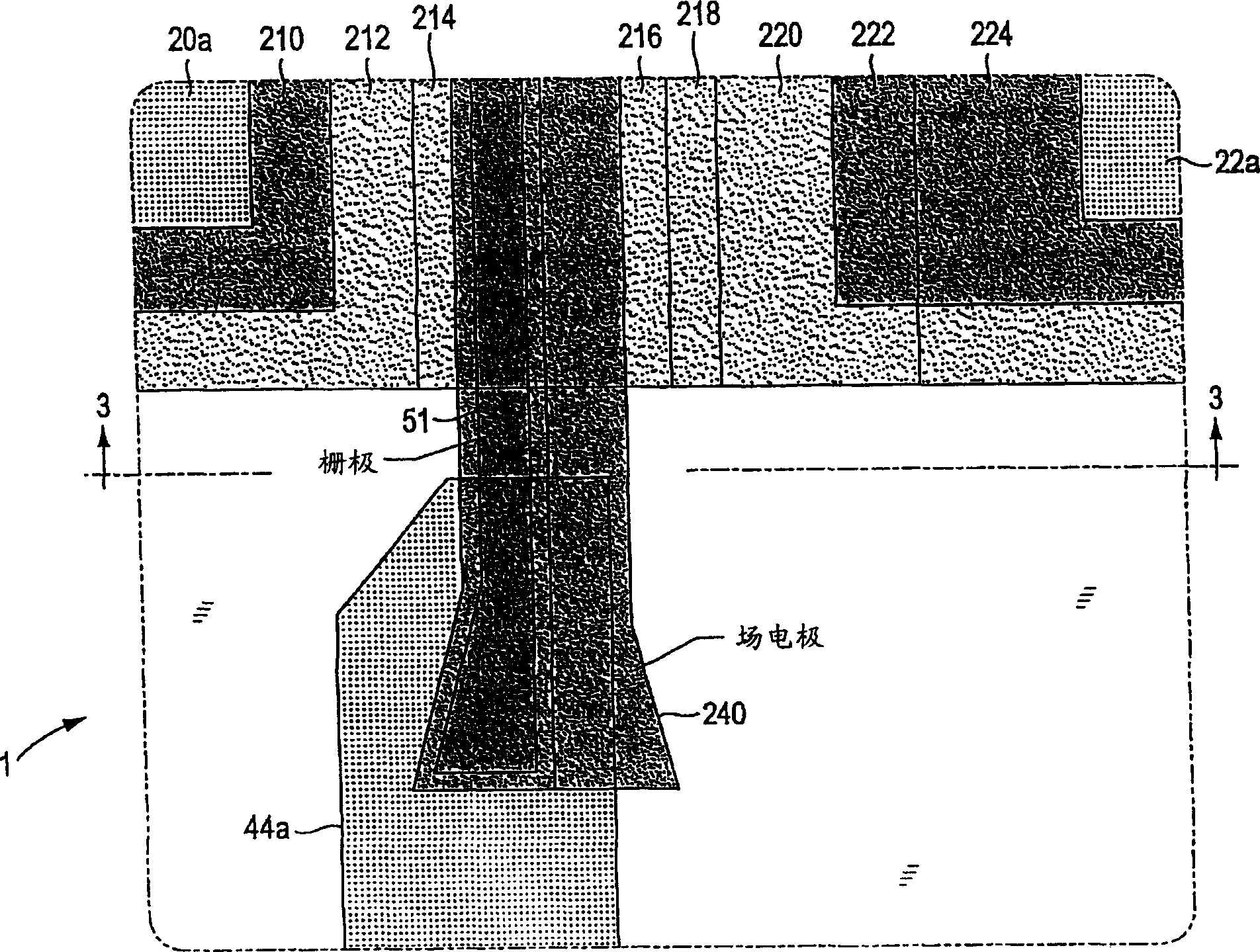

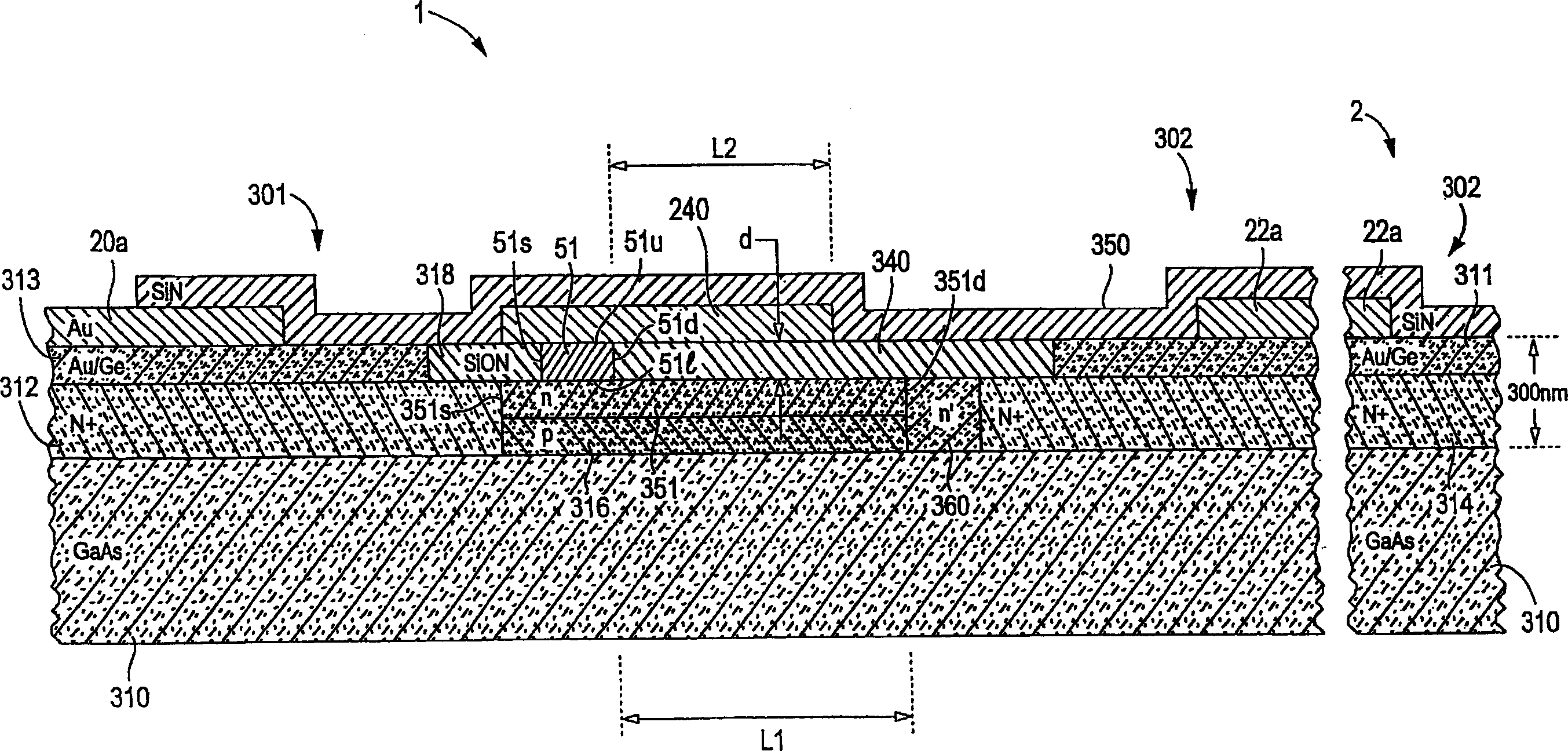

Field electrode metal semiconductor field effect transistor

InactiveCN1477716AShared drain structureShared source structureSolid-state devicesSemiconductor/solid-state device manufacturingElectrical conductorPlanar channel

A planar MESFET transistor includes a plurality of FET elements. Each FET element includes a doped planar channel, and source and drain coupled to the ends of the channel. A gate conductor extends over a portion of the channel at a location lying between the source and drain, a first predetermined distance from the drain. A field plate is connected to the gate conductor, and extends toward the drain a second predetermined distance, isolated from the channel except at its gate conductor connection by a dielectric material.

Owner:COBHAM DEFENSE ELECTRONICS SYST CORP

MOSFET structure

InactiveCN107195680AReduce electric field peaksImprove performanceSemiconductor devicesDevice materialPlanar channel

The invention discloses a MOSFET structure which belongs to the technical field of semiconductor devices and comprises a substrate electrode, a substrate, a channel region, a source region, a drain region, a source electrode, a drain electrode, a gate oxide layer and a gate electrode. The channel region with a non-planar surface is formed in a substrate region built in the substrate, and the source region and the drain region are arranged on both sides of the channel region respectively. The source electrode and the drain electrode are correspondingly arranged in the source region and the drain region respectively. The gate oxide layer covers the surface of the non-planar channel region. The gate electrode is arranged on the surface of the gate oxide layer, and both ends of the gate electrode are spaced from the source electrode and the drain electrode. Both ends of the gate electrode respectively extend to the source region and the drain region to form overlap. According to the invention, the non-planar channel MOSFET structure is used to reduce the electric field peak of the drain region and increase the effective channel length of a device; a leakage-induced barrier reducing effect is improve and suppressed; a short channel effect is suppressed; the high electric field of the drain region is reduced; the generation of hot carriers is suppressed; and the stability of the device is improved.

Owner:NANJING UNIV OF POSTS & TELECOMM

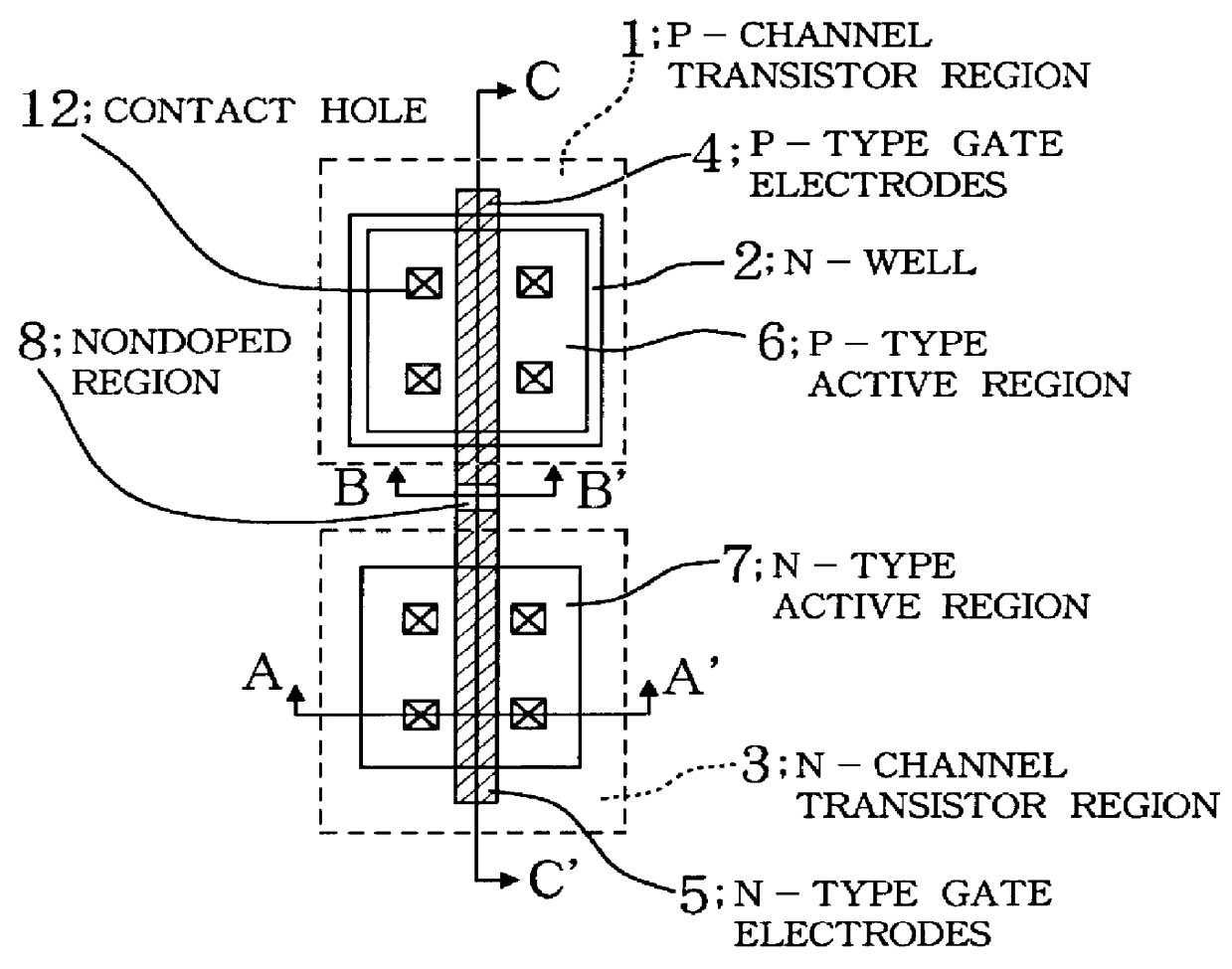

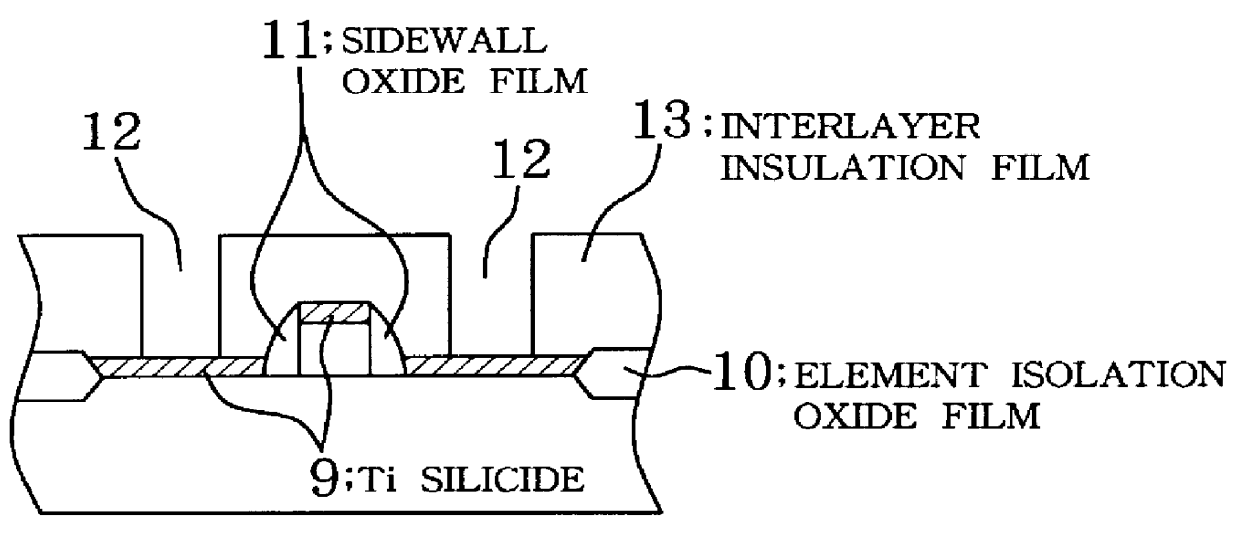

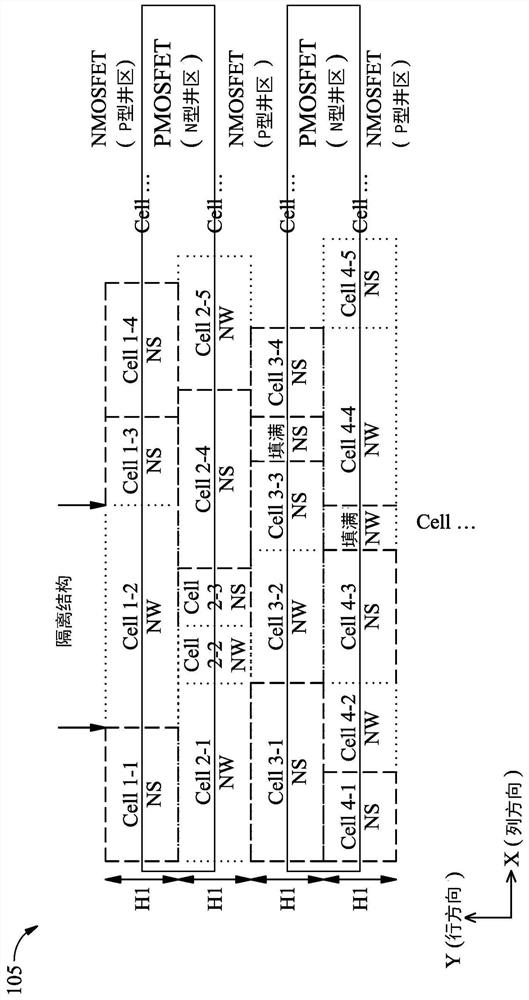

Planar channel-type MOS transistor

InactiveUS6043546ASemiconductor/solid-state device manufacturingSemiconductor devicesPlanar channelP channel

In the manufacture of a planar channel-type MOS transistor, an n-well is formed in a predetermined region of a p-type semiconductor substrate to define a p-channel transistor region in which element forming regions are located as a p-type active region and a p-type gate electrode. A p-type substrate region adjacent to the p-channel transistor region defines an n-channel transistor region in which element forming regions are located as an n-type active region and an n-type gate electrode. Titanium silicide is formed in self-alignment as an upper layer of each of the p- and n-type active regions and p- and n-type gate electrodes. A boundary of the p- and n-type gate electrodes is a nondoped region where the titanium silicide is formed in an increased thickness as compared to that of the titanium silicide formed on the remaining portion of the gate electrodes.

Owner:NEC CORP

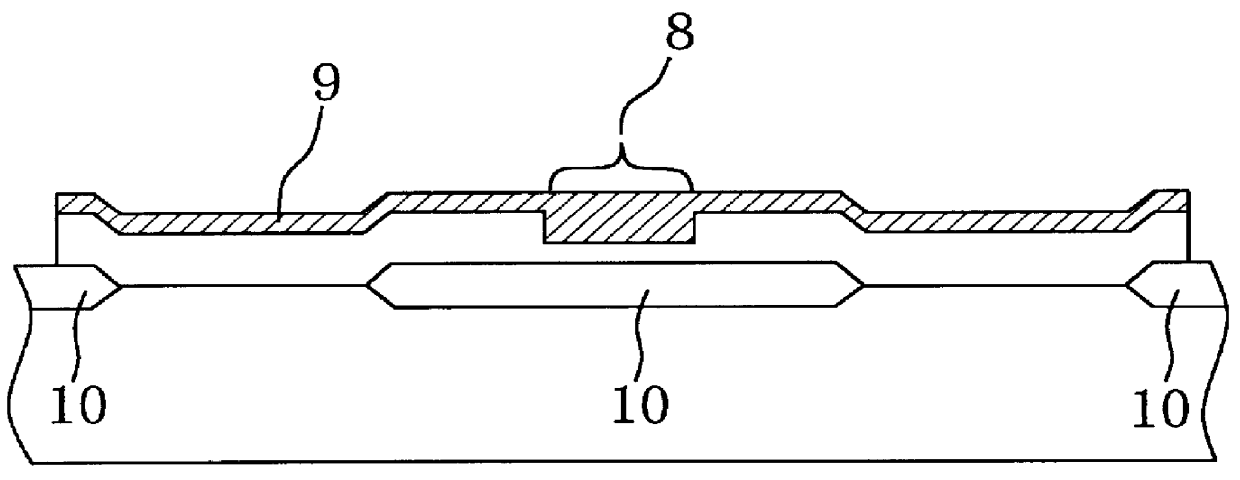

System and method for adjusting the land channel length of an extrusion die

The invention provides a system and method for adjusting the length of a channel of a flat portion in an extrusion die. The extrusion die having an adjustable flat channel can be formed from a mold body including a first mold body portion and a second mold body portion, a first lip body, a second lip body, and a flat channel body. The extrusion die can have a flow channel that includes a flat portion channel terminating in the exit aperture. The flow channel may be defined on one side by a first mold body portion, a flat portion channel body and a first lip body. The flow channel may be defined on the opposite side by the second mold body portion and the second lip body. In some examples, the length of the channel of the flat portion may be adjusted by configuring the planar channel body and / or the first lip body to move across the width of the flow channel.

Owner:NORDSON CORP

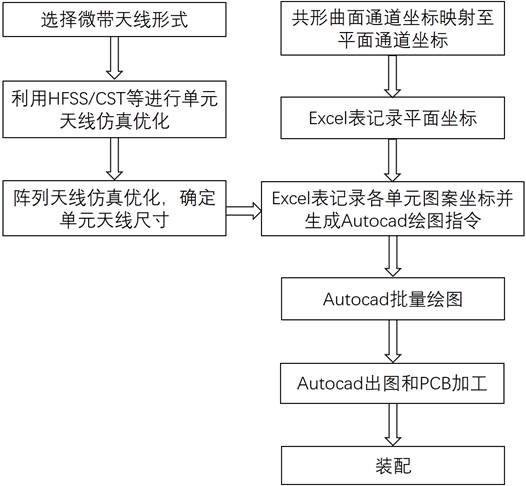

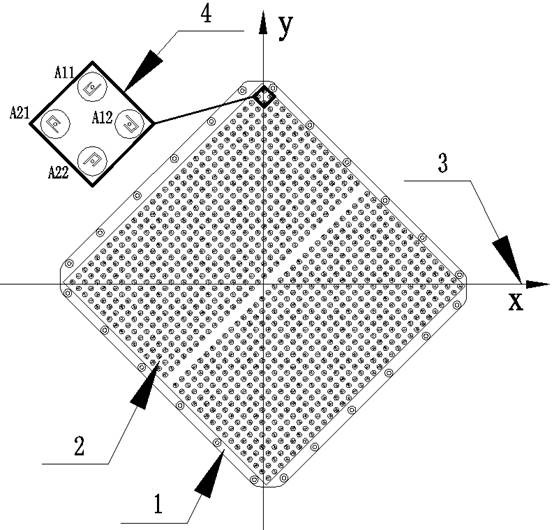

Conformal array antenna design method, computer equipment and storage medium

ActiveCN114447628AGuaranteed accuracyAvoid error proneAntenna adaptation in movable bodiesRadiating elements structural formsMicrostrip patch antennaAntenna design

The invention discloses a conformal array antenna design method, computer equipment and a storage medium. The method comprises the following steps: determining the form of a microstrip patch antenna; based on the micro-strip patch antenna and the preset bending curvature radius of the conformal array antenna, performing simulation and optimization design on the unit antenna by using three-dimensional electromagnetic field simulation software; the unit antennas form an array antenna, simulation optimization is carried out, and the final size of the antenna unit is determined; calculating corresponding plane channel position coordinates after the channel position coordinates on the curved surface of the conformal array antenna are flattened; writing pattern coordinates of the array antenna in the drawing tool software by utilizing tabulation software, writing a corresponding drawing command symbol, and copying and pasting the command symbol in a command line of the drawing tool software to complete pattern drawing of the array antenna; drawing out and carrying out PCB (Printed Circuit Board) processing; and bending, attaching and fixing the array antenna in the form of the plane PCB on the curved-surface carrier plate to form the final conformal array antenna. The method is wide in applicability, efficient and feasible.

Owner:成都雷电微力科技股份有限公司

Vertical power MOSFET cell with planar channel

ActiveCN105431946BLow costHigh dopingSemiconductor/solid-state device manufacturingSemiconductor devicesPower flowPlanar channel

The invention discloses a vertical power metal-oxide-semiconductor field-effect transistor cell with a planar channel, which comprises an N+ silicon substrate with a drain electrode. The N-type drift layer with low doping concentration is longer than the substrate. Alternate N-type columns and P-type columns are formed on the drift layer and have higher doping concentration. An N-type layer having a higher doping concentration than the drift region is then formed and etched with sidewalls. A P-well is formed in the N-type layer, and an N+ source region is formed in the P-well. A gate is formed on the lateral channel of the P-well near the sidewall to act as a vertical field plate. A source electrode contacts the P-well and the source region. A positive gate voltage inverts the lateral channel and increases conductivity along the sidewalls. The current between the source and the drain flows laterally and then vertically through various N layers. Turn-on resistance is reduced and the breakdown voltage is increased.

Owner:无锡美偌科微电子有限公司

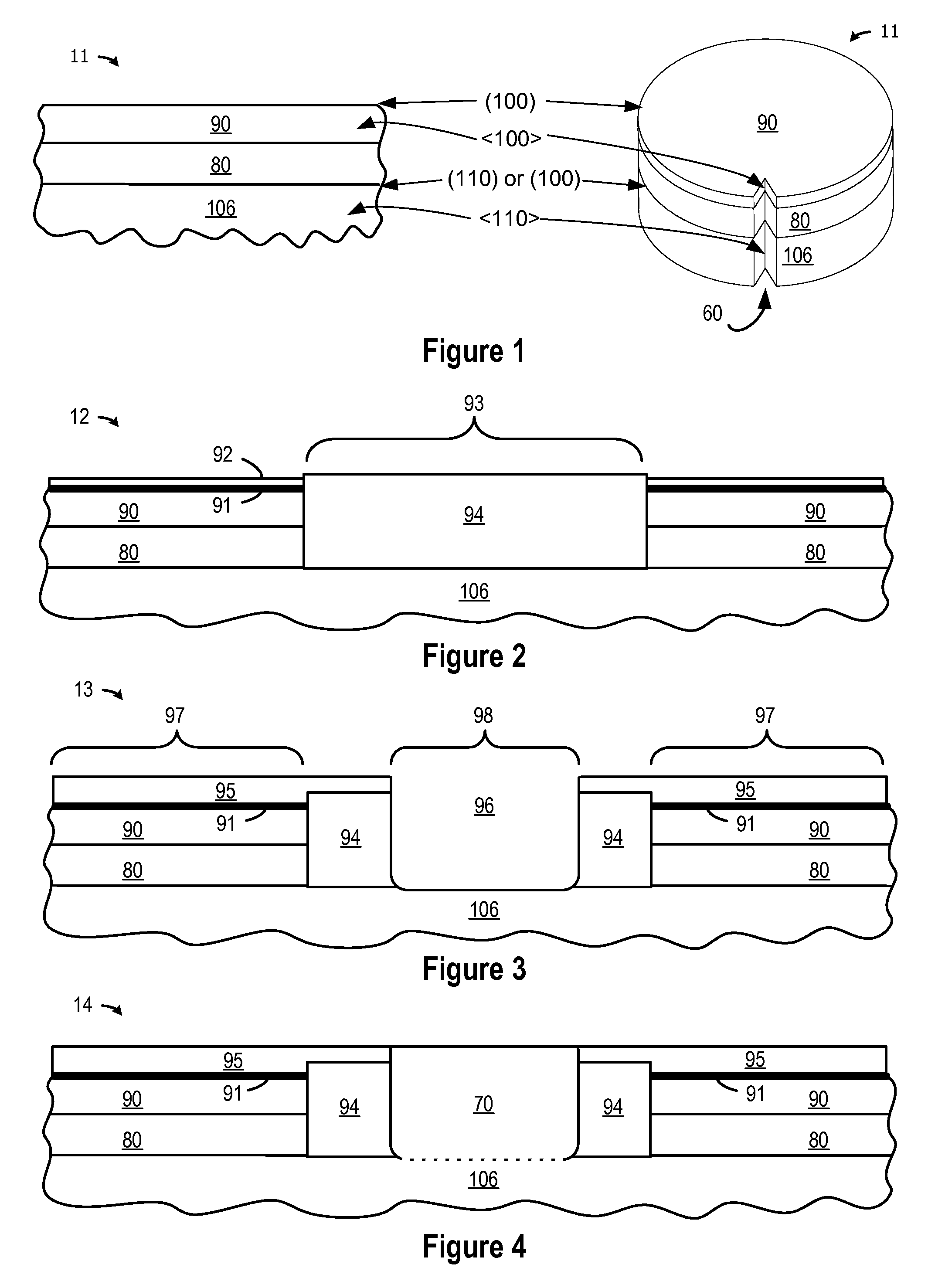

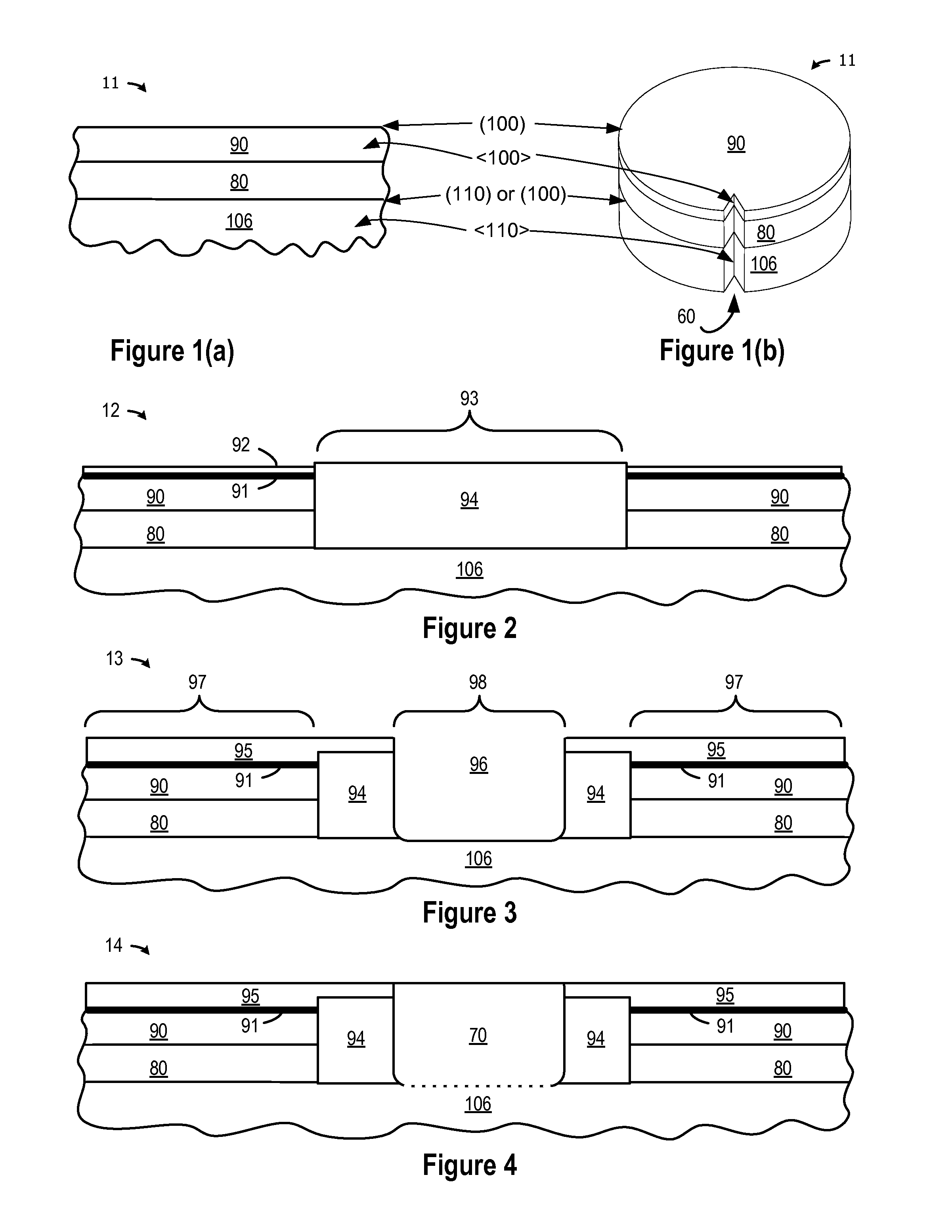

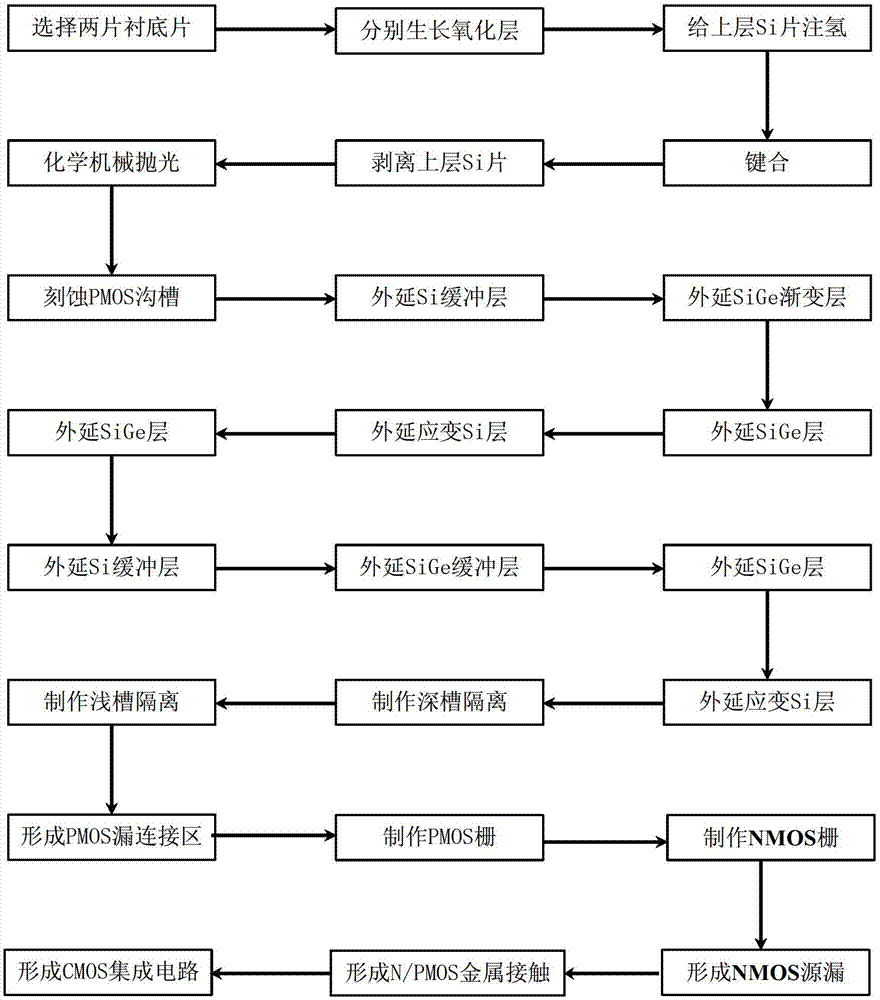

Mixed-crystal-face strain-Si vertical-channel CMOS (complementary metal oxide semiconductor) integrated device and preparation method

InactiveCN102820305BImprove mobilityImprove electrical performanceSolid-state devicesSemiconductor/solid-state device manufacturingPlanar channelP channel

The invention discloses a mixed-crystal-face strain-Si vertical-channel CMOS (complementary metal oxide semiconductor) integrated device and a preparation method. The preparation method includes: preparing an SOI (silicon on insulator) substrate, wherein an upper substrate is a crystal face (100) and a lower substrate is a crystal face (110); etching a deep trench in a PMOS (P-channel metal oxide semiconductor) active region at the temperature of 600-800 DEG C, selectively growing a strain Si PMOS active layer on a multi-layer structure of the crystal face (110), and preparing a compression strain PMOS of a vertical channel on the active layer; and etching a deep trench on an NMOS (N-channel metal oxide semiconductor) active region, selectively growing a strain Si NMOS active layer on a multi-layer structure of the crystal face (100), preparing a tensile strain NMOS of a planar channel on an epitaxial layer, and forming a mixed-crystal-face strain-Si CMOS integrated circuit with a conducting channel of 22-45nm. By the mixed-crystal-face strain-Si vertical-channel CMOS integrated device and the preparation method, the characteristics that migration rate of strain Si materials is higher than that of Si materials and the strain and the migration rate of the strain Si materials are anisotropic are fully used, and the mixed-crystal-face strain-Si CMOS integrated device and the mixed-crystal-face strain-Si CMOS integrated circuit which are excellent in performance are prepared on the basis of the SOI substrate.

Owner:XIDIAN UNIV

Integrated circuit and method of forming semiconductor structure

The embodiment of the invention provides an integrated circuit and a method for forming a semiconductor structure. The gate-all-around (GAA) nanowire transistor is provided with a plurality of nanowire channels which are vertically stacked, a first grid dielectric layer wrapping the nanowire channels and a first grid electrode wrapping the first grid dielectric layer. The GAA nanowire transistorshas a plurality of vertically stacked nanosheet channels, a second gate dielectric layer wrapping the nanosheet channels, and a second gate electrode wrapping the second gate dielectric layer. The planar device has a planar channel, a third gate dielectric layer on the planar channel, and a third gate electrode on the third gate dielectric layer. The first and second gate dielectric layers have the same thickness. The third gate dielectric layer is thicker than the first and second gate dielectric layers. The widths of the nanowire channels and the nanosheet channels are smaller than the widthof the planar channel.

Owner:TAIWAN SEMICON MFG CO LTD

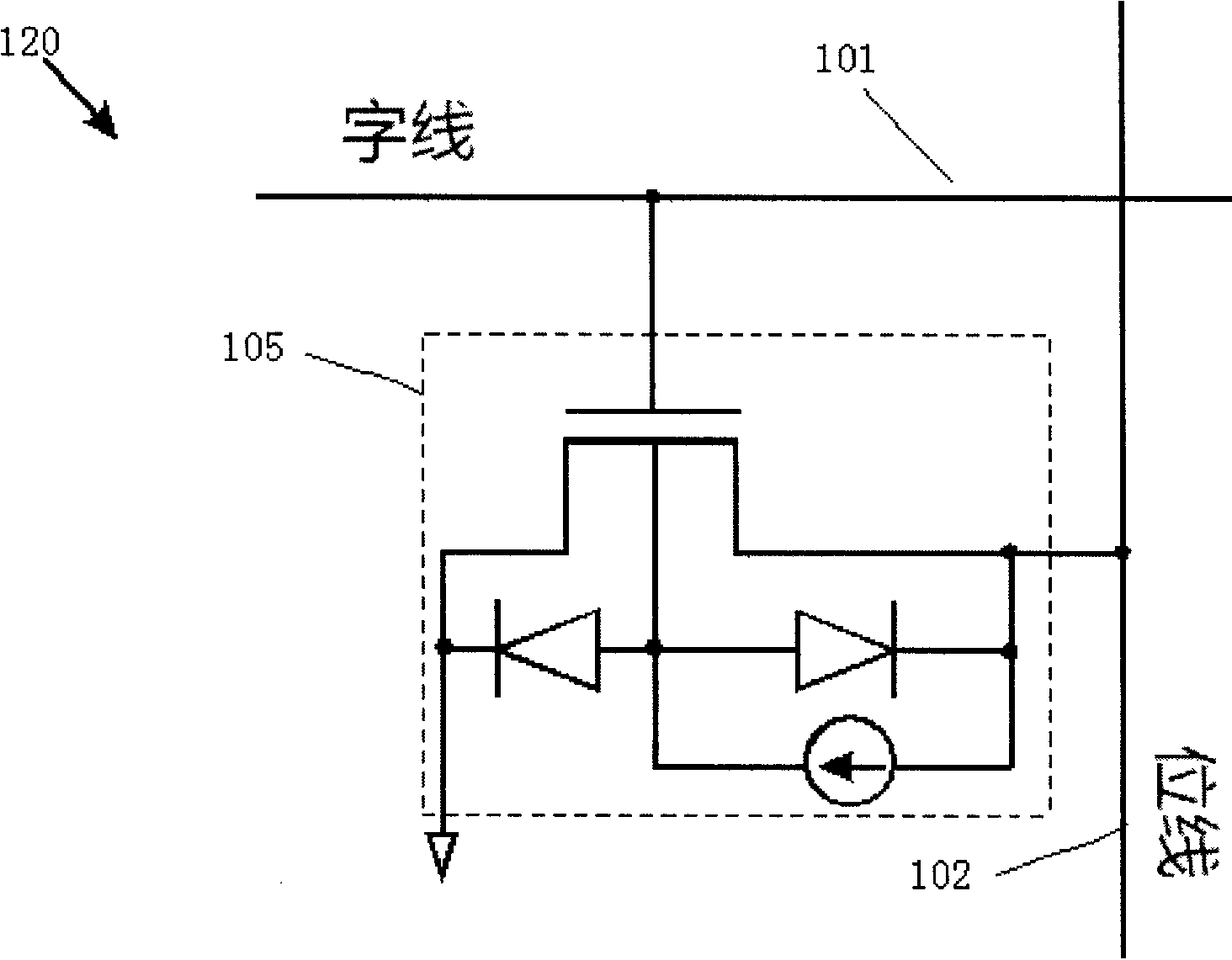

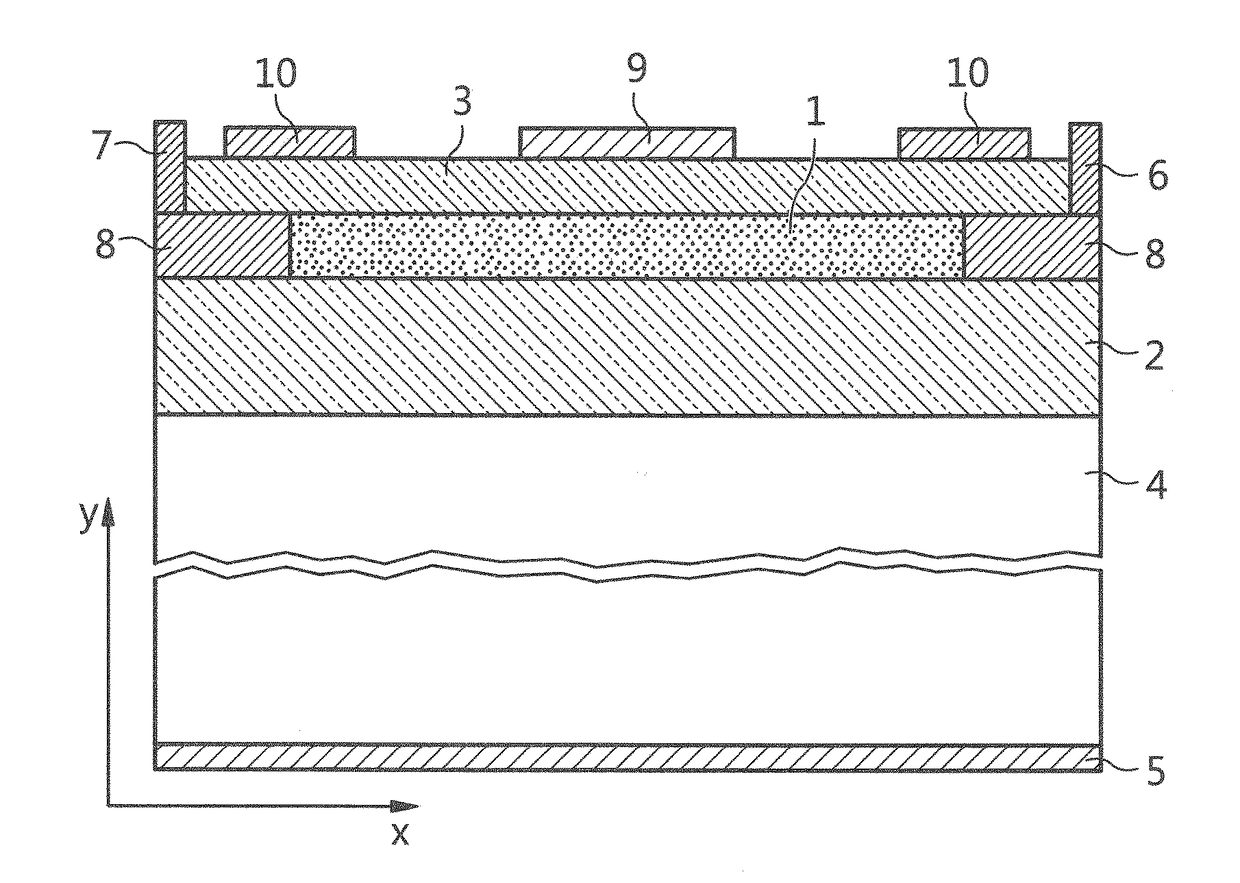

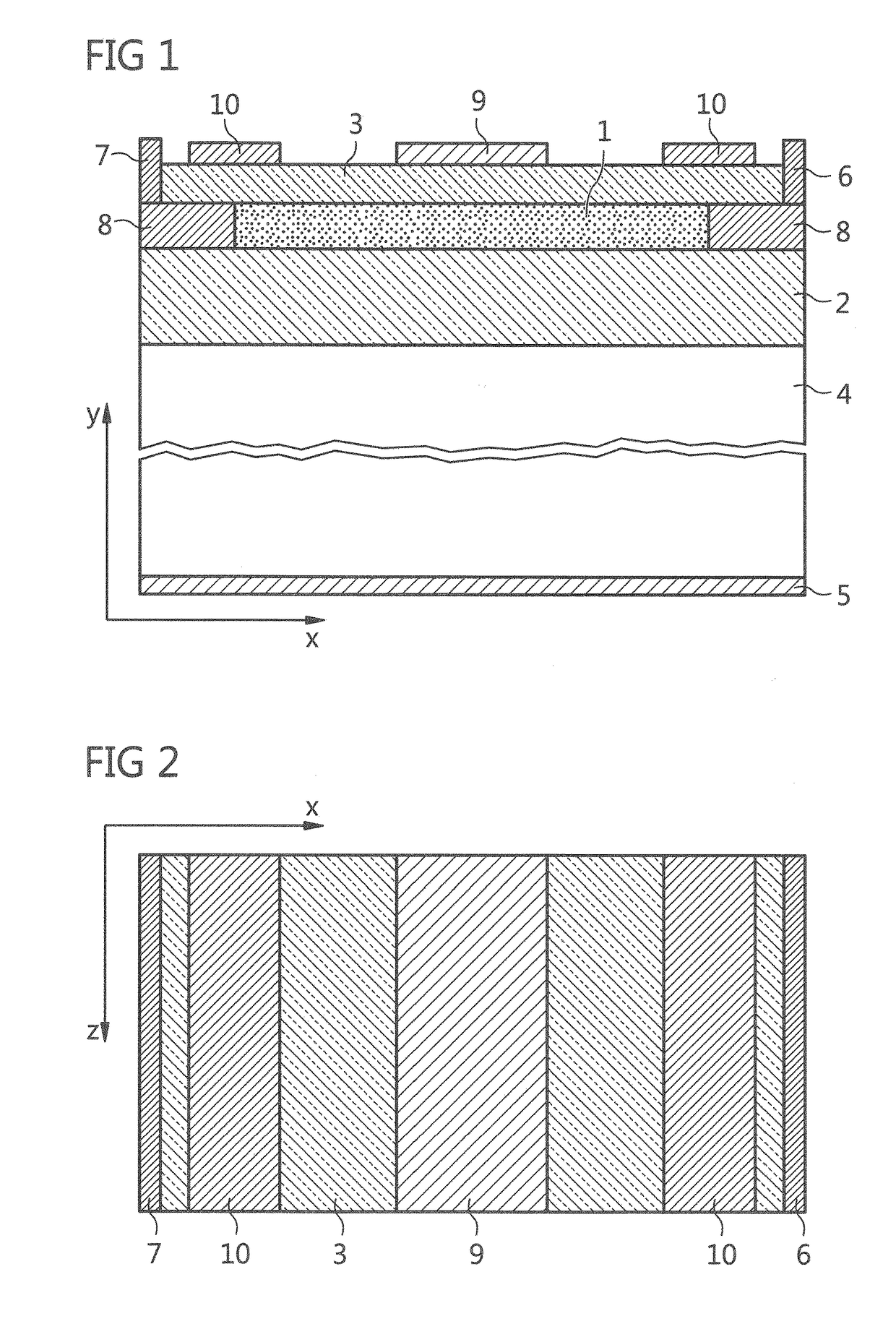

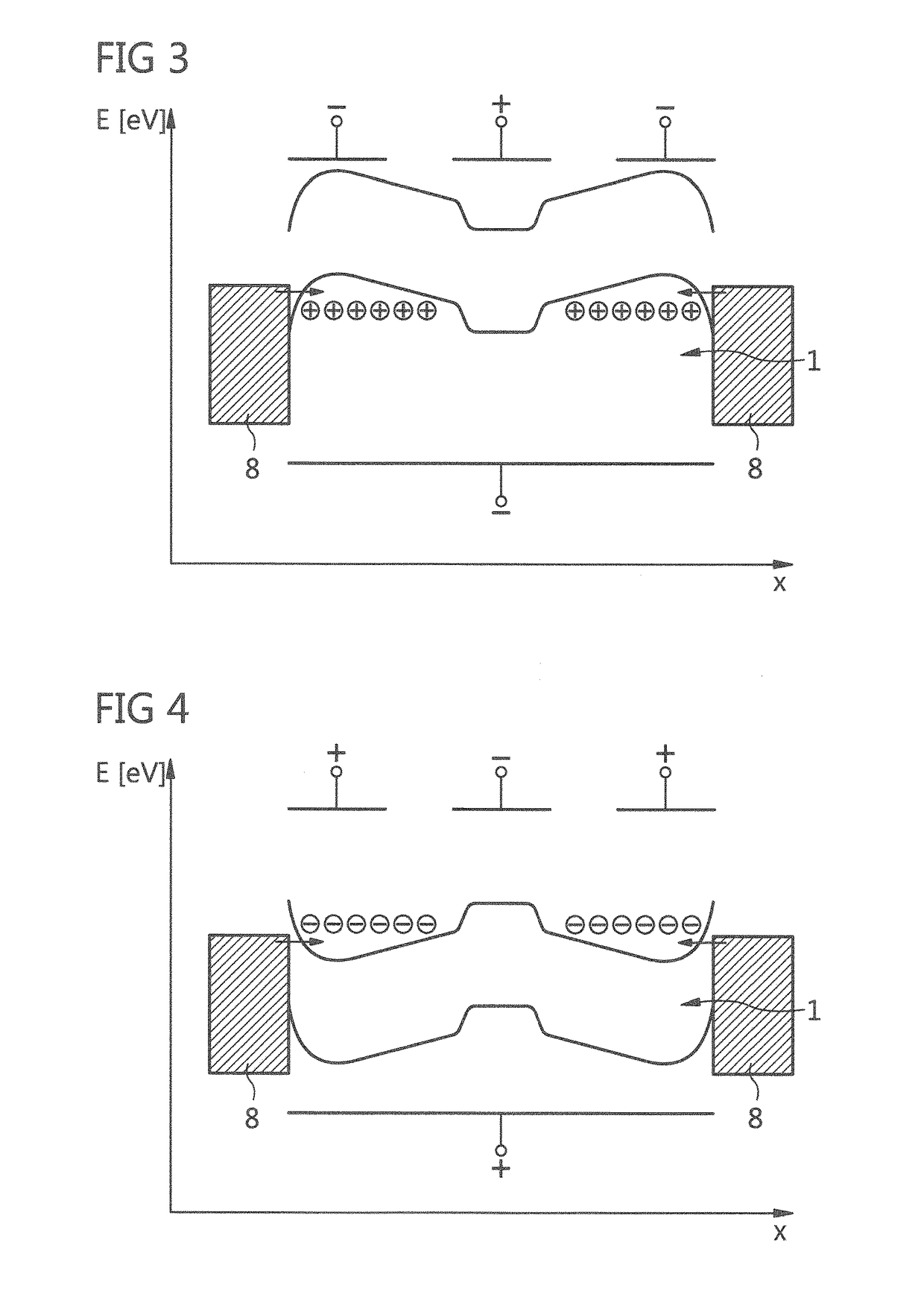

Method for operation of a field effect transistor arrangement

InactiveUS20180076323A1Fast switching timeReduce power consumptionTransistorElectricityInsulation layer

A method is provided for operation a field effect transistor arrangement, the field effect transistor arrangement having a planar channel layer including a semiconductor material, a whole surface of an underside of the planar channel layer being applied to a top side of an electrically insulating substrate layer and an upper side of the planar channel layer being covered by an electrically insulating electrode insulation layer, the arrangement having a source electrode disposed by a first side edge of the planar channel layer and having a drain electrode disposed by a second side edge of the planar channel layer, and having a control electrode arranged above the planar channel layer between the source electrode and the drain electrode, wherein an adjusting electrode is arranged on an underside of the substrate layer, and a first contact region between the source electrode and the planar channel layer and a second contact region between the drain electrode and the planar channel layer are each a Schottky barrier, wherein a respective barrier control electrode is arranged between the first contact region of the source electrode and the control electrode and between the second contact region of the drain electrode and the control electrode, the method including providing a first electric potential to the control electrode, providing a second electric potential to the barrier electrodes, and providing a third electric potential to the adjusting electrode.

Owner:TECH UNIV DARMSTADT

Semiconductor memory device and manufacturing method thereof

ActiveCN102169882BImprove compatibilityProcess stabilitySolid-state devicesSemiconductor/solid-state device manufacturingPlanar channelEngineering

The invention discloses a semiconductor memory device, which comprises a source, a drain, a floating gate region, a control gate, a planar channel region and a gate controlled diode, wherein the gate controlled diode is used for connecting the floating gate region and the drain; and in the semiconductor memory device, the floating gate region is used for memorizing information, the gate controlled diode is used for connecting a floating gate and a substrate, and the floating gate is charged or discharged by the gate controlled diode. The semiconductor memory device is manufactured by using a self-alignment process, and the process is simple and stable; and in the invention, manufacturing of a logic circuit and a flash memory device is compatible by using a planar channel structure.

Owner:SUZHOU ORIENTAL SEMICONDUCTOR CO LTD

Solid-state membrane module

InactiveUS9067172B1Improve component reliabilityRelieve pressureSemi-permeable membranesOxygen/ozone/oxide/hydroxidePorosityPlanar channel

A module for separating oxygen from an oxygen-containing gaseous mixture comprising planar solid-state membrane units, each membrane unit comprising planar dense mixed conducting oxides layers, planar channel-free porous support layers, and one or more planar intermediate support layers comprising at least one channeled porous support layer. The porosity of the planar channeled porous support layers is less than the porosity of the planar channel-free porous support layers.

Owner:AIR PROD & CHEM INC