A method of manufacturing a planar channel semi-floating gate device

A semi-floating gate device and planar channel technology, which is applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problems of metal gate damage and poor high temperature resistance of metal gate, so as to avoid damage, process The process is simple and the effect of reducing production costs

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

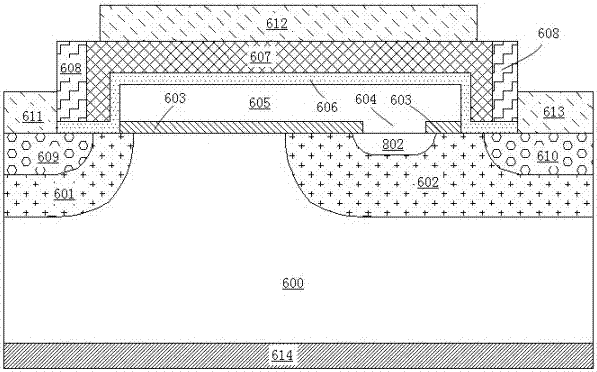

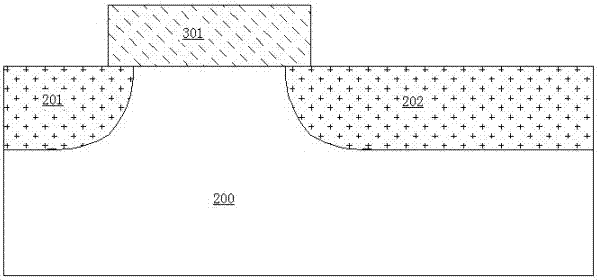

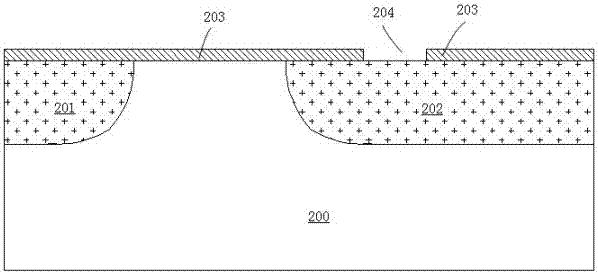

[0038] The present invention will be further described in detail below in conjunction with the accompanying drawings and specific embodiments. In the drawings, the thicknesses of layers and regions are exaggerated for convenience of illustration, and the shown sizes do not represent actual sizes. The referenced figures are schematic illustrations of idealized embodiments of the invention, and the illustrated embodiments of the invention should not be construed as limited to the particular shapes of regions illustrated in the figures but are to include resulting shapes, such as manufacturing-induced deviations. For example, the curves obtained by etching are usually curved or rounded, but in the embodiment of the present invention, they are all represented by rectangles. The representation in the figure is schematic, but this should not be considered as limiting the scope of the present invention. Meanwhile, in the following description, the term substrate used can be understoo...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More