Semiconductor device and preparation method thereof

A semiconductor and device technology, applied in the field of semiconductor devices and their preparation, can solve the problems of reduced threshold voltage stability of memory arrays, lengthy process steps and process steps, affecting component performance and reliability, etc., so as to reduce device area and increase Effective channel length, effect of overcoming short channel effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

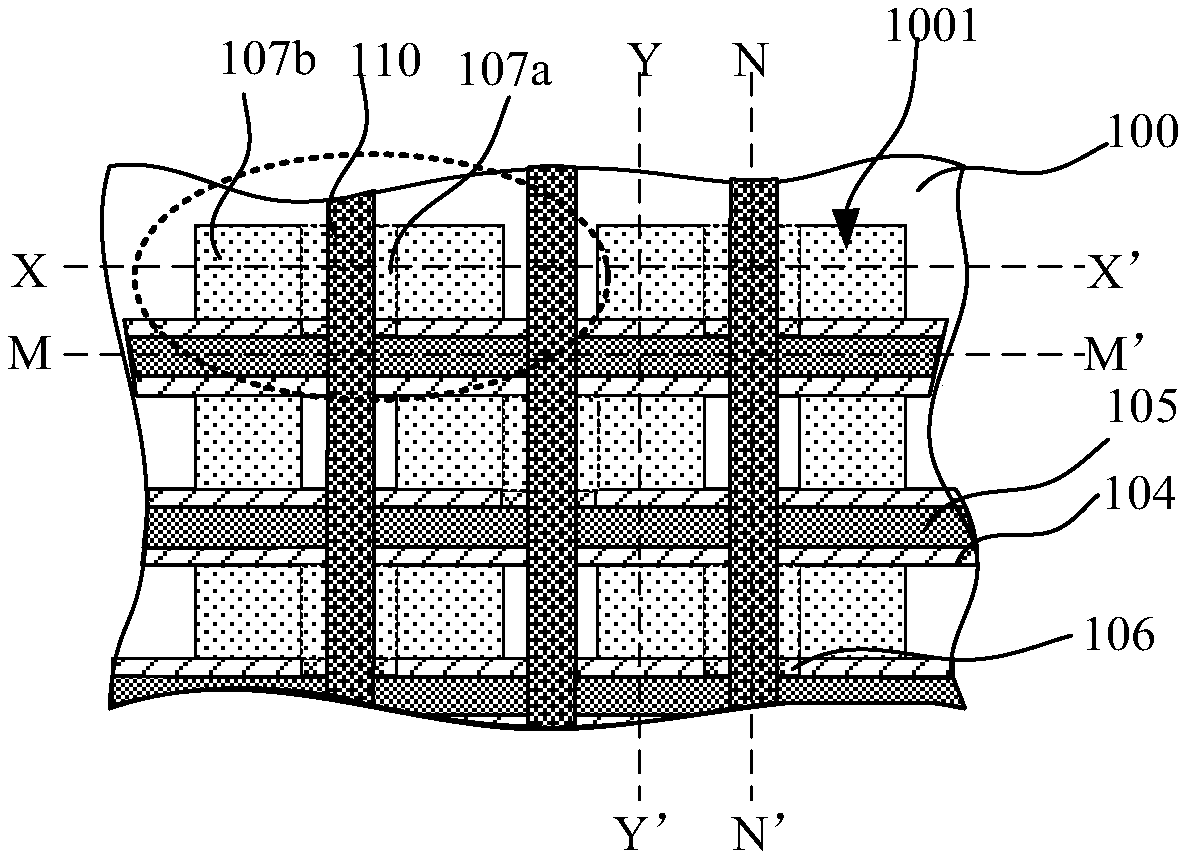

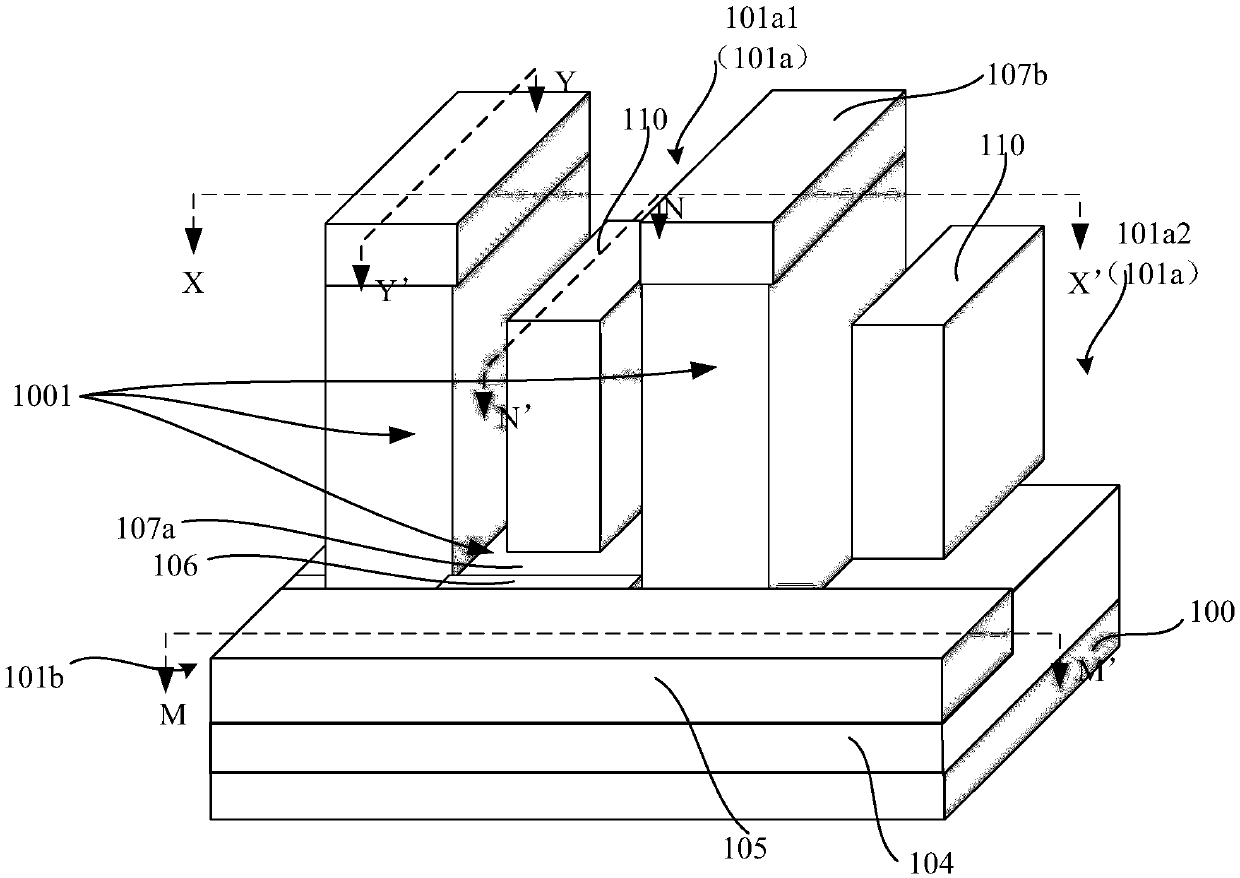

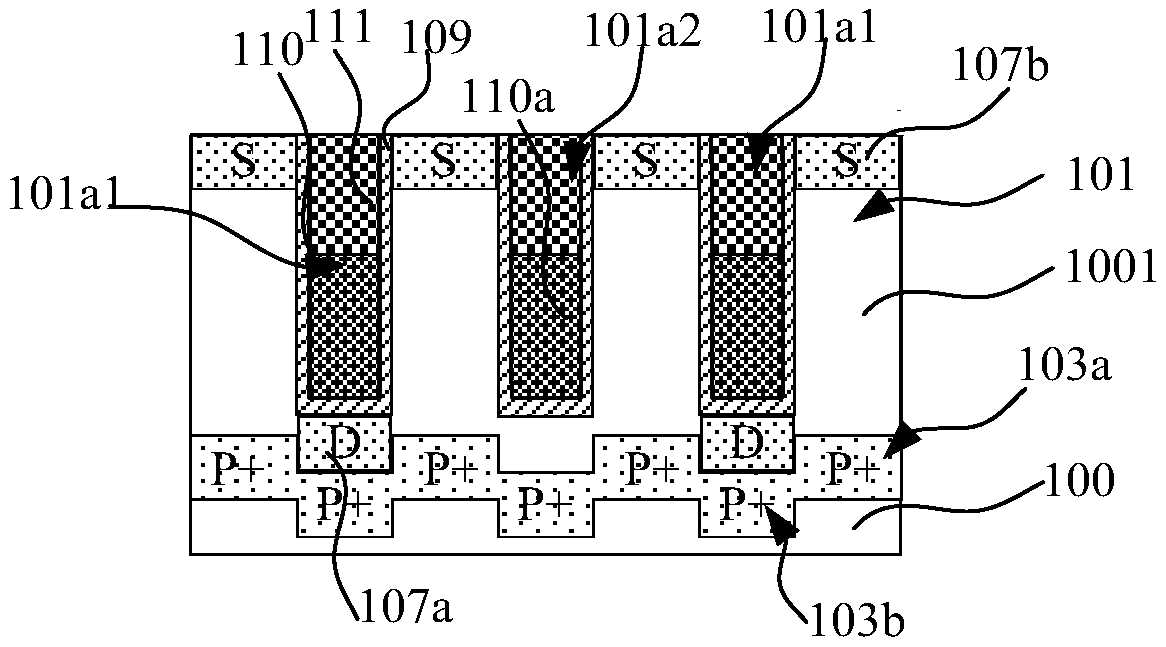

[0080] In order to make the purpose and features of the present invention more obvious and understandable, the technical solutions of the present invention will be described in detail below in conjunction with the accompanying drawings. However, the present invention can be implemented in different forms and should not be limited to the described embodiments. It should be noted that the "semiconductor substrate on both sides of the first trench" herein refers to the region where the first trench does not intersect with the second trench (that is, the area where the first trench does not intersect with the second trench). The semiconductor substrate on both sides of the area other than the intersection with the second trench); the "semiconductor substrate at the bottom of the first trench" herein means that the first trench is not connected to the first trench. The region where the two trenches intersect the bottom of the semiconductor substrate. Furthermore, it should be readi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More