Method for increasing length of effective channel of PMOS

A technology of channel length and area, applied in the direction of electrical components, semiconductor/solid-state device manufacturing, circuits, etc., to increase the effective communication length of PMOS and benefit the cost

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

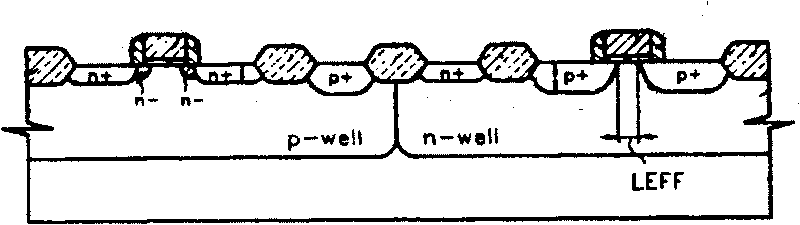

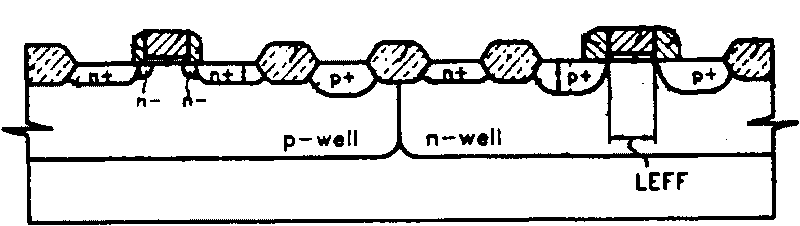

Image

Examples

Embodiment Construction

[0021] The present invention will be further described in detail below in conjunction with the accompanying drawings and specific embodiments.

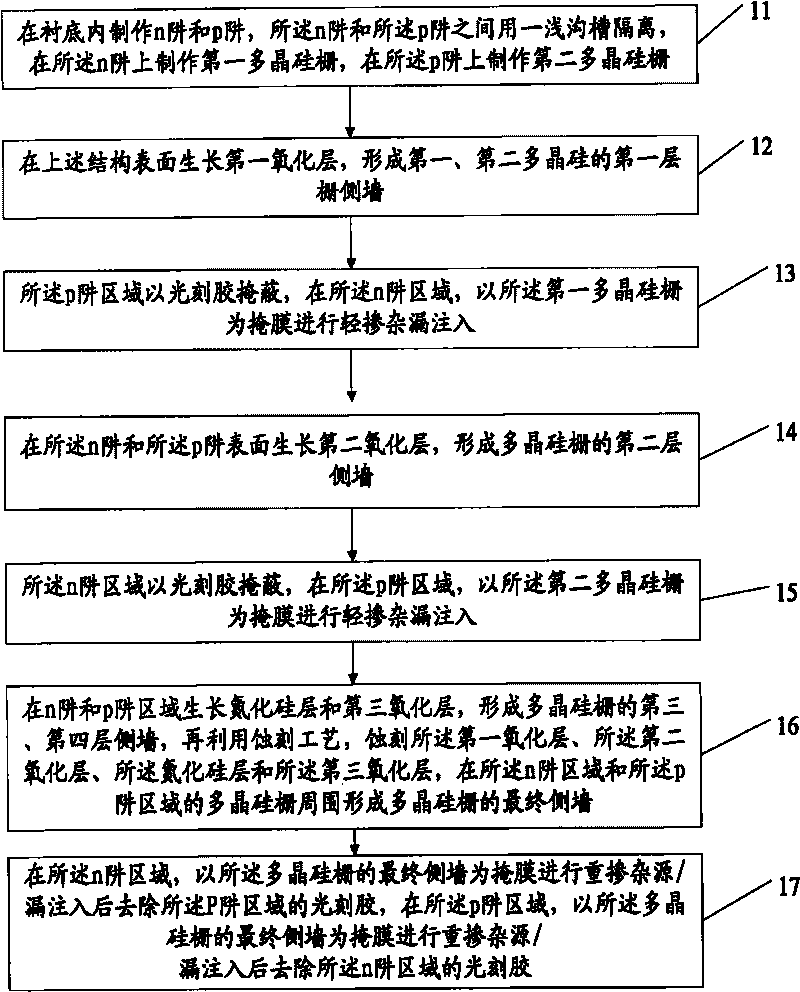

[0022] Please refer to image 3 , image 3 It is a schematic flow chart of a method for increasing the PMOS effective channel length of the present invention, comprising the following steps:

[0023] Step 11: fabricating n well and p well in the substrate, using a shallow trench isolation between the n well and the p well, fabricating a first polysilicon gate on the n well, and forming a first polysilicon gate on the p well Fabrication of the second polysilicon gate shallow trench isolation on the well is mainly divided into three steps, namely trench etching, oxide filling and oxide planarization. The fabrication of the gate structure in the transistor is the most critical step in the process, because It includes the thermal growth of the thinnest gate oxide layer and the imprinting and etching of the polysilicon gate. The basic pr...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More