Second level cache and kinetic energy switch access method

A cache, kinetic energy technology, applied in energy-saving computing, memory systems, energy-saving ICT and other directions, can solve problems such as current consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

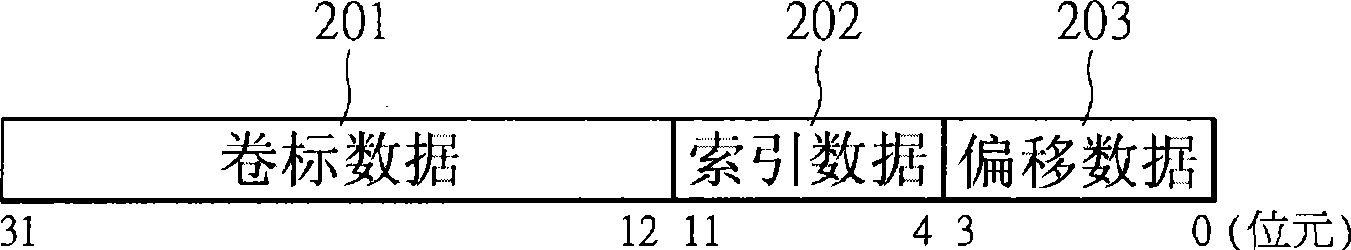

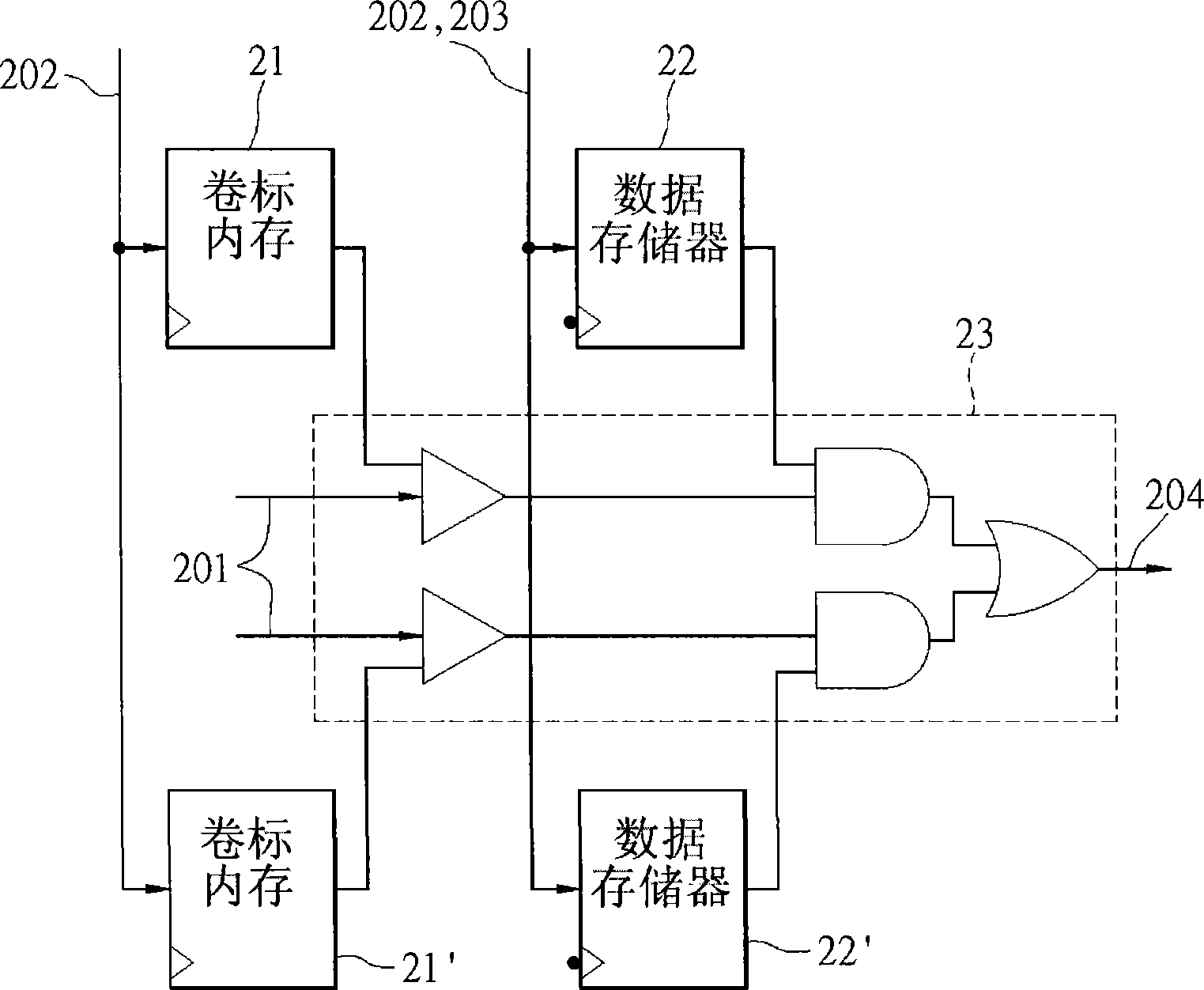

[0036] Please also refer to Figure 2A and Figure 2B , are respectively a schematic diagram of the data address packet of the central processing unit and a schematic diagram of the circuit architecture of an embodiment of the secondary cache architecture of the present invention. exist Figure 2A Among them, a central processing unit generates a 32-bit (bits) data address packet as a follow-up description, but it can also be changed according to its actual required bit data; the data address packet contains a label data (20 bits ) 201, an index data (8 bits) 202 and an offset data (4 bits) 203.

[0037] When the central processing unit processes data, it will first look for it in the cache. If the data is temporarily stored here because it has been read before, it does not need to read the data from the huge memory for a long time. And as Figure 2B As shown, the present invention provides a second-level high-speed cache (L2 Cache) 2 architecture, which is mainly when the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More