BSIM3 HCI reliability model used in MOSFET electrical simulation

A reliability and model technology, applied in special data processing applications, electrical digital data processing, instruments, etc., can solve problems such as acceleration, reliability problems, circuit function failures, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0035] In order to better understand the technical content of the present invention, specific embodiments are given together with the attached drawings for description as follows.

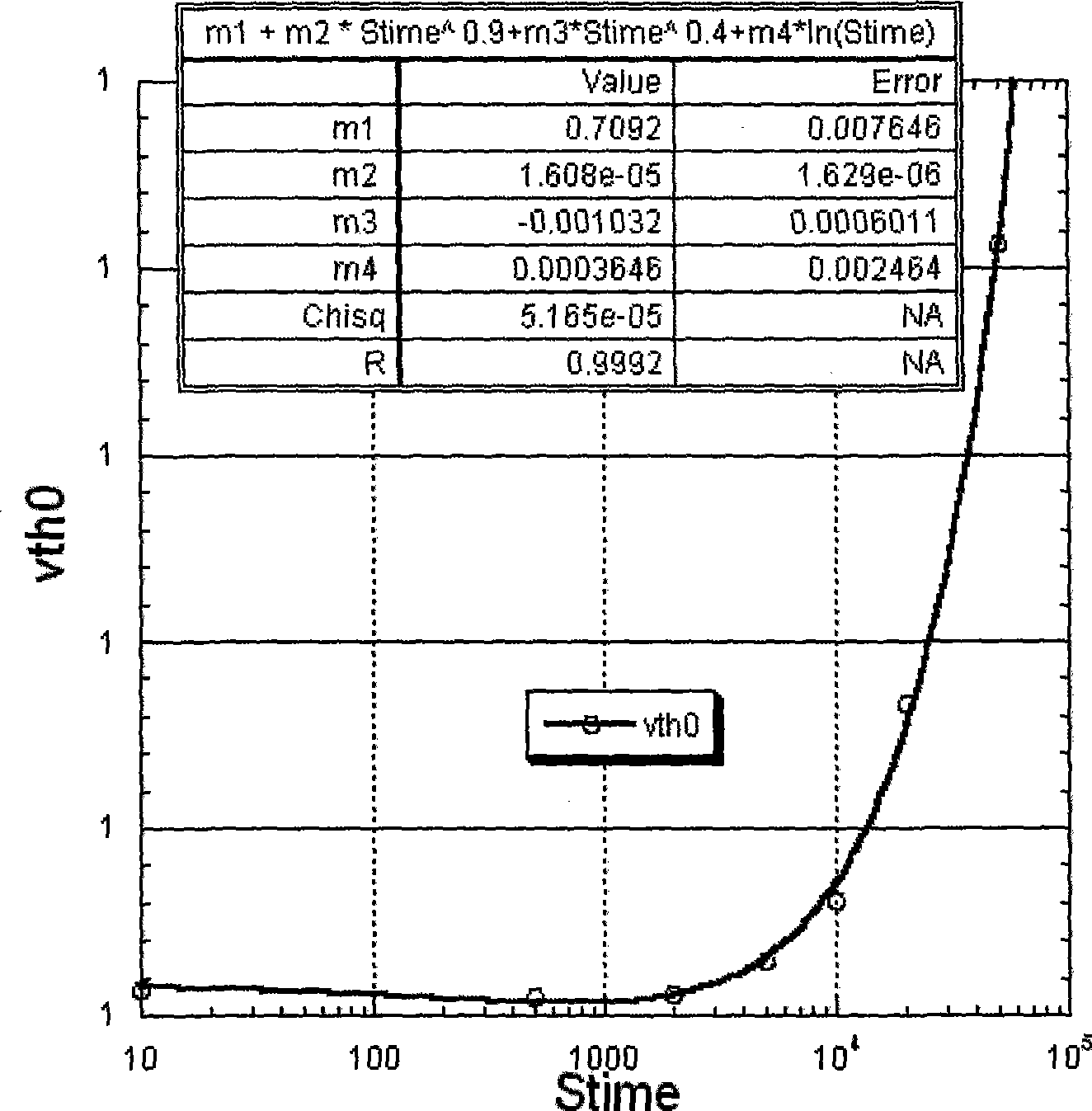

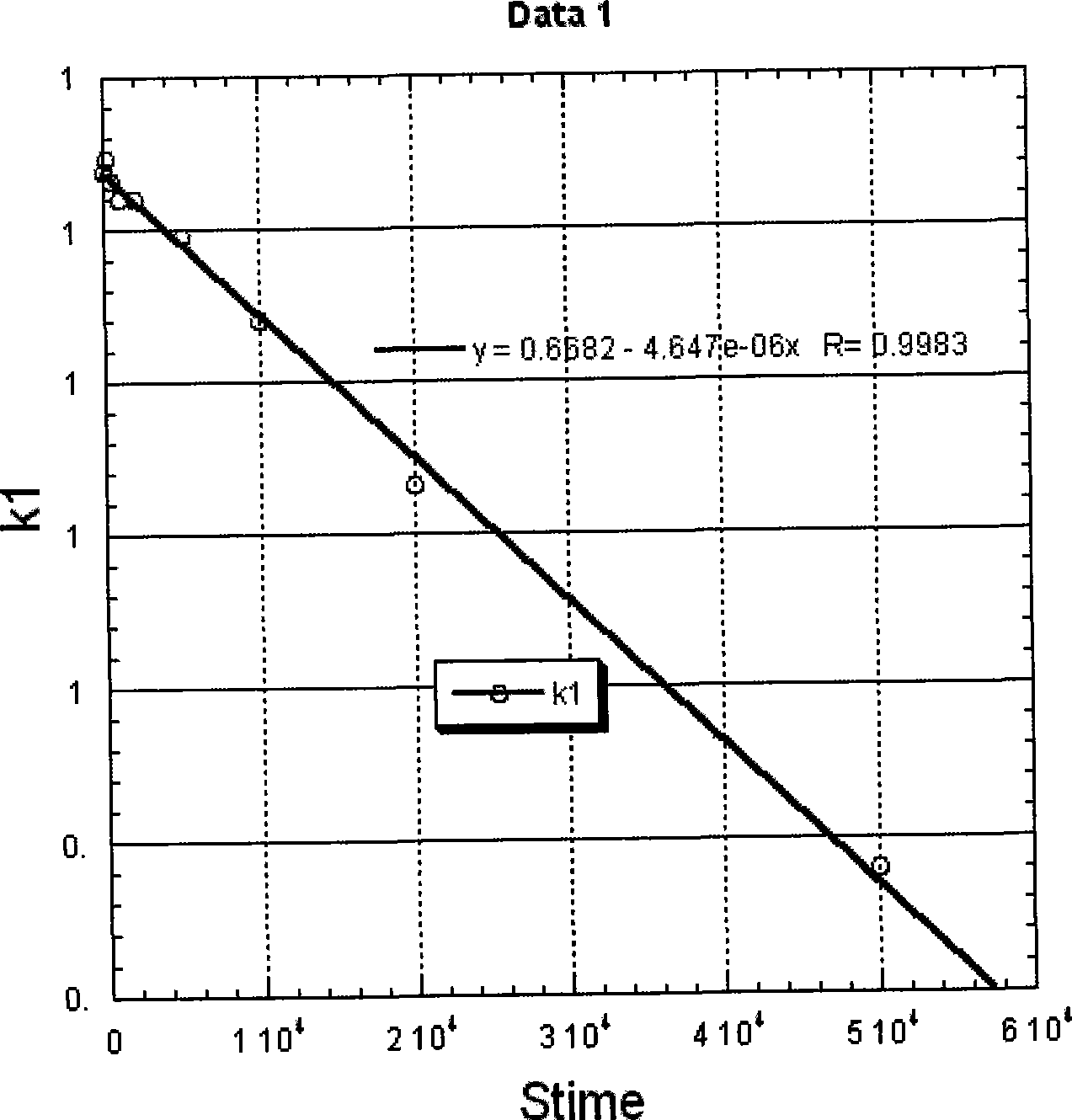

[0036] The present invention provides a BSIM3 HCI reliability model of 0.35μm-0.5μm standard process MOSFET, which has clear physical meaning and high accuracy, and can simulate the electrical characteristics of MOSFET under certain bias conditions and different bias times .

[0037] In the following, an example will be used to further describe in detail how to apply the BSIM3HCI reliability model of the 0.5 μm standard technology MOSFET of the present invention.

[0038] Please refer to figure 1 , figure 1 It is a structural block diagram of the BSIM3 HCI reliability model. Such as figure 1 As shown, the BSIM3 HCI reliability model of the 0.5 μm standard process MOSFET of the present invention is affected by the hot carrier degradation effect by 7 BSIM3SPICE model parameters, and the formula t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More