Network-on-chip router having adaptive routing capability and implementing method thereof

An on-chip network and router technology, which is applied in the field of on-chip multi-processor inter-core communication, can solve problems affecting performance, resources cannot be fully utilized, data packet blocking, etc., and achieve the effects of improving efficiency, facilitating efficient interaction, and reducing blocking

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

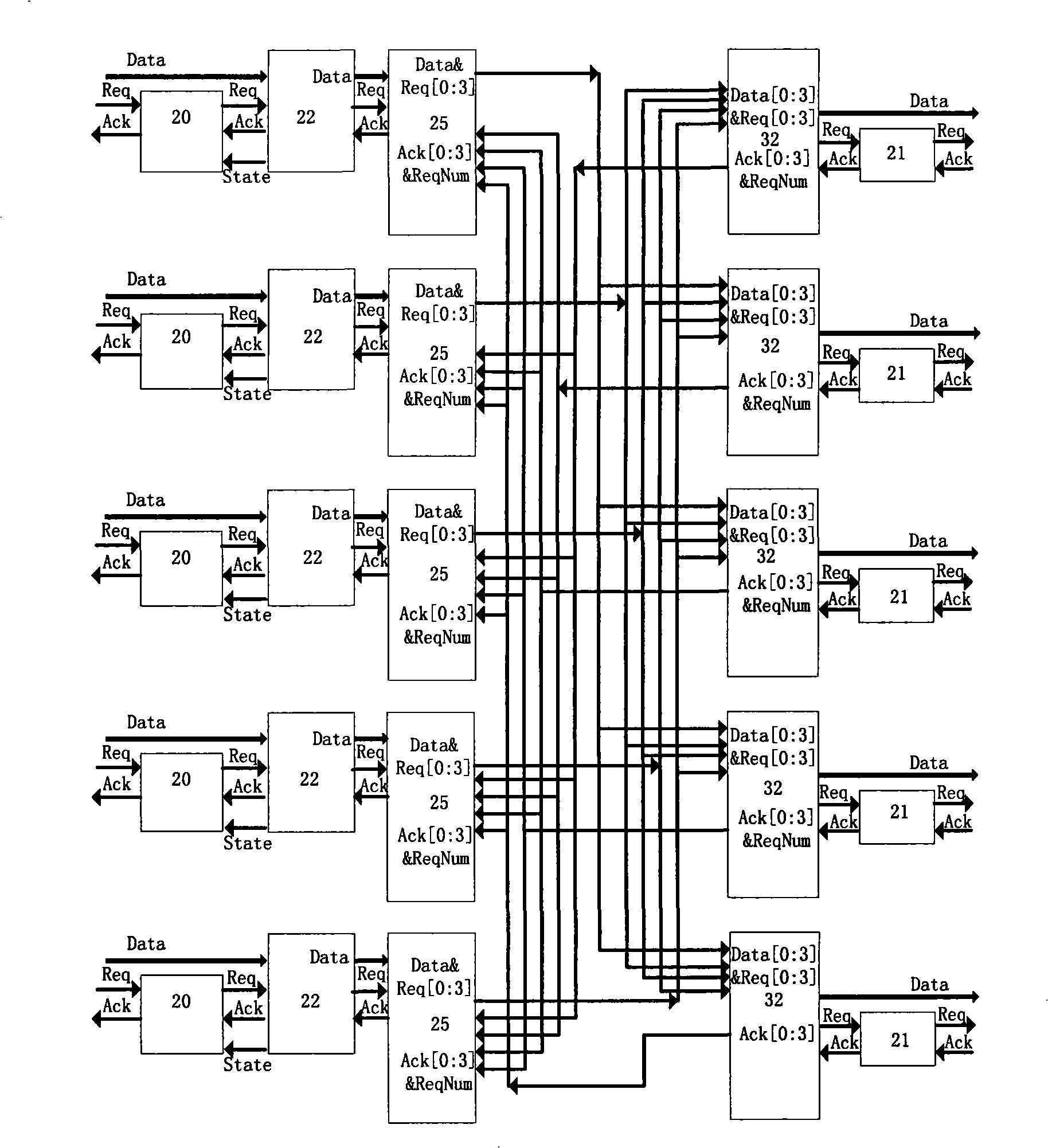

[0029] The invention proposes an on-chip router design method with self-adaptive routing capability, which is used to construct an on-chip network communication system. In the process of designing the router, such as figure 1 structure shown. The invention designs the processes of receiving, buffering, analyzing routing, forwarding and the like of the data packets respectively.

[0030] Packet format used

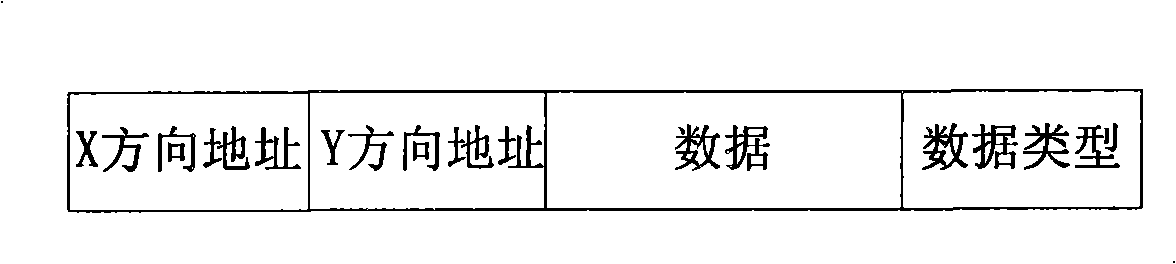

[0031] The following data packet format is adopted in the present invention, as figure 2 As shown, it includes four parts: address in X direction, address in Y direction, data and data type. Wherein, the data width of the X and Y addresses determines the size of the network that the current router can support. For example, if the data width of X and Y is 4, then the largest network supported by the current router is 16×16. Data and data types determine the content and properties of the data communicated between endpoints.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More