Signal delay circuit

A signal delay and signal technology, applied in the direction of electrical components, pulse processing, single output arrangement, etc., can solve the problems of increased transmission delay, etc., and achieve the effect of reduced design complexity, high delay time resolution, and less redesign time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

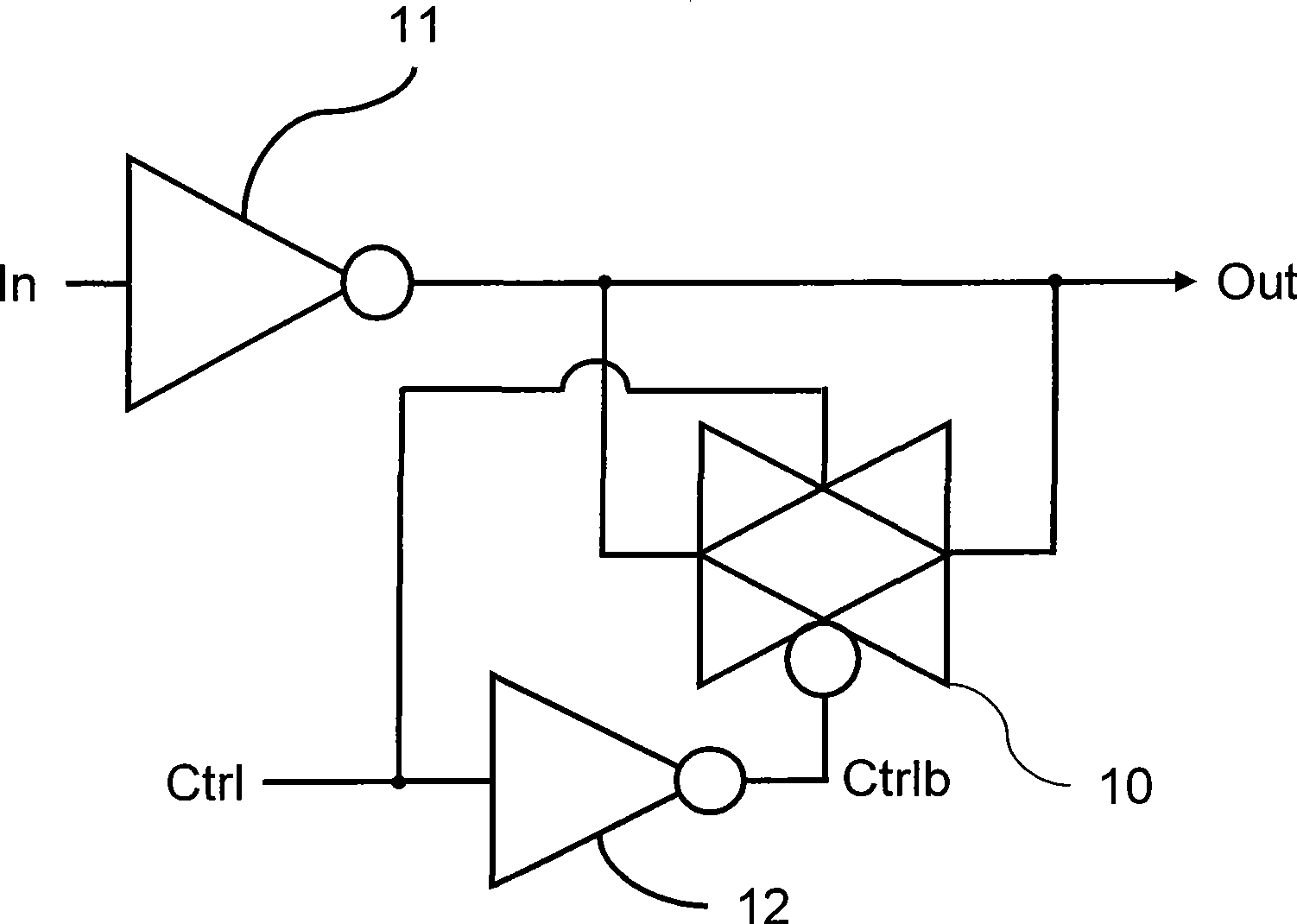

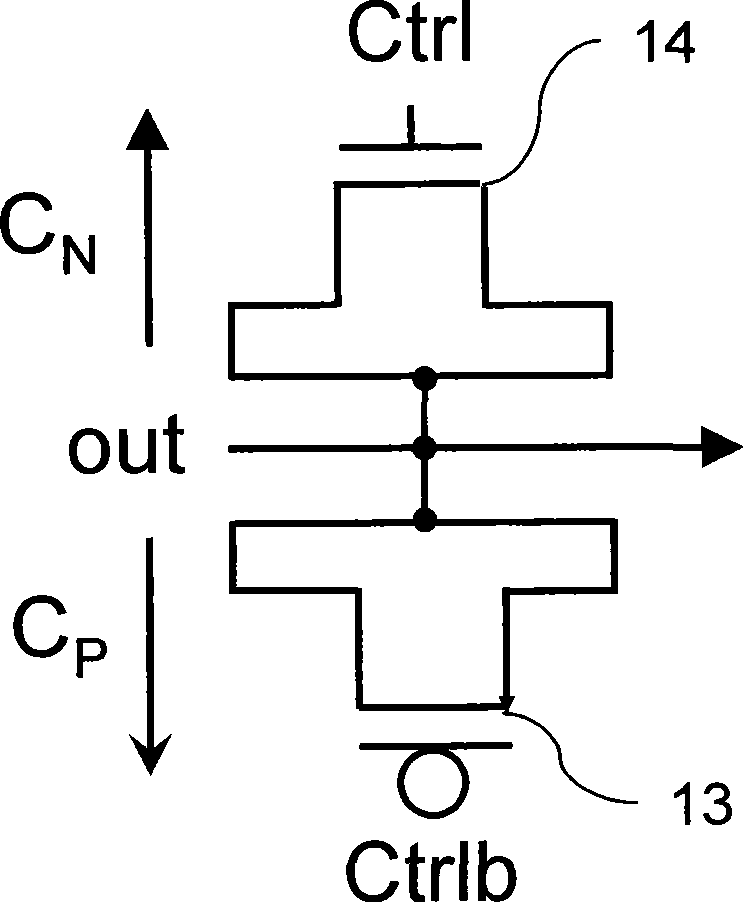

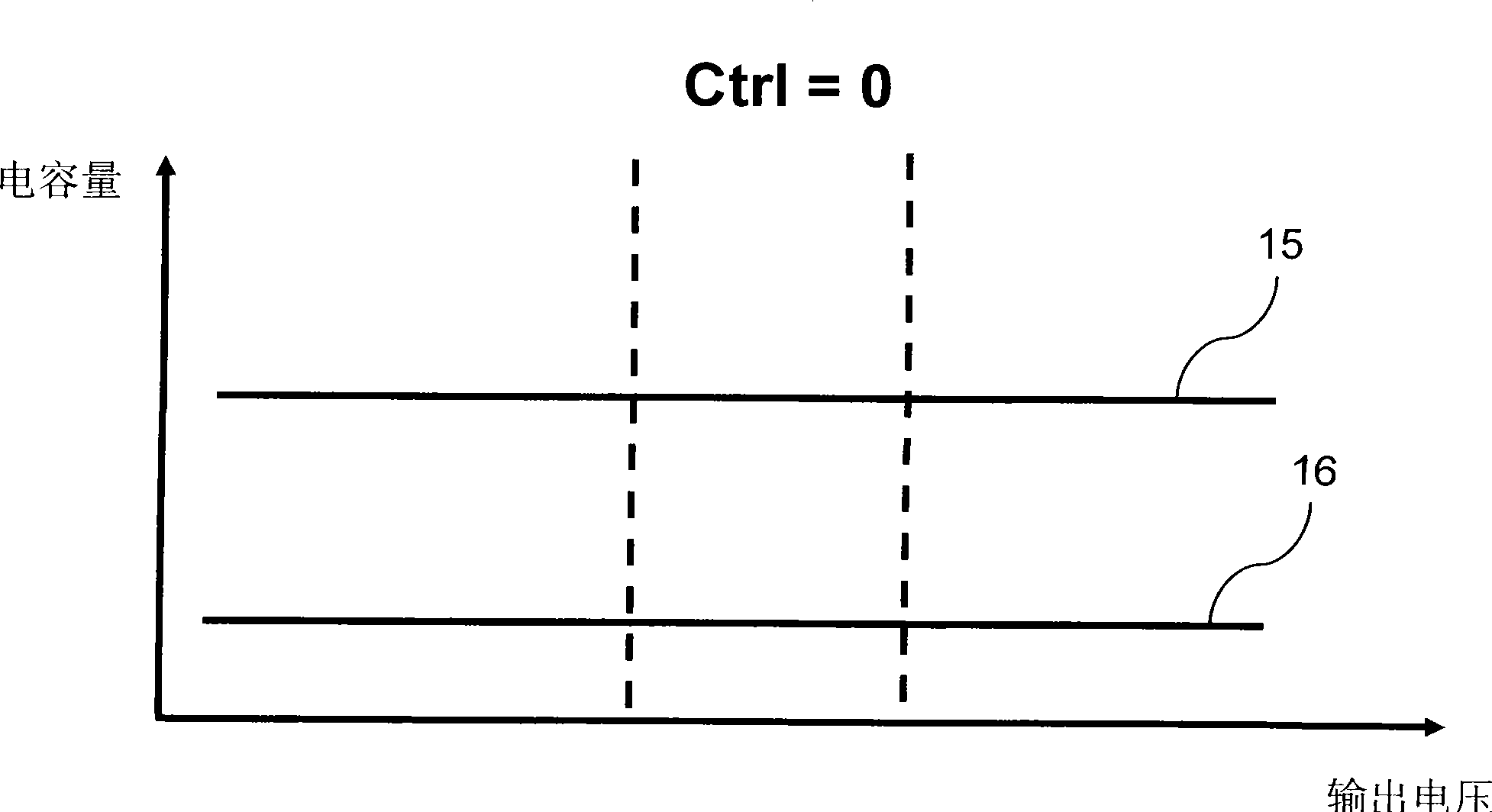

[0140] Please refer to Figure 7A and Figure 7B , is a schematic diagram of a signal delay circuit disclosed in an embodiment of the present invention. The signal delay circuit disclosed in the embodiment consists of a capacitive load element, in this embodiment a logic gate 100 with three input terminals. This logic gate 100 is composed of at least three switches 105 , 106 , 107 . In an embodiment, transistors can be used as the switches 105 , 106 , 107 . The resistors in the figure represent the equivalent parasitic resistances 101 , 102 , 103 , 104 of other active components or passive components in the logic gate. The voltages V1 and V2 can be power supply voltage or ground voltage.

[0141] exist Figure 7A In the illustrated embodiment, the switch 105 receives a first signal Sin, the switch 106 receives a second signal Inb, and the switch 107 receives a control signal Ctrl. The first signal Sin and the second signal Sinb are mutually inversion signals. In an embo...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com