Semiconductor encapsulation structure with pins on chip

A semiconductor and chip technology, applied in the direction of semiconductor devices, semiconductor/solid-state device parts, electric solid-state devices, etc., to achieve the effect of not easy to tilt and tilt, improve the anti-stress effect, and strengthen the locking ability.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 Embodiment

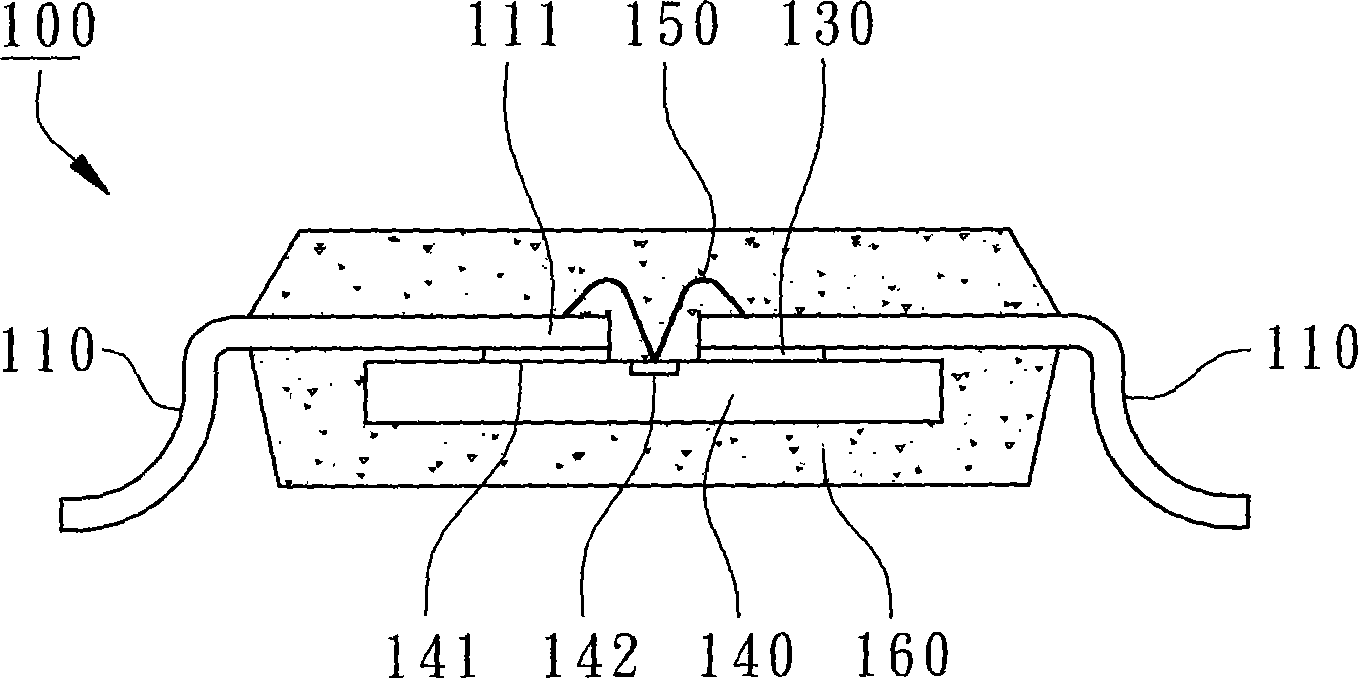

[0054]According to a first embodiment of the present invention, a lead-on-chip (LOC, Lead-On-Chip) semiconductor package structure is disclosed. Wherein, the "pins on the chip" referred to here means that the pins of the lead frame are attached to the active surface of the chip, so as to achieve the effect of carrying the chip during the packaging process. Figure 4 A schematic cross-sectional view along the pin centerline is constructed for the semiconductor package. Figure 5 is a schematic plan view of a lead frame suitable for the semiconductor package configuration. Figure 6 It is a schematic plan view of the leadframe after die bonding and wire bonding. Figure 7 for Figure 6 A zoomed-in view of a feature in a leadframe prior to wire bonding. Figure 8 A schematic partial cross-sectional view cut along the lead fingers is constructed for the semiconductor package. in, Figure 5 can be with figure 2 Compared with the known lead frames for feature differences, F...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More