Wafer-level packaging of chip and packaging method thereof

A wafer-level packaging and packaging method technology, applied in electrical components, electrical solid-state devices, circuits, etc., can solve the problems affecting the bonding quality of the whole chip, the decline in yield, and the inability to achieve sealing.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

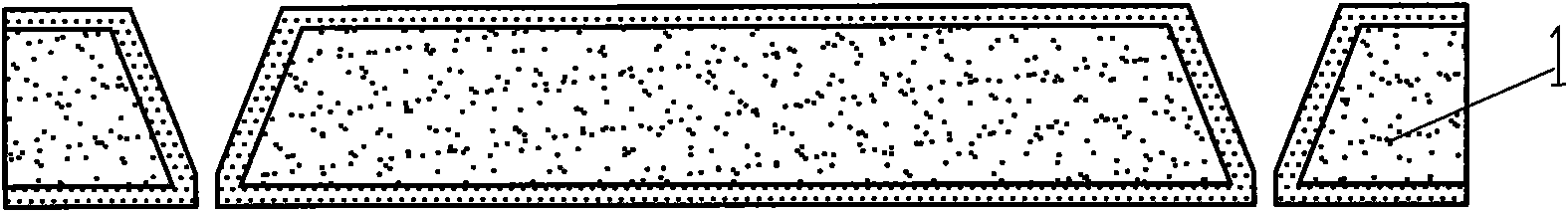

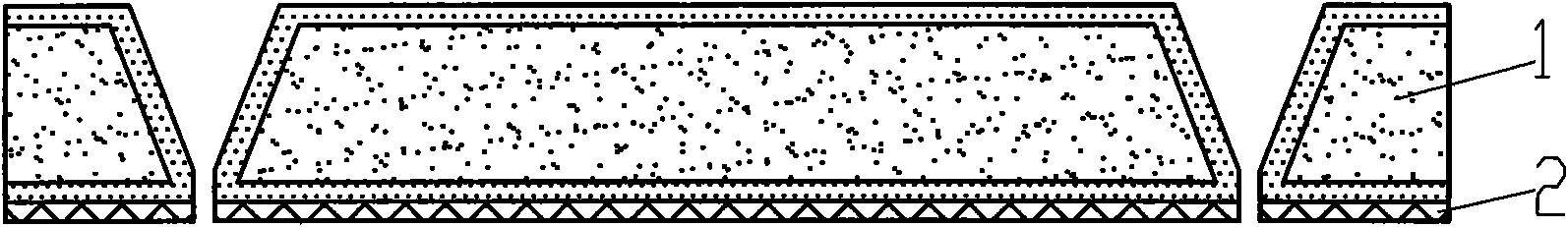

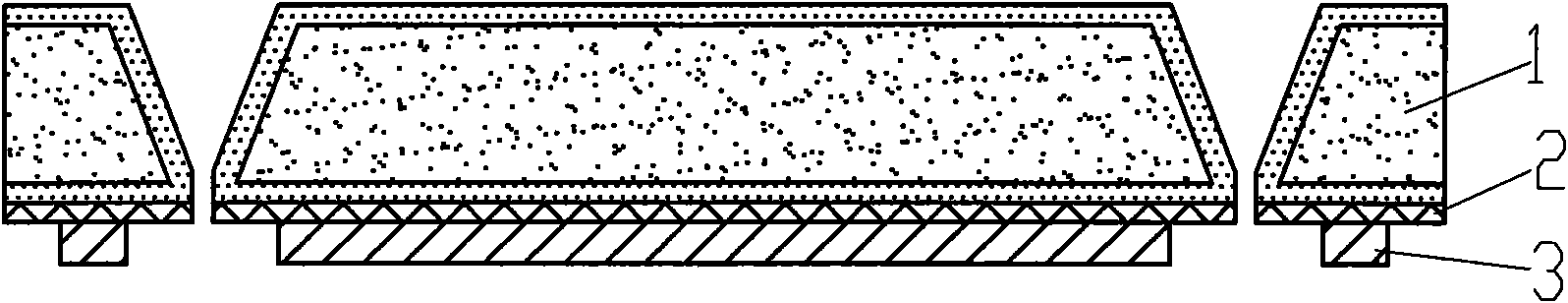

[0048] Example 1: Figure 3-2 As shown, the wafer-level package of the chip is packaged by an upper cover wafer and a lower cover wafer made of silicon wafers. There is an upper sealing ring on the upper cover disc, and a lower sealing ring matching the lower sealing ring on the lower cover disc; the upper sealing ring and the lower sealing ring are eutectic or hot-pressed Implement encapsulation.

[0049] The wafer-level packaging of this chip uses thermocompression bonding of tin-lead and gold for wafer-level packaging. Concrete process steps are as follows:

[0050] 1. Preparation of the upper cover wafer: prepare the upper cover wafer 1 with or without through holes having the same size as the wafer to be packaged. The material of the top cover wafer can be silicon wafer, glass wafer or ceramic wafer, etc. There is no limit to the way of realizing the through hole, and it can be etching, laser drilling, frosting and other means. In this embodiment, a silicon wafer with...

Embodiment 2

[0064] Example 2: Figure 5-2 As shown, the wafer-level package of the chip is packaged by an upper cover wafer and a lower cover wafer made of silicon wafers. A bonding layer of BCB material is coated on the upper cover disc, and a lower sealing ring matching the lower sealing ring is provided on the lower cover disc; the lower sealing ring is extruded to the bonding layer to realize packaging.

[0065] The wafer-level packaging of this chip uses cold-compression bonding of BCB and gold for wafer-level packaging. The specific process steps are as follows:

[0066] 1. Preparation of the top cover wafer: prepare a top cover wafer with or without through holes of the same size as the wafer to be packaged. The material of the top cover wafer can be silicon wafer, glass wafer or ceramic wafer, etc. There is no limit to the way of realizing the through hole, and it can be etching, laser drilling, frosting and other means. In this embodiment, a silicon wafer with a thickness of 3 ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More