Computer interlocking system code bit-level redundancy method

A technology of computer interlocking and system code, applied in the redundancy of hardware for data error detection, interlocking device between switch and signal, transportation and packaging, etc., can solve the problem of not being able to complete normal work and affecting work efficiency. and other problems to achieve the effect of eliminating sudden shutdown, improving reliability, and alleviating reliability reduction.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

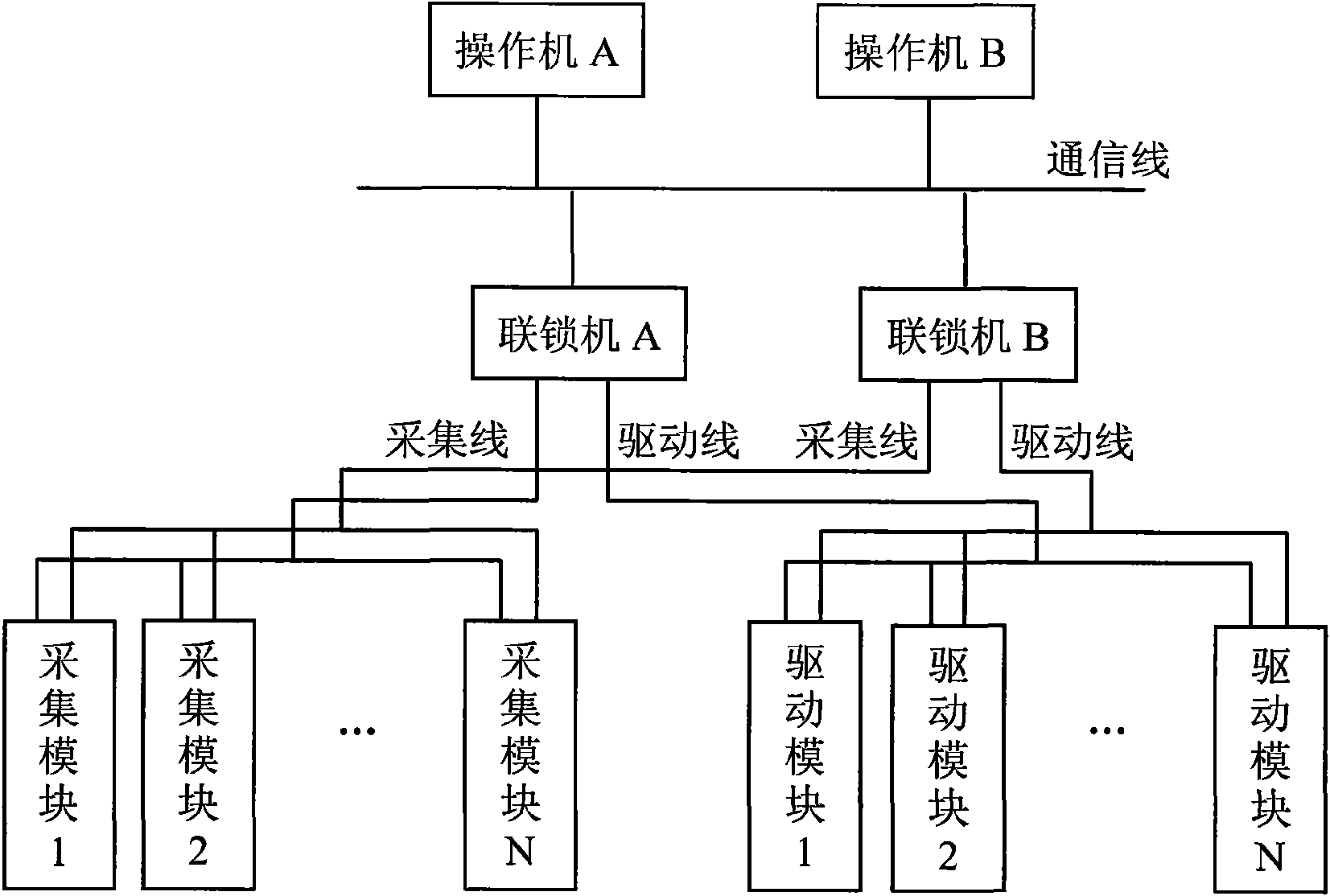

[0027] Hereinafter, taking the interlocking processing subsystem (IPS) of the iLOCK system as an example, the specific embodiments of the present invention will be described in detail in conjunction with the accompanying drawings.

[0028] output parallel control

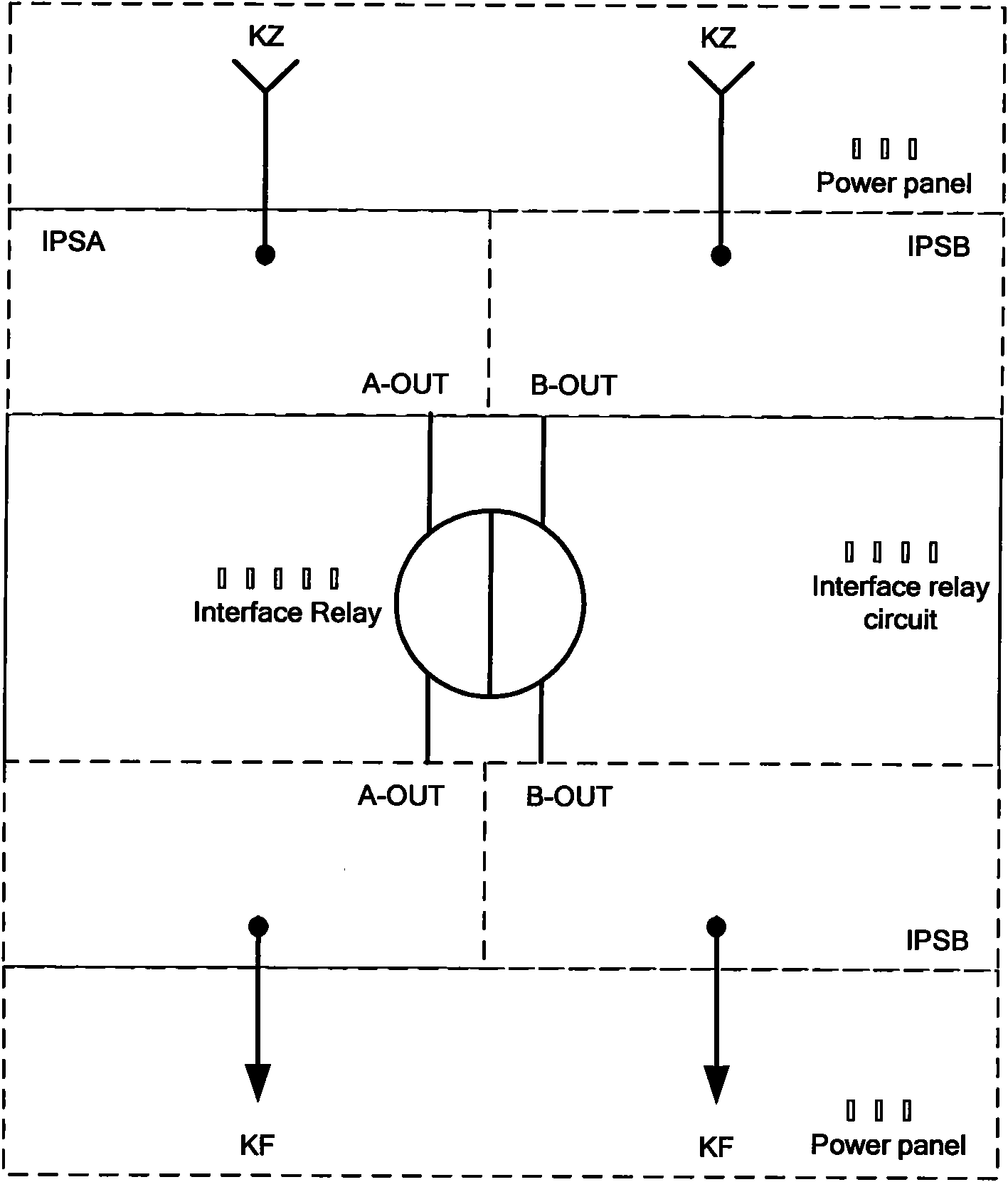

[0029] Such as figure 1 As shown, the KZ and KF power sources drawn from the power panel are respectively sent to the IPS to generate the driving power for driving the related interface relays.

[0030] Output parallel control is implemented by application software. For the same driving relay, IPSA and IPSB respectively drive a group of coils of the relay. When the A-OUT and B-OUT of a certain output port are output at the same time, the parallel control of the port is realized. Otherwise, when the application software judges that a certain port cannot be controlled in parallel, it will close the output of the backup system of the port, and only the coils of the relays of the main system have driving power to real...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More