High-speed parallel equalizer and equalizing method thereof

An equalizer and high-speed technology, which is applied in digital receivers and digital communication fields, can solve the problems of rarely seen high-speed parallel equalization algorithm implementation schemes, unfavorable hardware implementation, and discontinuous data points, etc., so as to improve hardware implementation speed and better Convergence effect, effect of saving hardware resources

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0042] The following describes the implementation of the high-speed parallel equalizer in conjunction with the accompanying drawings and specific implementation examples:

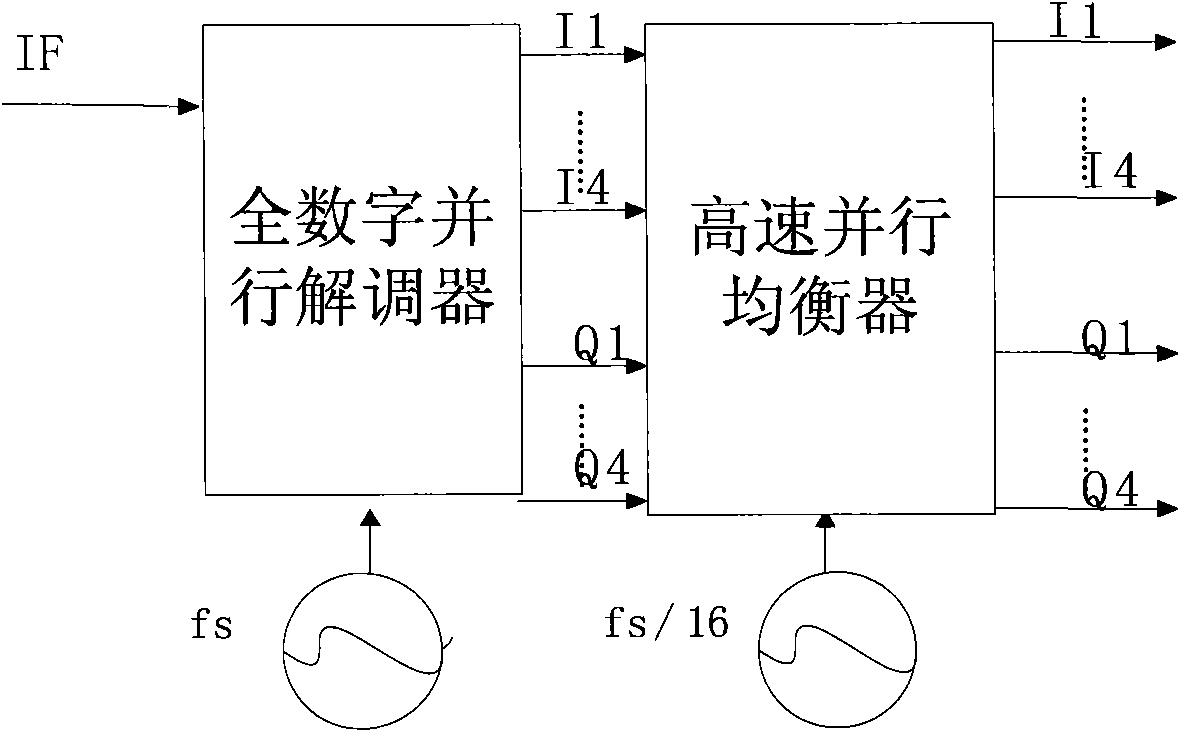

[0043] figure 1 It is the specific application mode of the equalizer. The equalizer of the present invention is generally placed after the all-digital parallel demodulator. This figure shows that the parallel 4-way data is sent from the demodulator. 1 / 16 times, the output is also parallel 4-way data. A high-speed parallel equalizer processes the demodulated complex signal at a symbol rate of 1 / n (1 / 4). The data input to the parallel equalizer is one sample point per symbol. The following takes 4 channels as an example to illustrate the specific implementation method, and other channels can be implemented in a similar manner.

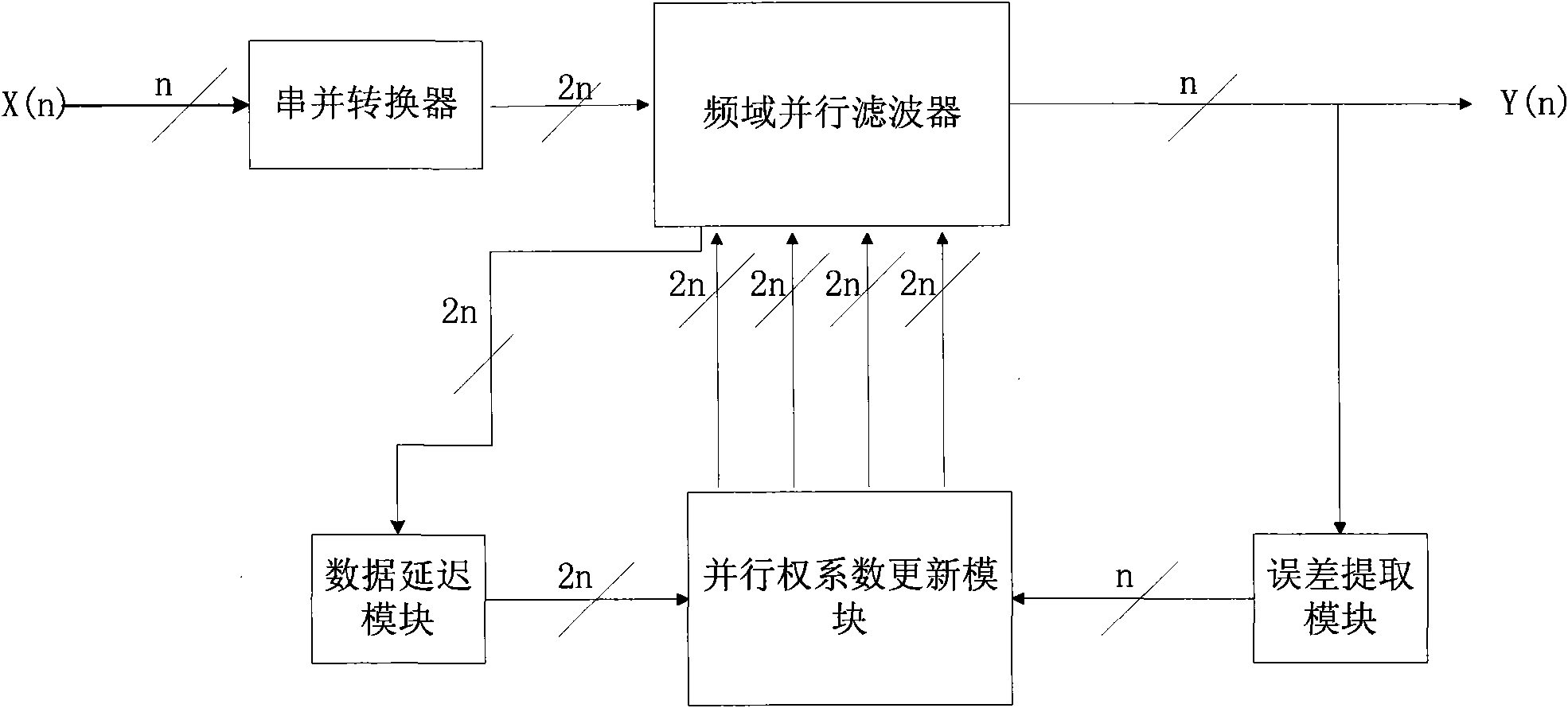

[0044] figure 2 It is a schematic diagram of the composition of the equalizer of the present invention. The high-speed parallel equalizer structure includes five main parts: a se...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More