Parallel interpolation bit synchronization system in all-digital demodulation and synchronized method thereof

An all-digital demodulation and bit synchronization technology, which is applied in the field of digital communication and all-digital demodulators, can solve the problems that cannot meet the actual needs, cannot directly apply parallel structures, etc. formula simple effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

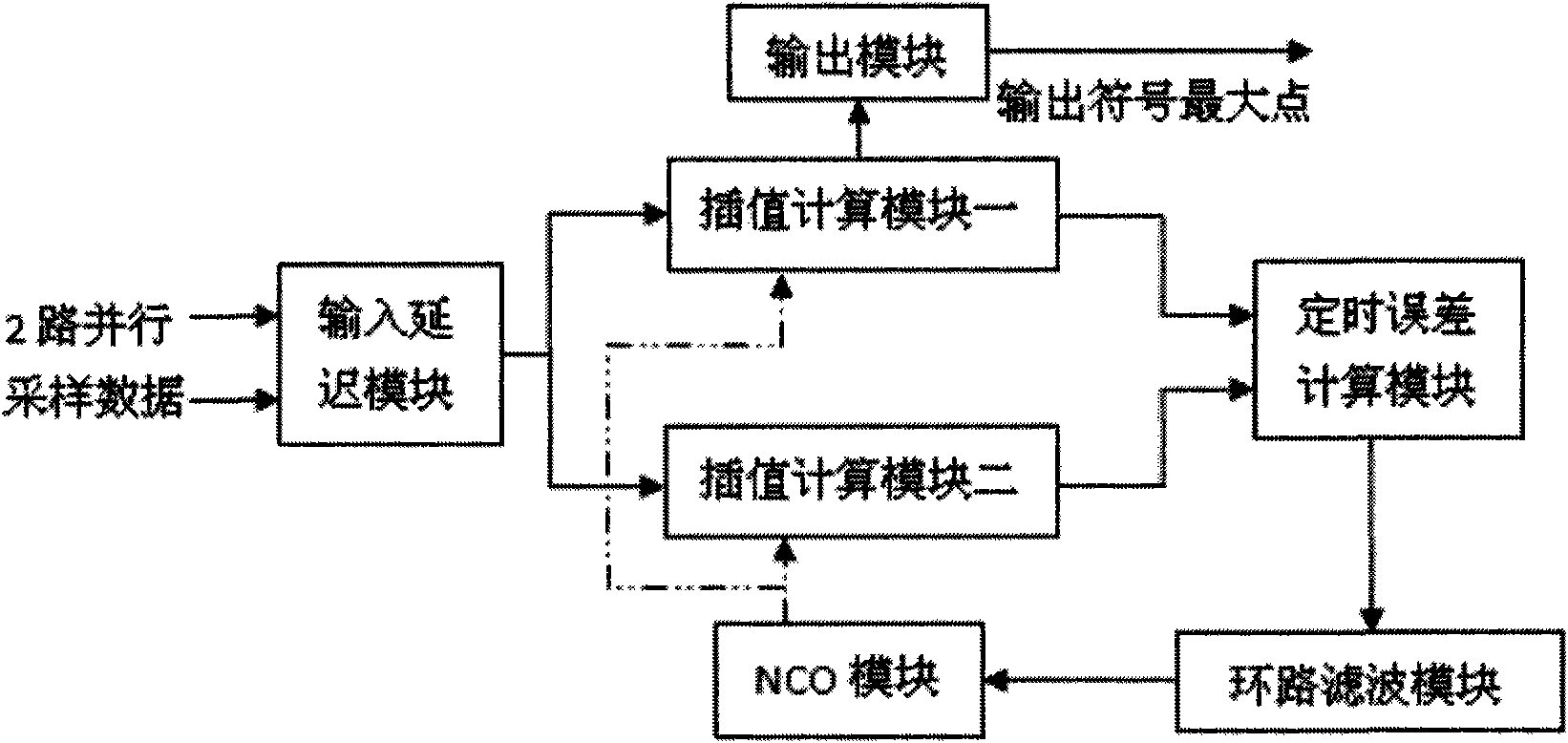

[0033] Such as figure 1 As shown, the parallel interpolation bit synchronization system in full digital demodulation includes: input delay module, interpolation calculation module 1, interpolation calculation module 2, timing error calculation module, loop filter module, NCO module and output module;

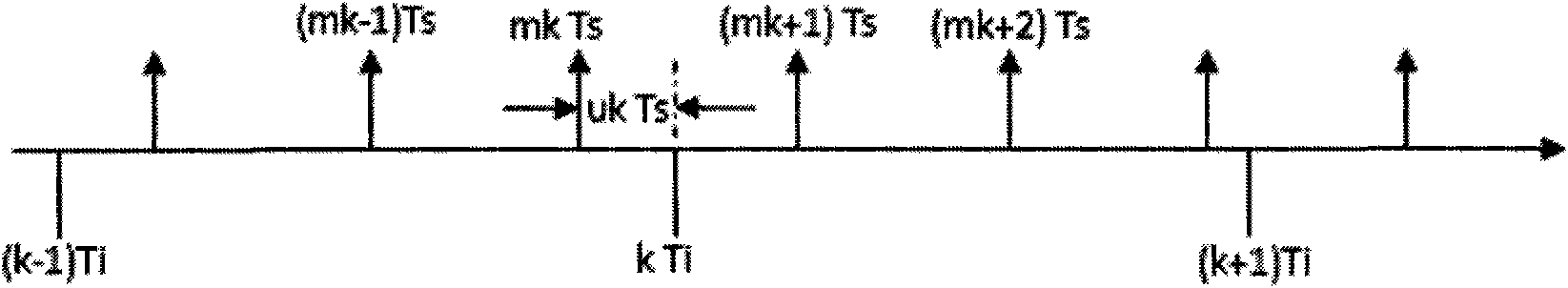

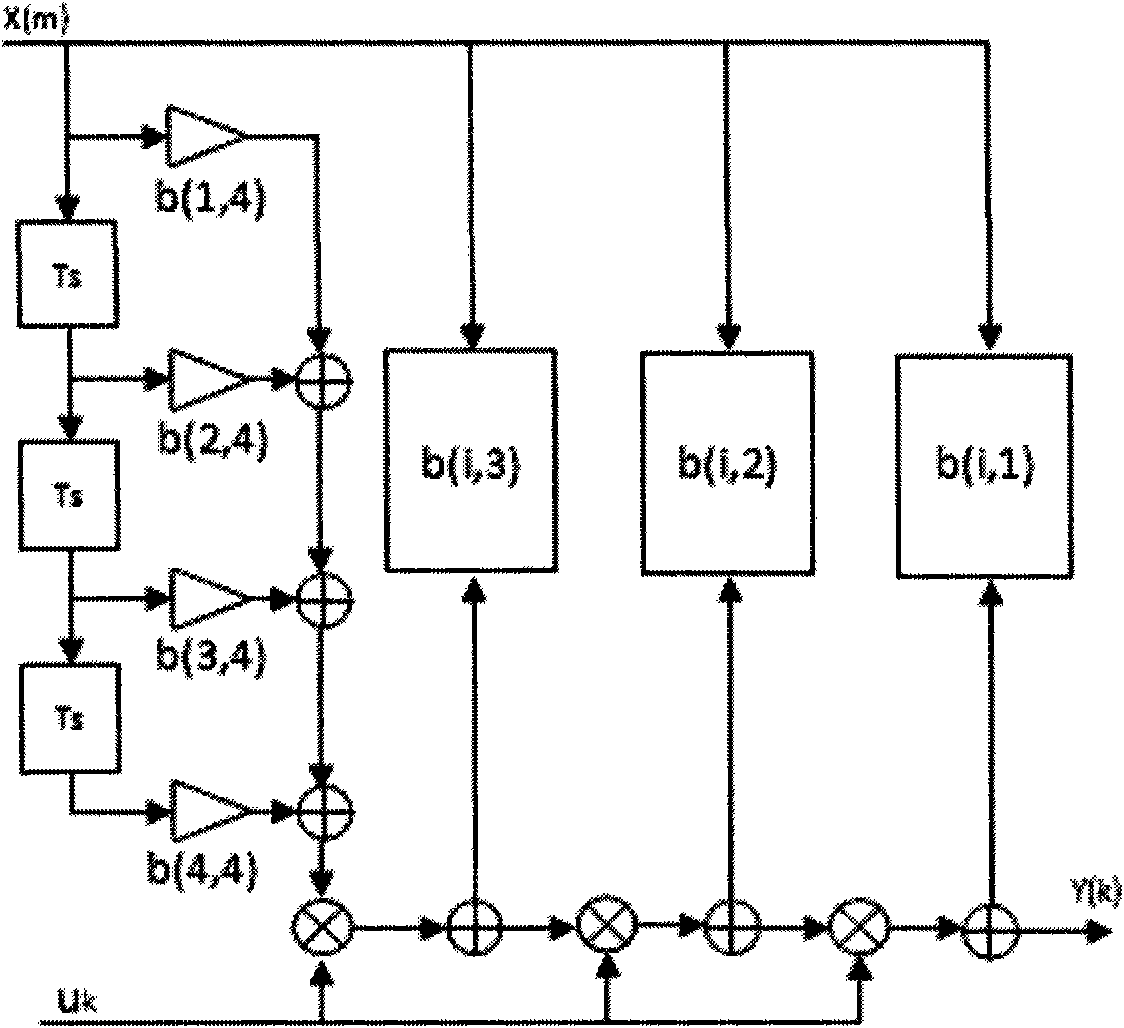

[0034] After the sampled data passes through the input delay module, it enters the interpolation calculation module (interpolation calculation module 1, interpolation calculation module 2), and the interpolation calculation module uses four points to calculate each time. The calculated points include the decision points representing the data symbols and the symbols. Crossing points, crossing points are meaningless to data judgment, but time errors need to be calculated through them, so they also need to be calculated. The data from the interpolation calculation module, on the one hand, is sent to the output module for further processing, and at the same time enters the timing er...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More