Chip lug structure and manufacturing method thereof

A manufacturing method and a technology of bumps, which are applied in semiconductor/solid-state device manufacturing, electrical components, electric solid-state devices, etc., can solve the problems affecting the reliability of packaging, difficult to control the amount of solder in solder bumps 18, and the amount of solder does not meet the requirements, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0021] The present invention will be further described below in conjunction with the accompanying drawings and embodiments.

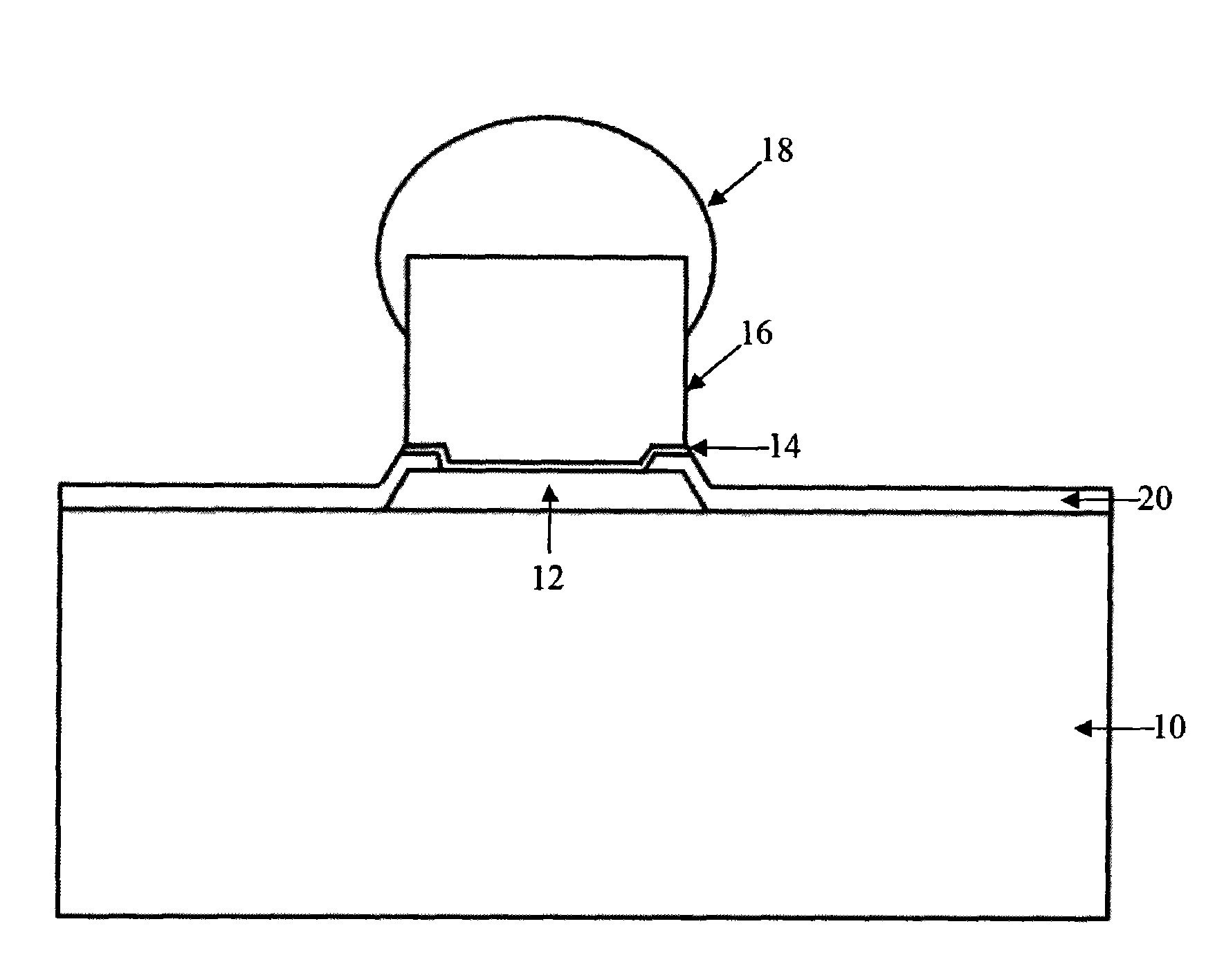

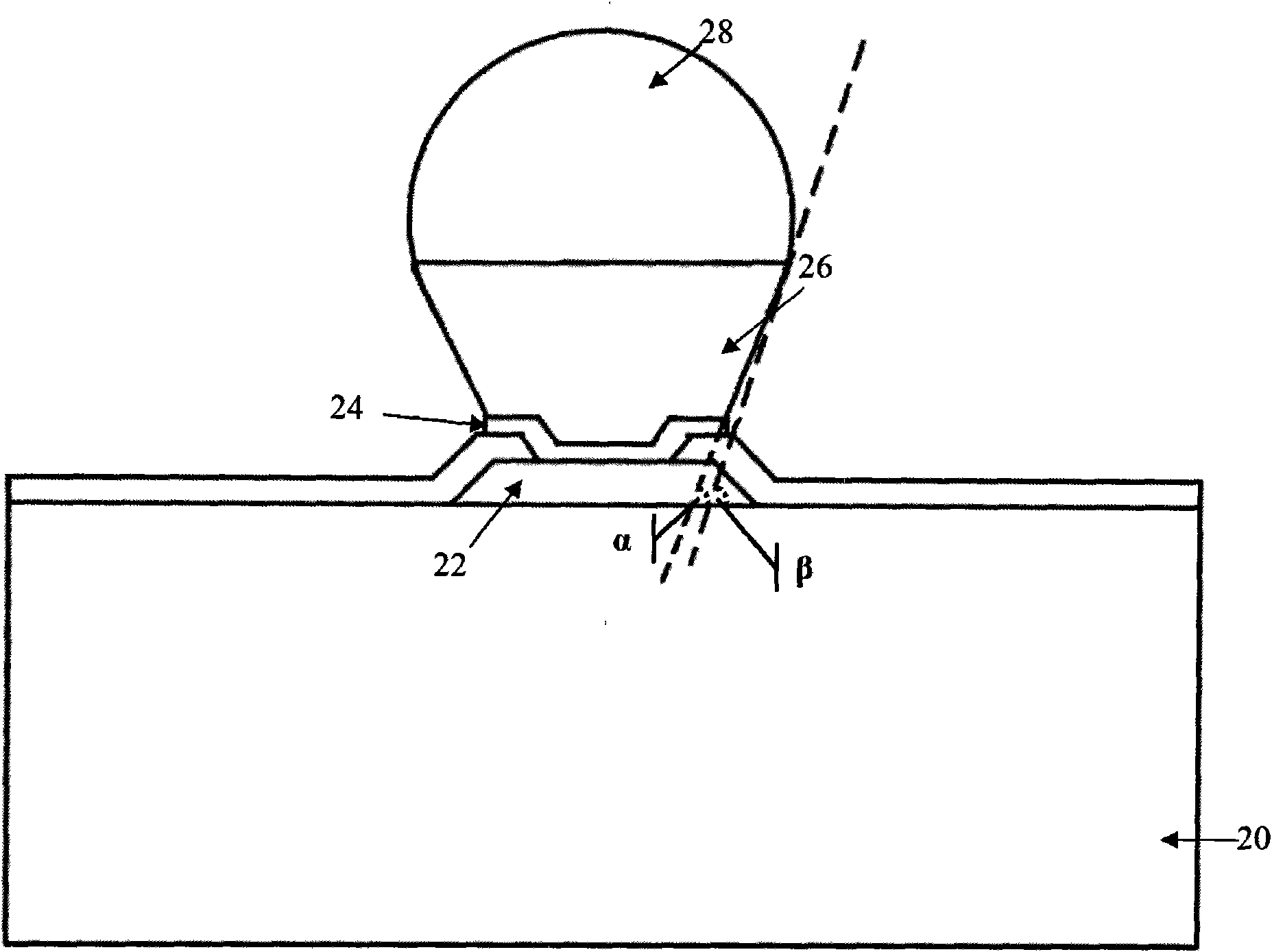

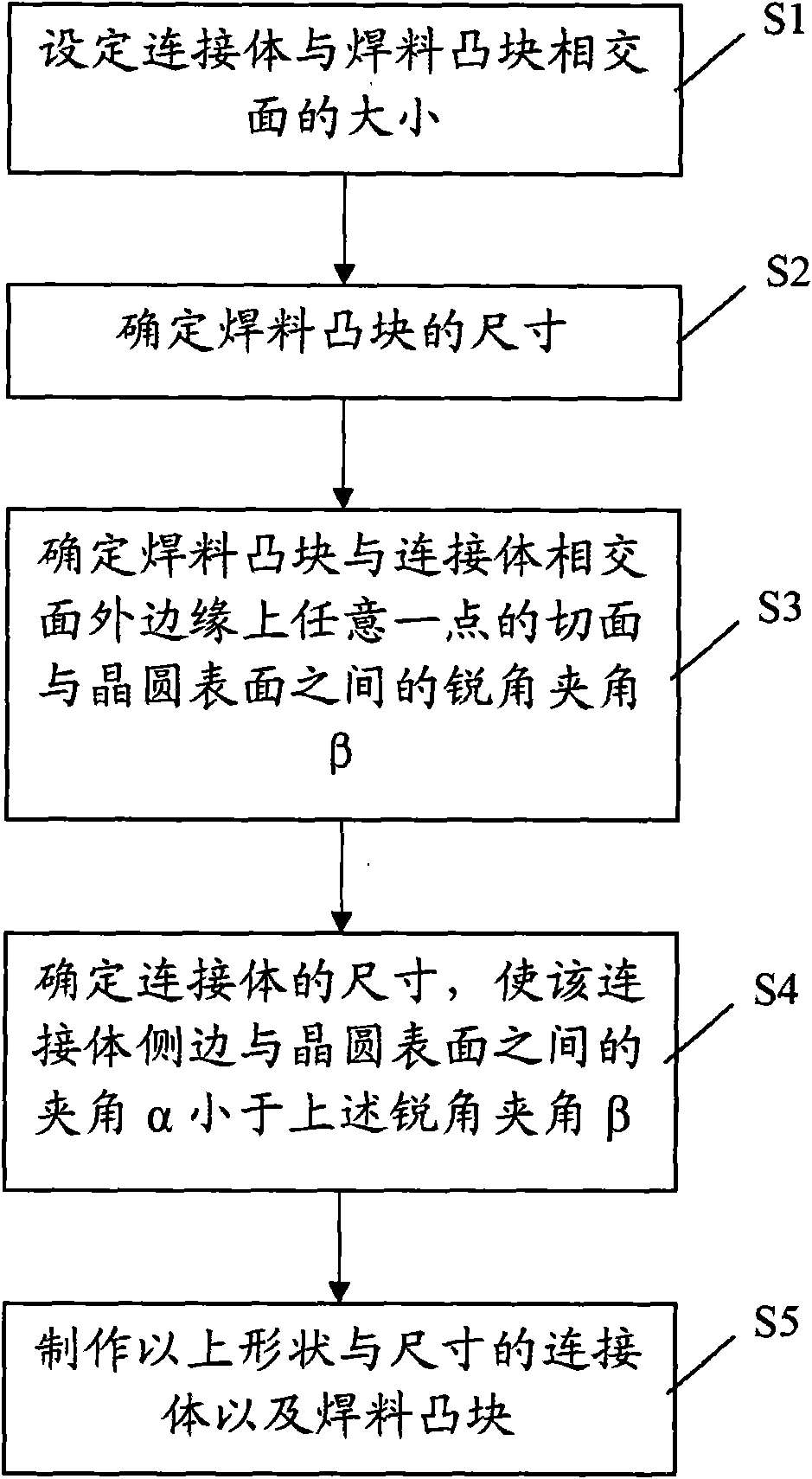

[0022] Please refer to figure 2 , which is a schematic cross-sectional view of a chip bump structure provided by an embodiment of the present invention. As shown in the figure, the chip bump structure is formed on the bonding pad 22 on the surface of the wafer 20, which includes a connecting body 26 on the bonding pad and a solder bump 28 on the connecting body 26, wherein the connecting body 26 has a shape For the Taiwan body. Usually, a first included angle α is formed between the side of the connecting body 26 and the surface of the wafer 20; A second included angle β less than 90 degrees is formed between the surfaces, wherein the first included angle α is smaller than the second included angle β.

[0023] In actual operation, the material of the connecting body 26 is often copper; and the UBM layer 24 is usually formed between it and the pad 22...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More