64-bit floating-point multiply accumulator and method for processing flowing meter of floating-point operation thereof

A floating-point multiplication and addition technology, applied in electrical digital data processing, digital data processing components, instruments, etc., can solve problems such as increased area overhead, FAR path delay bottleneck, and complexity of path division, reducing time The effect of prolonging and reducing area overhead

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

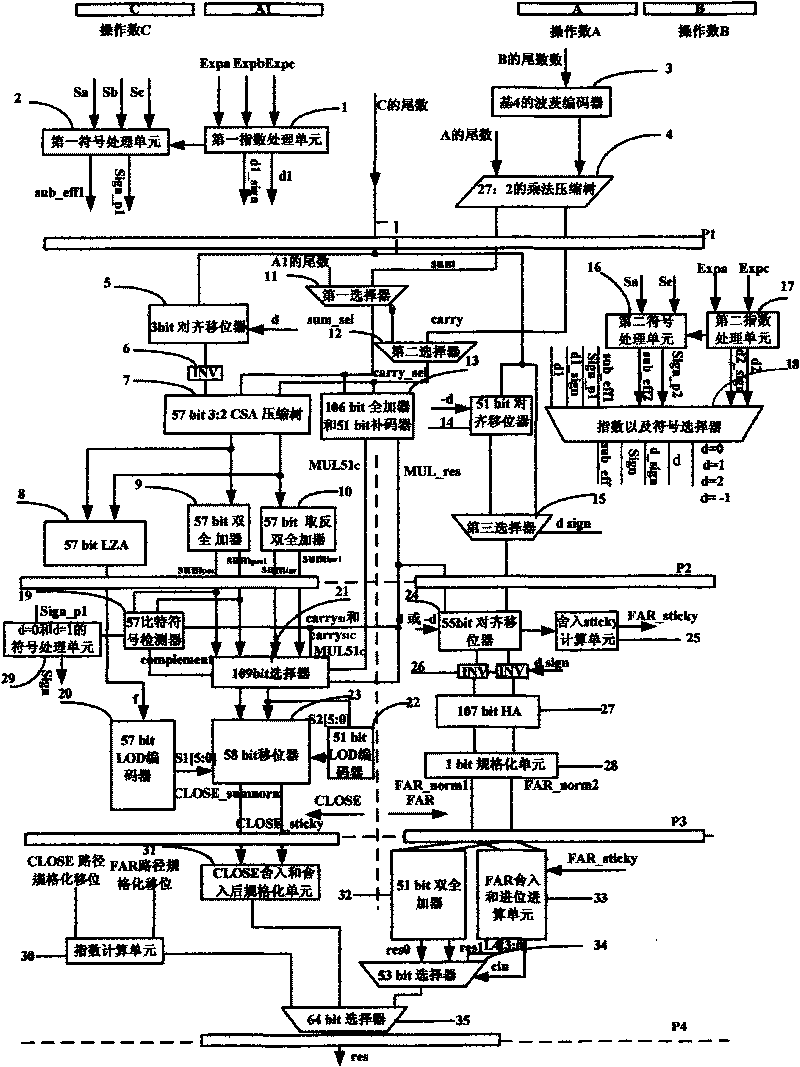

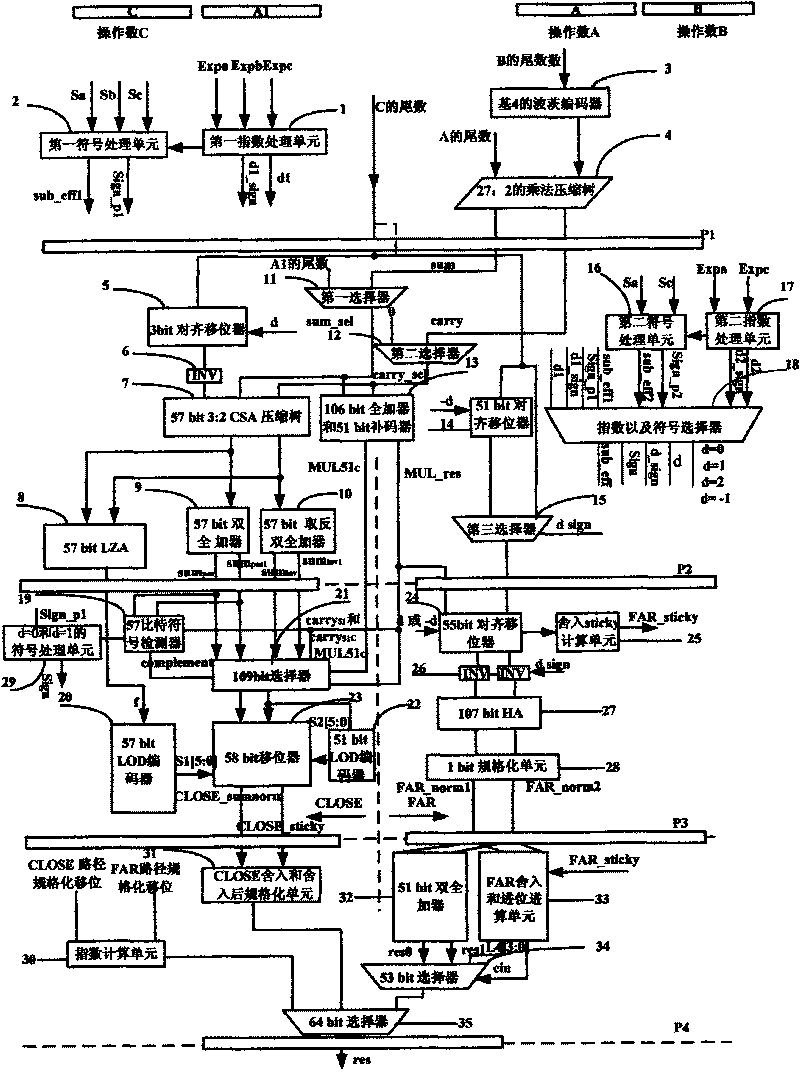

[0050] In order to make the purpose, technical solution and advantages of the present invention clearer, the 64-bit floating-point multiplier-adder and its floating-point operation pipeline beat processing method of the present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments. It should be understood that the specific embodiments described here are only used to explain the present invention rather than limit the present invention.

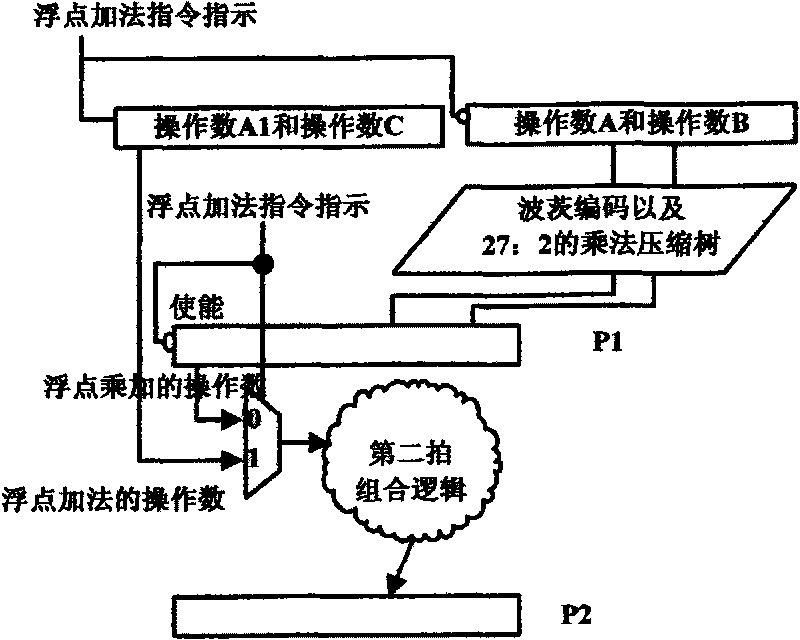

[0051] The 64-bit floating-point multiply-accumulator and its floating-point operation pipeline beat processing method in the embodiment of the present invention realize the floating-point multiply-accumulate operation in the form of (A×B)+C.

[0052] The 64-bit floating-point multiply-adder in the embodiment of the present invention is a 64-bit floating-point multiply-adder of an improved double-precision dual-path, which is divided into 2 paths according to the index difference of mu...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More