Anti-radiation field effect transistor, CMOS integrated circuit and preparation thereof

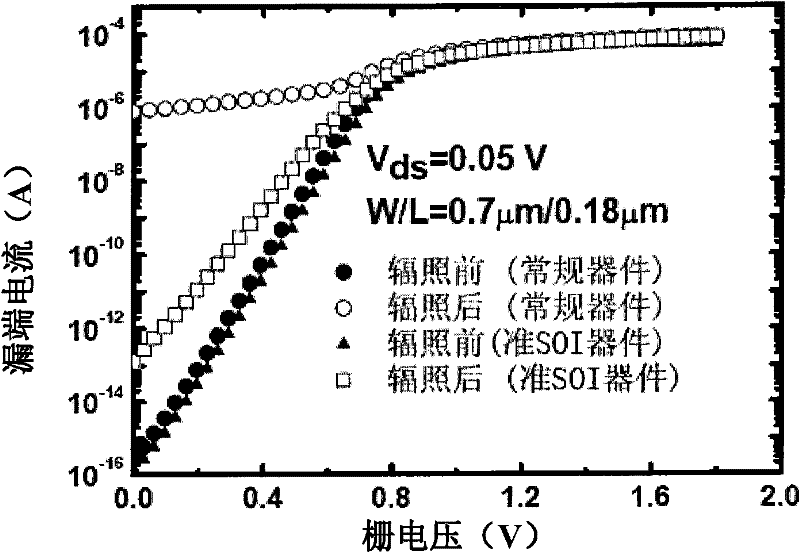

A technology of field effect transistors and body regions, which is applied in the manufacture of transistors, circuits, semiconductors/solid-state devices, etc., and can solve problems such as difficult resistance to single event effects, poor resistance to total dose effects, and increased off-state current

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

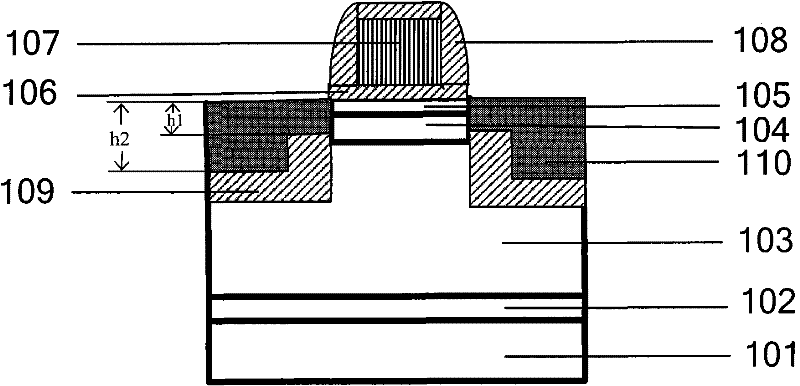

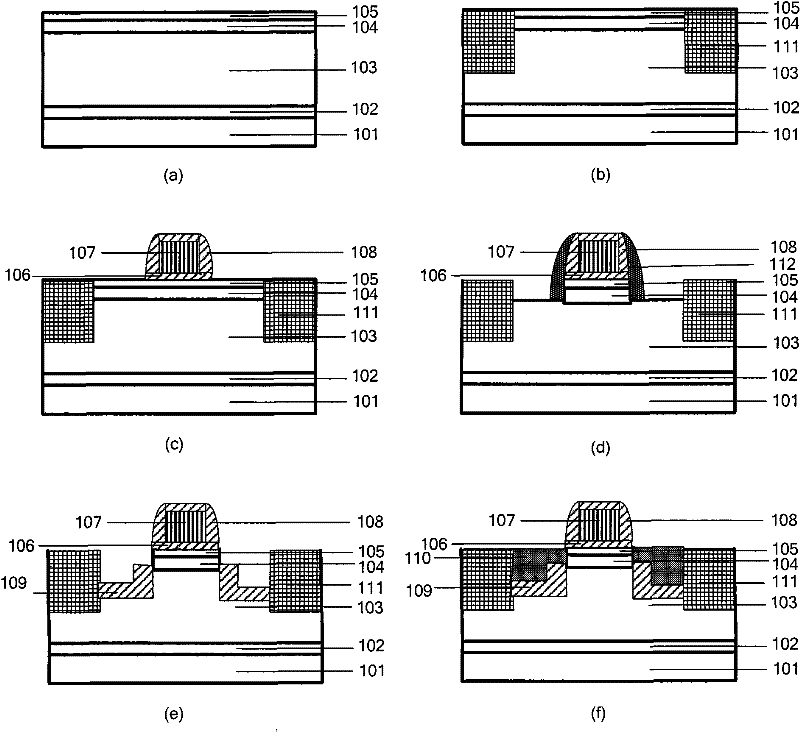

[0029] Attached below figure 2 (a)---(e) further describe in detail the preparation method and process flow of N-type field effect transistor of the present invention:

[0030] 1) On the p-type bulk silicon substrate 101, sequentially epitaxially n+ epitaxial layer 102, p well region 103, p+ epitaxial layer 104 and p epitaxial layer 105, such as figure 2 As shown in (a), wherein the thickness of the n+ epitaxial layer 102 is 50-250 nm, the thickness of the p well region 103 is 150-500 nm, the thickness of the p+ epitaxial layer 104 is 20-50 nm, and the thickness of the p epitaxial layer 105 is 10-20 nm ,like figure 2 (a) shown.

[0031] 2) Shallow trench isolation (STI) is used to define the active region, and the depth of the STI isolation region 111 is 250-350nm, preferably 300nm, such as figure 2 (b) shown.

[0032] 3) Thermally oxidize the gate oxide layer 106, deposit polysilicon gate material, perform n-type doping implantation on the polysilicon material, activa...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More