Fan-out circuit of array substrate

A technology of array substrates and fan-out circuits, applied in circuits, nonlinear optics, optics, etc., can solve problems such as disconnection of wires 130, achieve the effects of preventing disconnection, improving yield and display effect, and avoiding scratches

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

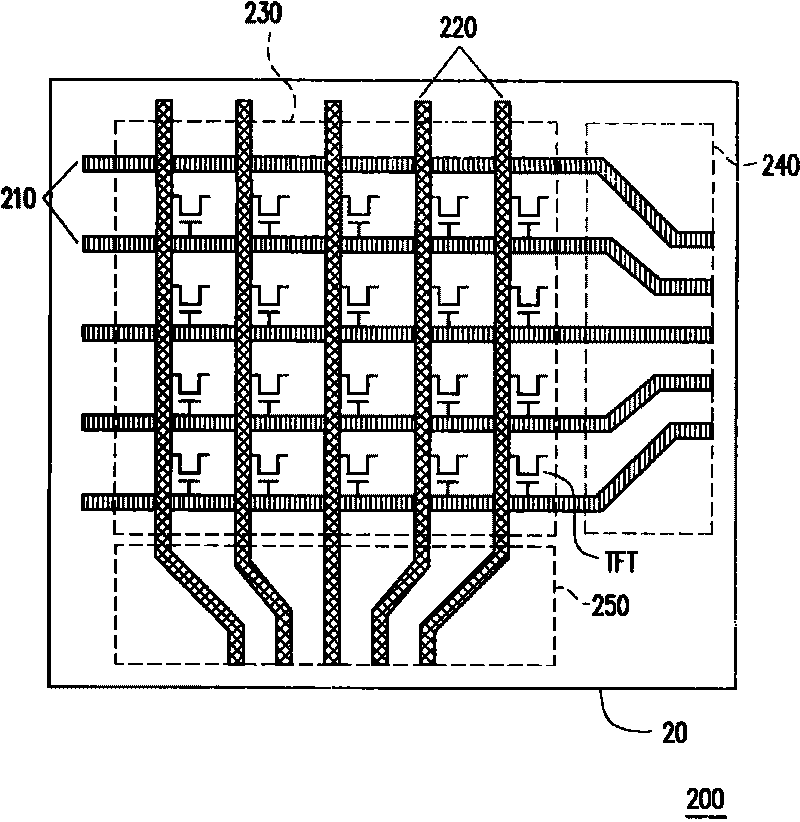

[0034] Figure 3A It is a schematic diagram of the fan-out circuit of the first embodiment of the present invention. Please refer to Figure 3A In this embodiment, the fan-out circuit 300 may be a circuit layout implementation manner provided on the aforementioned array substrate 200. The fan-out circuit 300 is composed of a main fan-out wire 320 and a pseudo-fan-out wire pattern 340 disposed on the substrate 30. And the main fan-out wire 320 and the pseudo-fan-out wire pattern 340 are arranged in a staggered manner, wherein the pseudo-fan-out wire pattern 340 includes a pseudo-fan-out wire 330 and a pad layer 310 (refer to Figure 3B ). In addition, according to the requirements of circuit layout or impedance matching, the pseudo-fan-out wire 330 may be electrically connected to the main fan-out wire 320, or may be a floating line (Floating Line).

[0035] Figure 3B for Figure 3A Section along the line B-B' in the middle. Please refer to Figure 3B As seen from the cross-sec...

no. 2 example

[0039] Figure 4A It is a schematic diagram of the fan-out circuit of the second embodiment of the present invention. Please refer to Figure 4A In this embodiment, the fan-out circuit 400 may be a circuit layout implementation manner provided on the aforementioned array substrate 200. The fan-out circuit 400 is composed of a main fan-out wire 420 and a pseudo-fan-out wire pattern 440 disposed on the substrate 40. And the main fan-out wire 420 and the pseudo-fan-out wire pattern 440 are alternately arranged, wherein the pseudo-fan-out wire pattern 440 includes the pseudo-fan-out wire 430 and the pad layer 410 (refer to Figure 4B ). In addition, according to the requirements of circuit layout or impedance matching, the pseudo-fan-out wire 430 may be electrically connected to the main fan-out wire 420, or may be a floating line (Floating Line).

[0040] Figure 4B for Figure 4A Section along the line C-C' in the middle. Please refer to Figure 4B From the cross-sectional view, ...

no. 3 example

[0043] Figure 5A It is a schematic diagram of the fan-out circuit of the third embodiment of the present invention. Please refer to Figure 5A In this embodiment, the fan-out circuit 500 may be a circuit layout implementation manner provided on the aforementioned array substrate 200. The fan-out circuit 500 is composed of a main fan-out wire 520 and a pseudo-fan-out wire pattern 540 disposed on the substrate 50. And the main fan-out wire 520 and the pseudo-fan-out wire pattern 540 are arranged in a staggered manner, wherein the pseudo-fan-out wire pattern 540 includes a pseudo-fan-out wire 530 and a pad layer 510 (refer to Figure 5B ). In addition, according to the requirements of circuit layout or impedance matching, the pseudo-fan-out wire 530 may be electrically connected to the fan-out wire 520, or may be a floating line (Floating Line).

[0044] Figure 5B for Figure 5A Section along the line D-D' in the middle. Please refer to Figure 5B From the cross-sectional view, ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More