Simulation generation method for parallel interleaver

An interleaver and row number technology, applied in the field of parallel interleaver generation, can solve problems such as memory conflicts, and achieve the effects of reducing time delay, low algorithm complexity, and improving system throughput

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

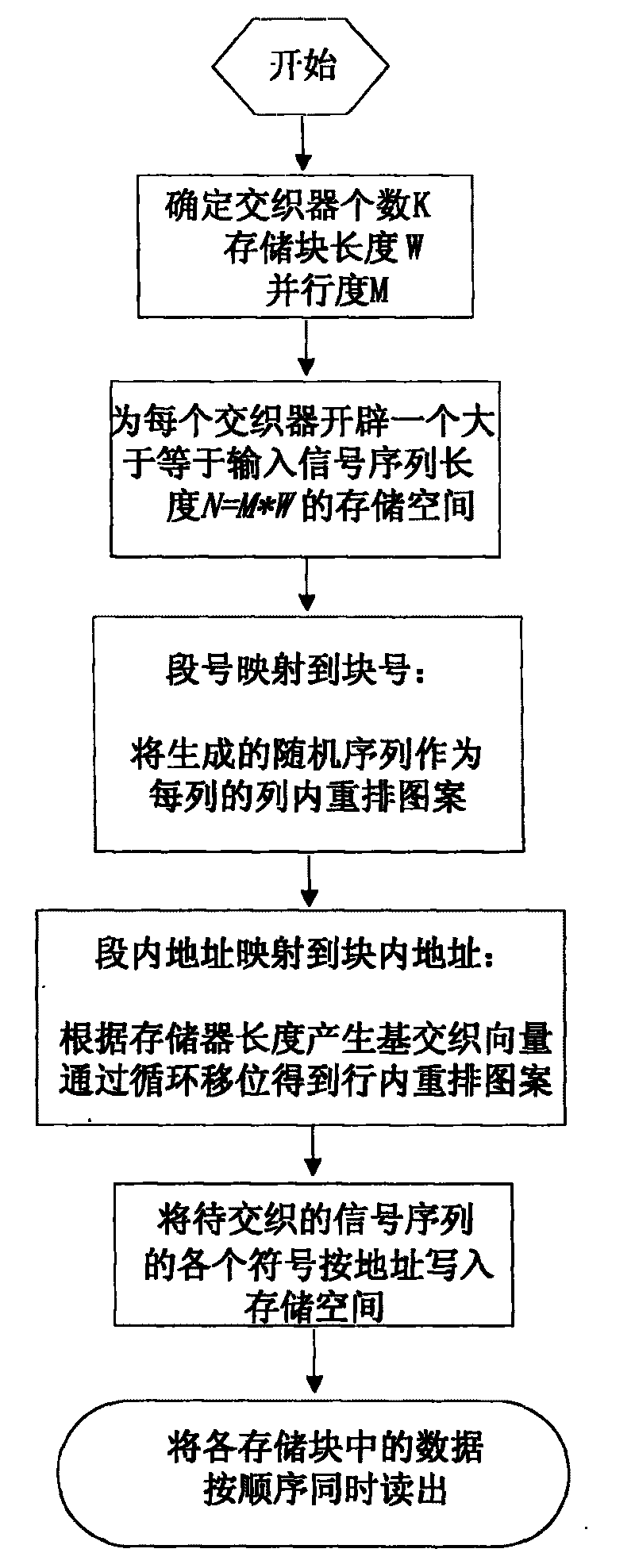

Method used

Image

Examples

Embodiment

[0065] Embodiment: In this embodiment, the number of interleavers K=2, the degree of parallelism M=4, the length of the sequence to be interleaved N=24, and thus the generation of parallel interleaving patterns when the memory length W=N / M=6 is obtained. Wherein, in the step (3), the generation of the basic interleaving vector adopts the QPP interleaver in 3GPP Realse8, and the input position index i and the output position index π(i) adopt the following relational expression:

[0066] π(i)=(f 1 i+f 2 i 2 )modW,

[0067] parameter f 1 and f 2 Depends on the block size W, which can be obtained by looking up the interleaver parameter table in the Turbo code in the 3GPP Realse8 standard (such as when W=40, f 1 = 3, f 2 =10).

[0068] The signal address sequence before interleaving is set to be arranged in the order of 1-24, and the generation of the interleaving pattern includes the following steps:

[0069] Step (1) Make a two-dimensional arrangement of 4 rows and 6 colu...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com