Method for dynamically distributing isomerism storage resources on instruction parcel based on virtual memory mechanism

A heterogeneous storage and dynamic allocation technology, applied in memory address/allocation/relocation, memory systems, instruments, etc., to improve system performance and reduce energy consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0032] The present invention will be further described in detail below in conjunction with the accompanying drawings and specific embodiments.

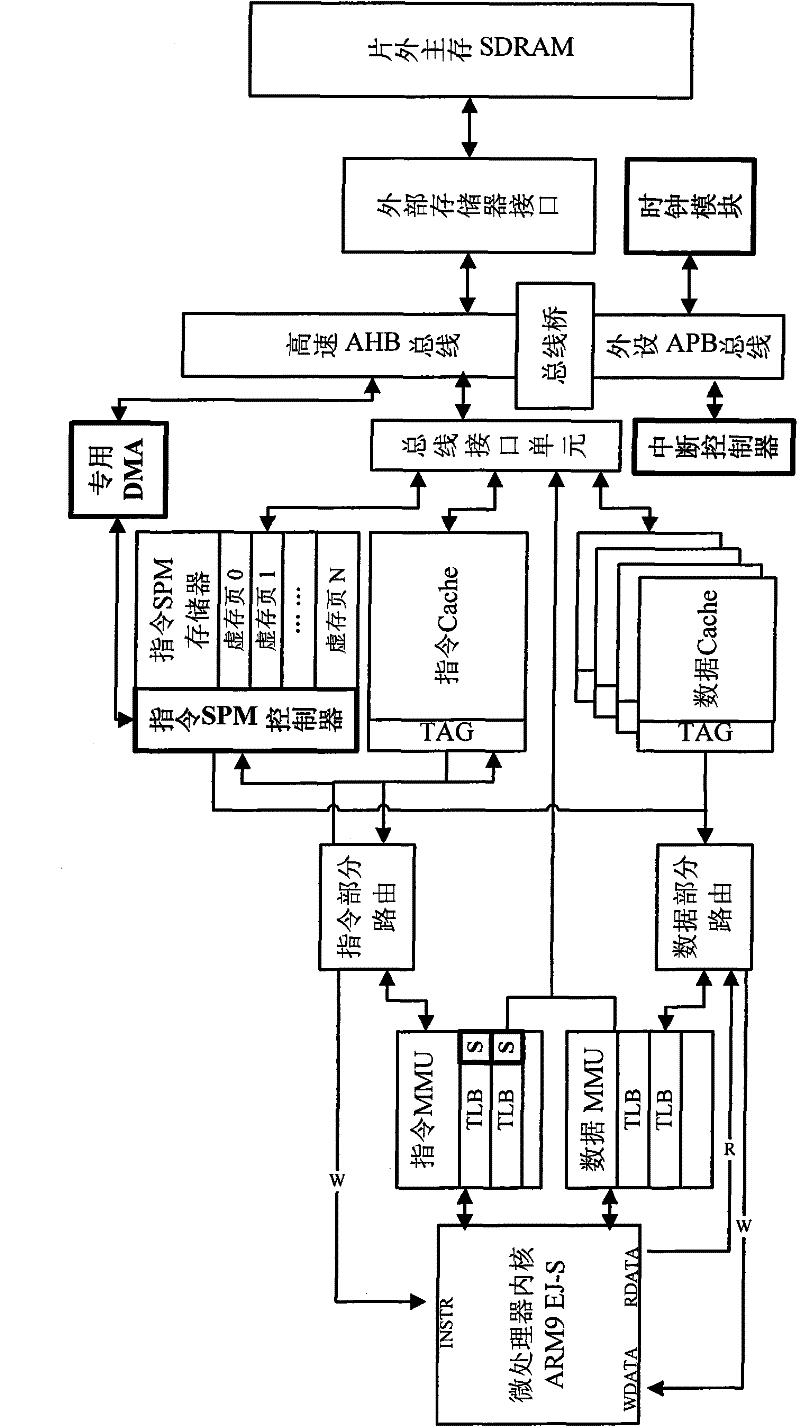

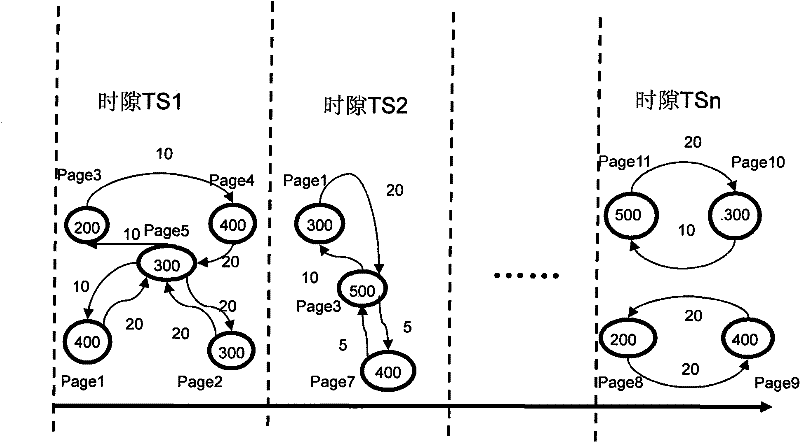

[0033] The present invention obtains the time and space distribution of instruction Cache hits and misses by tracking the instruction Cache access in the application program execution process, and then obtains the time slot access graph of instruction Cache by the distribution, including the weight of the instruction page itself (i.e. the number of Cache hits) ) and conflict graphs between instruction pages. The conflict graph is a vector diagram that quantitatively describes the replacement relationship between different program contents mapped to the same Cache line. Through the mathematical abstraction of Cache time slot access, the method of integer nonlinear programming can determine the state of each instruction page when the total energy consumption of the system is optimal, so as to obtain the page number of the most optimized...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More