Method and microprocessor for supporting single instruction stream and multi-instruction stream dynamic switching execution

A technology of single instruction stream and multiple instruction streams, which is applied in the direction of concurrent instruction execution and machine execution devices, can solve the problems of affecting processor performance, waste of processor resources, and insufficient utilization of scalar unit computing resources, etc., to achieve improved The effect of resource utilization, improving utilization, and reducing instruction bandwidth requirements

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

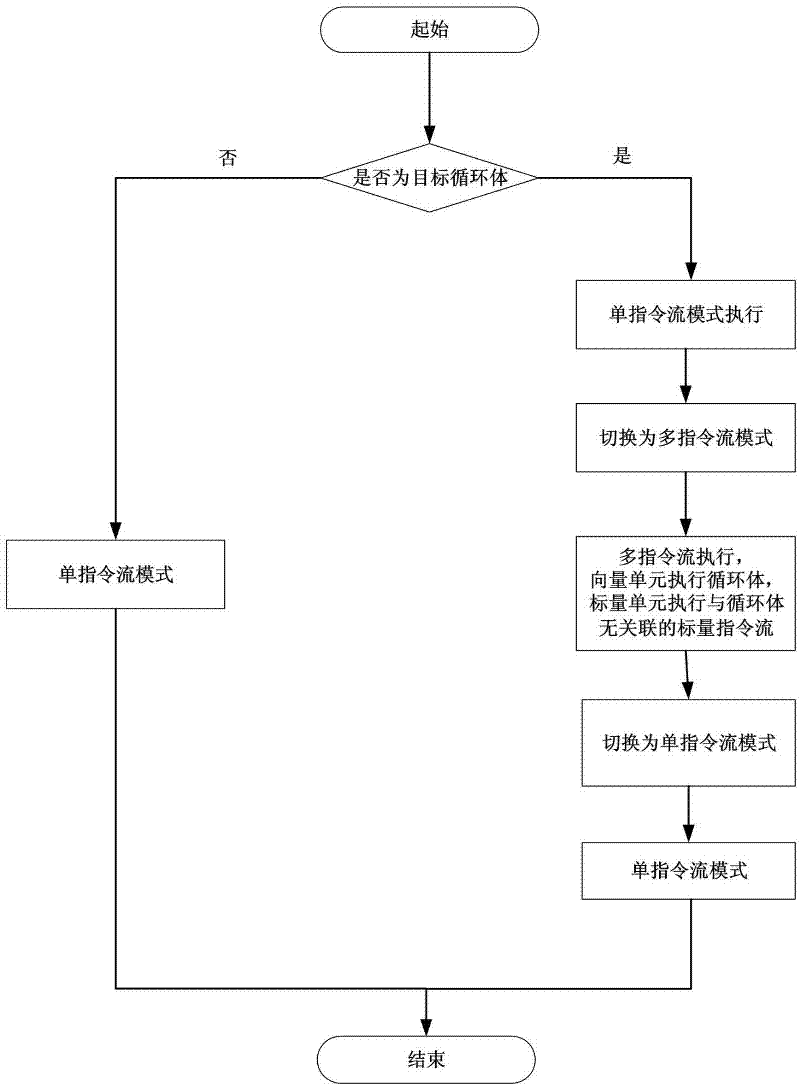

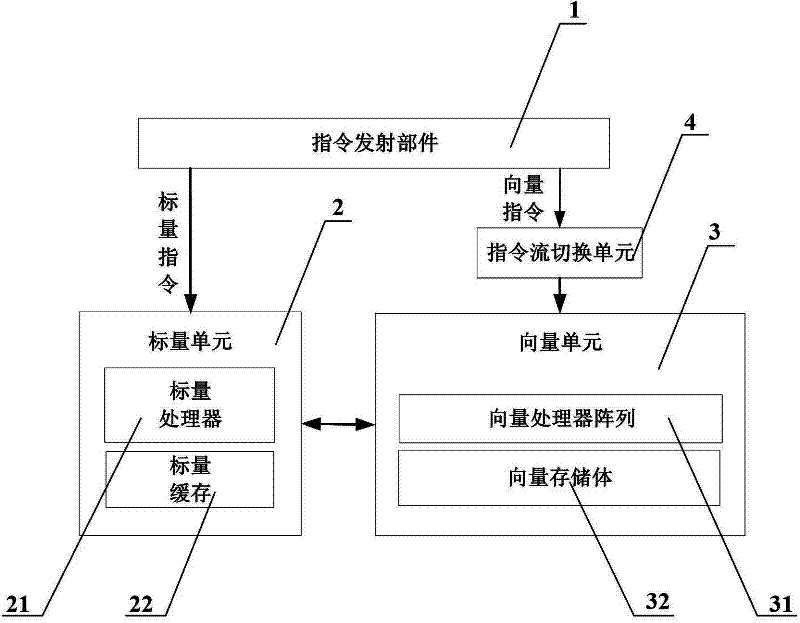

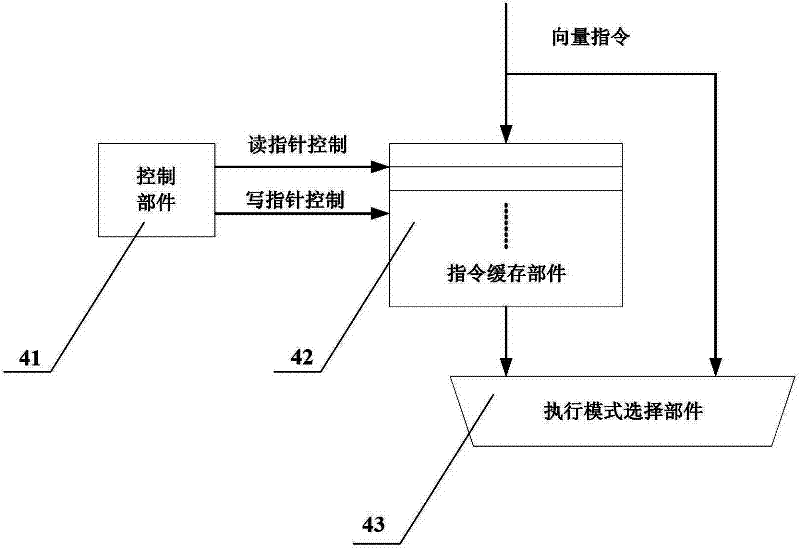

[0026] Such as figure 1 As shown, the method for supporting dynamic switching between single instruction streams and multiple instruction streams in the embodiment of the present invention uses scalar unit 2 and vector unit 3 to execute instructions from instruction issuing unit 1. The implementation steps are as follows: first, scalar unit 2 and vector unit 3 In the default single instruction flow mode, execute the same instruction stream from the instruction issuing unit 1. When the vector unit 3 executes the target loop body, the scalar unit 2 completes the initialization of the target loop body, and controls the target loop body instructions to cache and switch In the multi-instruction flow mode, then the vector unit 3 executes the cached target loop body instructions, while the scalar unit 2 executes the scalar instruction flow that is not associated with the target loop body, and finally switches to a single instruction when the vector unit 3 finishes executing the target ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com