Field programmable gate array (FPGA)-based final test (FT) method of liquid crystal display controller (LCDC) module

A testing method and a technology of collecting modules, which are applied in the fields of electronic circuit testing, optics, instruments, etc., can solve problems such as the influence of the yield rate of chip testing, the inability to test the function of the LCDC module, and the inability to test whether the function of another module is correct, etc., to achieve Auxiliary FT test, get rid of interference, reduce the effect of restraint

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

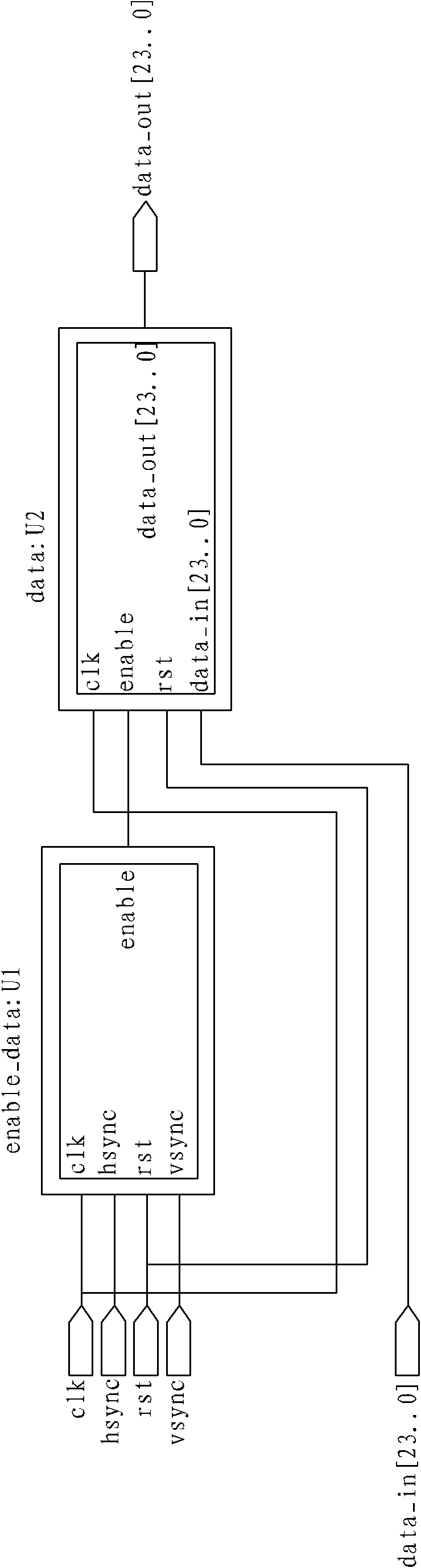

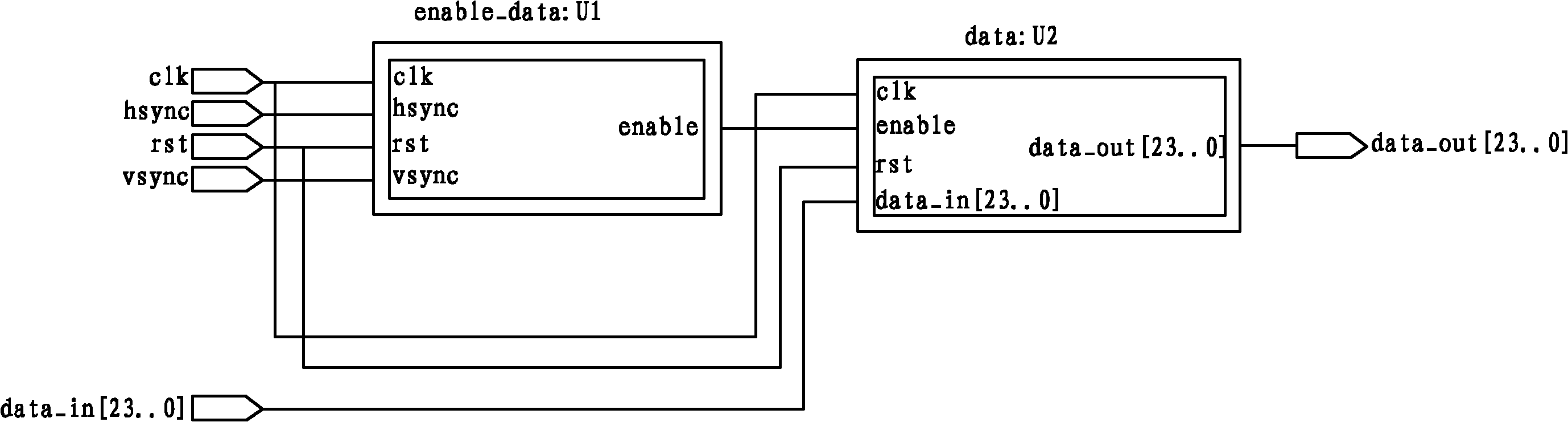

[0021] see figure 1 , is a schematic diagram of the LCDC module test. figure 1 Among them, clk, hsync, rst, and vsync are input control signals provided by the chip under test. As long as the timing of these four signals is correct, the correct enable control signal can be generated. The enable signal is used to control when to start collecting data , when to end the collection, so that the required data can be collected correctly. data_in[23..0] is the input data signal provided by the chip to be tested. The data bits are 24 bits in total. The collected data data_out[23..0] is stored in the specified memory address. Specifically include the following steps:

[0022] Step 10: Design a VIP acquisition module in FPGA;

[0023] Step 20: According to the timing of the LCDC and the V_BP (behind the field blanking), V_FP (before the field blanking), V_VD (vertical effective resolution), V_PW (field pulse width), H_BP (behind the line blanking), H_FP of the screen (line blanking)...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com