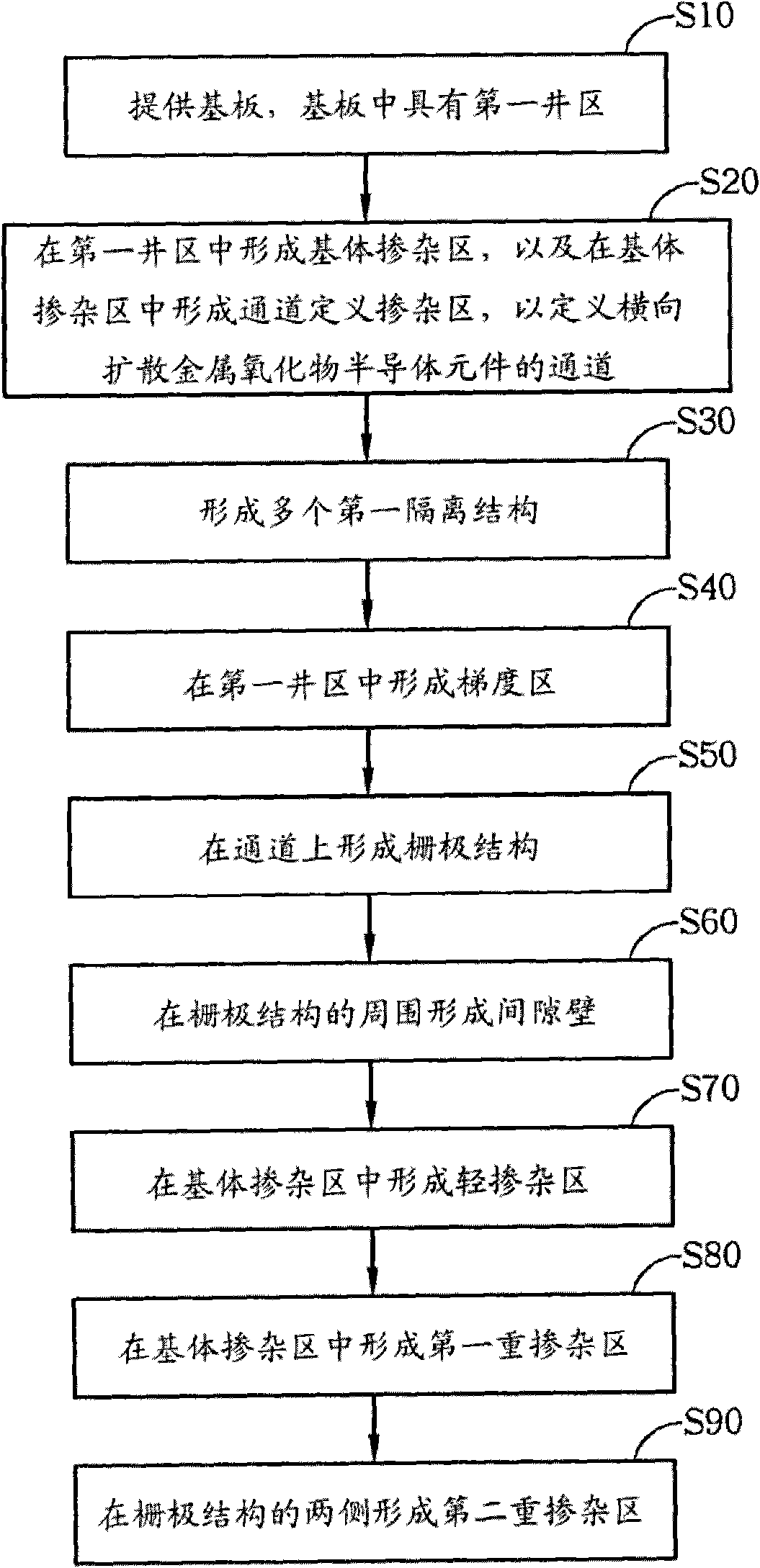

Manufacturing method of laterally diffused metal oxide semiconductor element

A technology of oxide semiconductor and manufacturing method, which is applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., and can solve problems such as misalignment, relative position error, affecting channel length

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

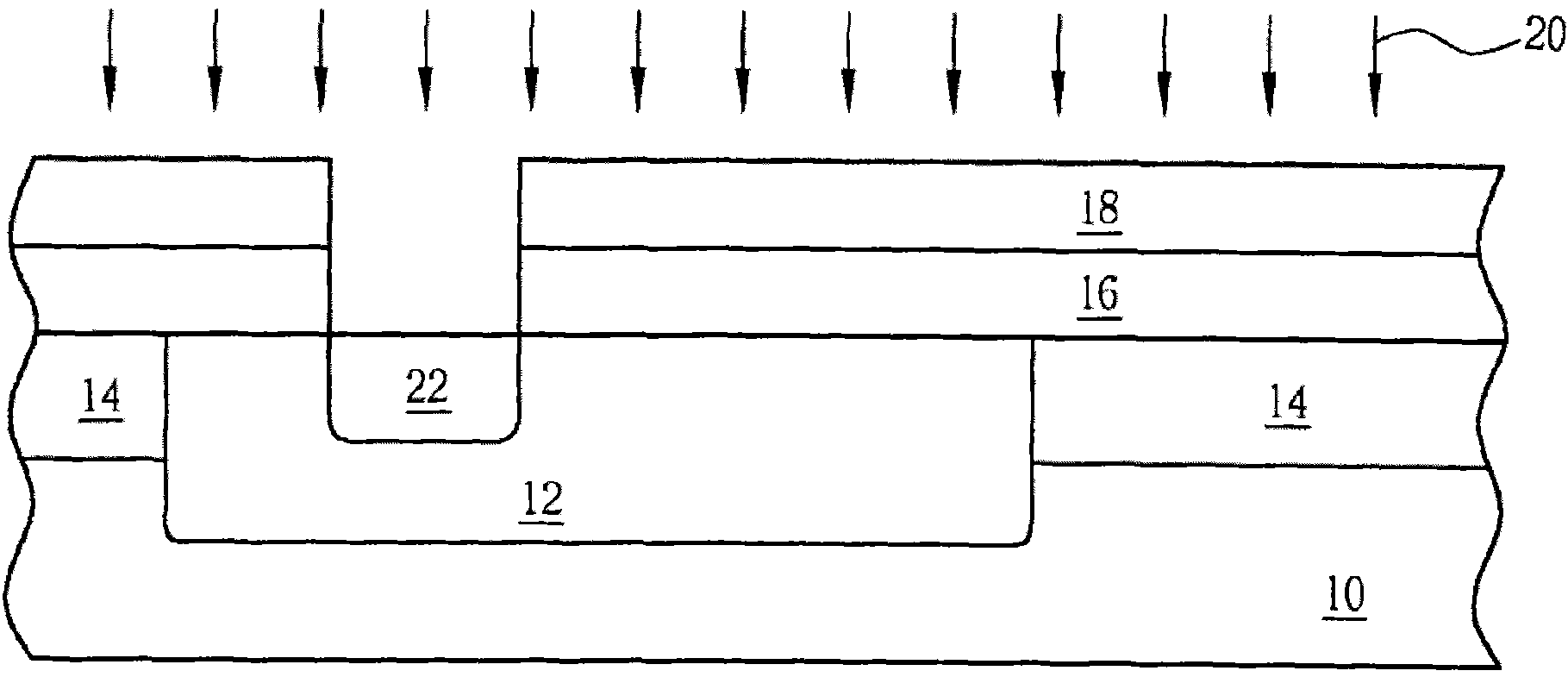

[0053] Additionally, please refer to Figure 12 and Figure 13 , Figure 12 It is a schematic flow chart of the manufacturing method of the laterally diffused semiconductor element according to the second embodiment of the present invention, Figure 13 It is a schematic diagram of the manufacturing method of the laterally diffused semiconductor device according to the second embodiment of the present invention. Compared with the first embodiment, the manufacturing method of the second embodiment is used for manufacturing a laterally diffused semiconductor device whose gate structure and drain end can withstand high breakdown voltage. The method of this embodiment before step S20 and after step S50 is the same as that of the first embodiment. In order to facilitate the comparison of the differences between the embodiments, the same steps of this embodiment and the first embodiment will not be repeated, and the same components Symbols are marked with the same symbols. Such a...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More