Lower hardware mapping method of integrated circuit, and time-space diagram compression method and device

A technology of integrated circuits and space-time maps, which is applied in the fields of electrical digital data processing, special data processing applications, instruments, etc., can solve the problems of time difference of realization, and achieve the effect of convenient and fast realization.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

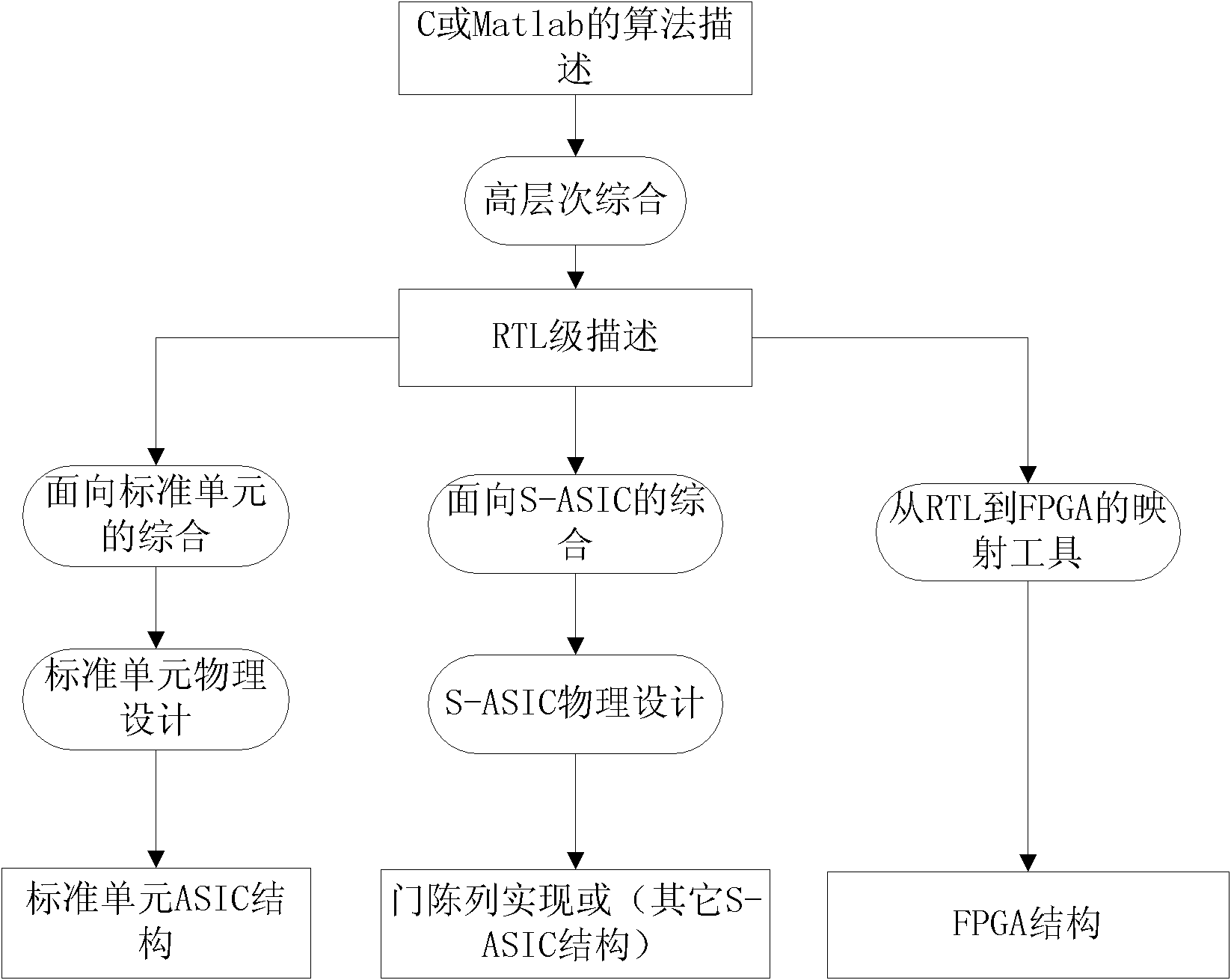

[0071] In one embodiment of the present invention, a mapping system from computer language to integrated circuit underlying hardware circuits is provided, such as Figure 7 Shown is the integrated circuit lower layer hardware mapping method of the system, including the following steps:

[0072] Step S1, analyze the high-level language program, that is, read the computer language program used to describe the target algorithm of the integrated circuit, and match the mapped execution object and parameter object from the computer language program according to the rules of the computer language. For an ASIC, first design the target algorithm of the integrated circuit according to the function of the integrated circuit, and then write a computer language program describing the algorithm of the integrated circuit. The computer language usually uses C language or MATLAB language. The written computer language program is input into the mapping system of the present invention, and the s...

Embodiment 2

[0098] H.264 is a digital video coding standard jointly formulated by the Joint Video Team (JVT) jointly established by the International Telecommunications Union (ITU-T) and the International Organization for Standardization (ISO). In this embodiment, the X264_me_search function described in the C language of the H.264 standard is taken as an example to describe the step of compressing the space-time graph in Embodiment 1 in more detail.

[0099] Such as Figure 8 The original function of X264_me_search in C language is shown as the operator space-time diagram regenerated by the procedure of program analysis step and data control flow graph generation step mentioned in Embodiment 1, and then through the step of operator structure graph generation step. Since the original program of the X264_me_search function calls the pixel_sad_16×16 function, so in Figure 8 , does not clearly show the specific operator space-time diagram of the called function such as the pixel_sad_16×16 ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More