Hierarchical heat driving floor planning and layout method

A layout planning and layout method technology, which is applied in special data processing applications, instruments, electrical digital data processing, etc., can solve the problem of not considering the influence of heat source on the device layer, so as to avoid repeated thermal calculation process, optimize area and interconnection Line length, the effect of eliminating hot spots

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0028] Embodiments of the present invention will now be described with reference to the drawings, in which like reference numerals represent like elements.

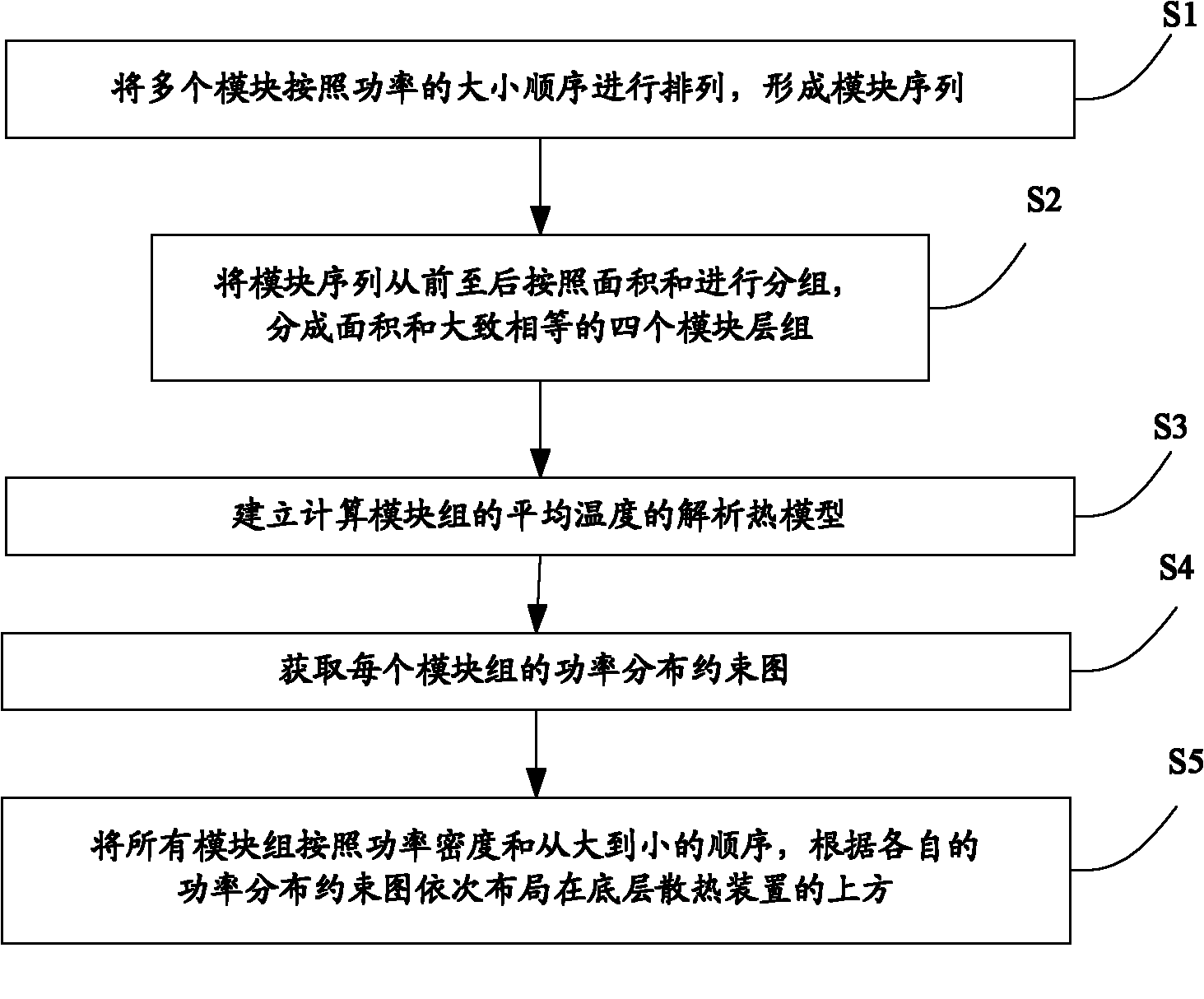

[0029] refer to figure 1 , the layered heat-driven layout planning and layout method of the present invention includes the following steps:

[0030] Step S1, arranging multiple modules according to the order of power to form a module sequence;

[0031] Step S2, group the module sequence from front to back according to the area sum, and divide it into four module layer groups whose area sum is approximately equal, so that the modules with the largest power density and the largest power density will be gathered in the same group;

[0032] Step S3, establishing an analytical thermal model for calculating the average temperature of the module group;

[0033] Step S4, obtaining the power distribution constraint graph of each module group;

[0034] Step S5, according to the power density and order from large to small, all th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More