Metal oxide semiconductor (MOS) bootstrap switch circuit for calibrating sampling clock offset

A sampling clock and switching circuit technology, applied in the field of MOS bootstrap switching circuits, can solve the problems of increasing design complexity and chip area and power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

specific Embodiment approach

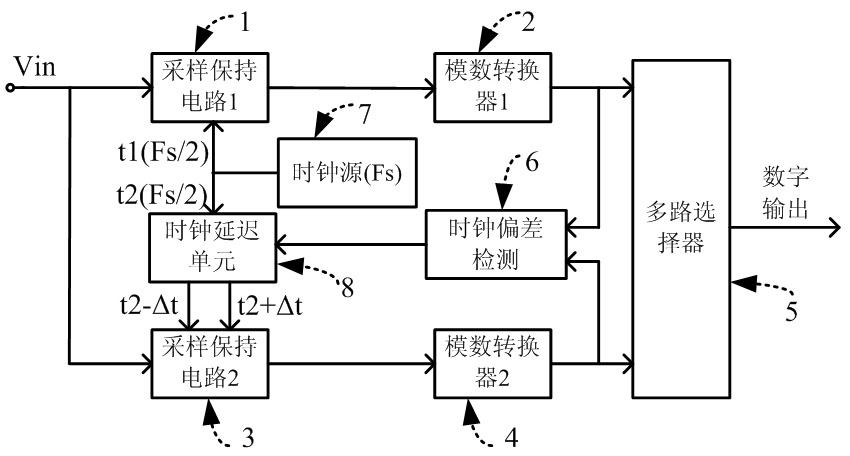

[0036] figure 2 Represents an implementation structure that can eliminate channel-to-channel sampling clock skew in a time-interleaved analog-to-digital converter. By detecting the clock deviation between channels, and then feeding it back to the clock delay circuit, the size and direction of the clock delay are adjusted until the deviation is finally eliminated. The invention saves the clock delay circuit unit and realizes the same function. The specific implementation is as follows:

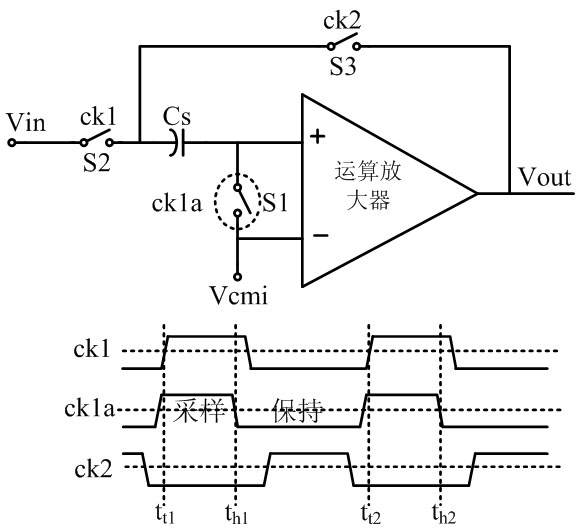

[0037] image 3 A schematic diagram of a single-ended sample-and-hold circuit. The timing diagrams of three clocks ck1, ck2 and ck1a are shown in the figure. at t t1 After time, the switches S1 and S2 are closed, S3 is opened, the circuit enters the sampling stage, and the capacitor Cs follows the input signal Vin. when the arrival time t h1 , the clock ck1a is turned off in advance, and this moment determines the actual sampling point of the sample-and-hold circuit. because t h1 In the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More