Patents

Literature

46 results about "Sampling clock offset" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

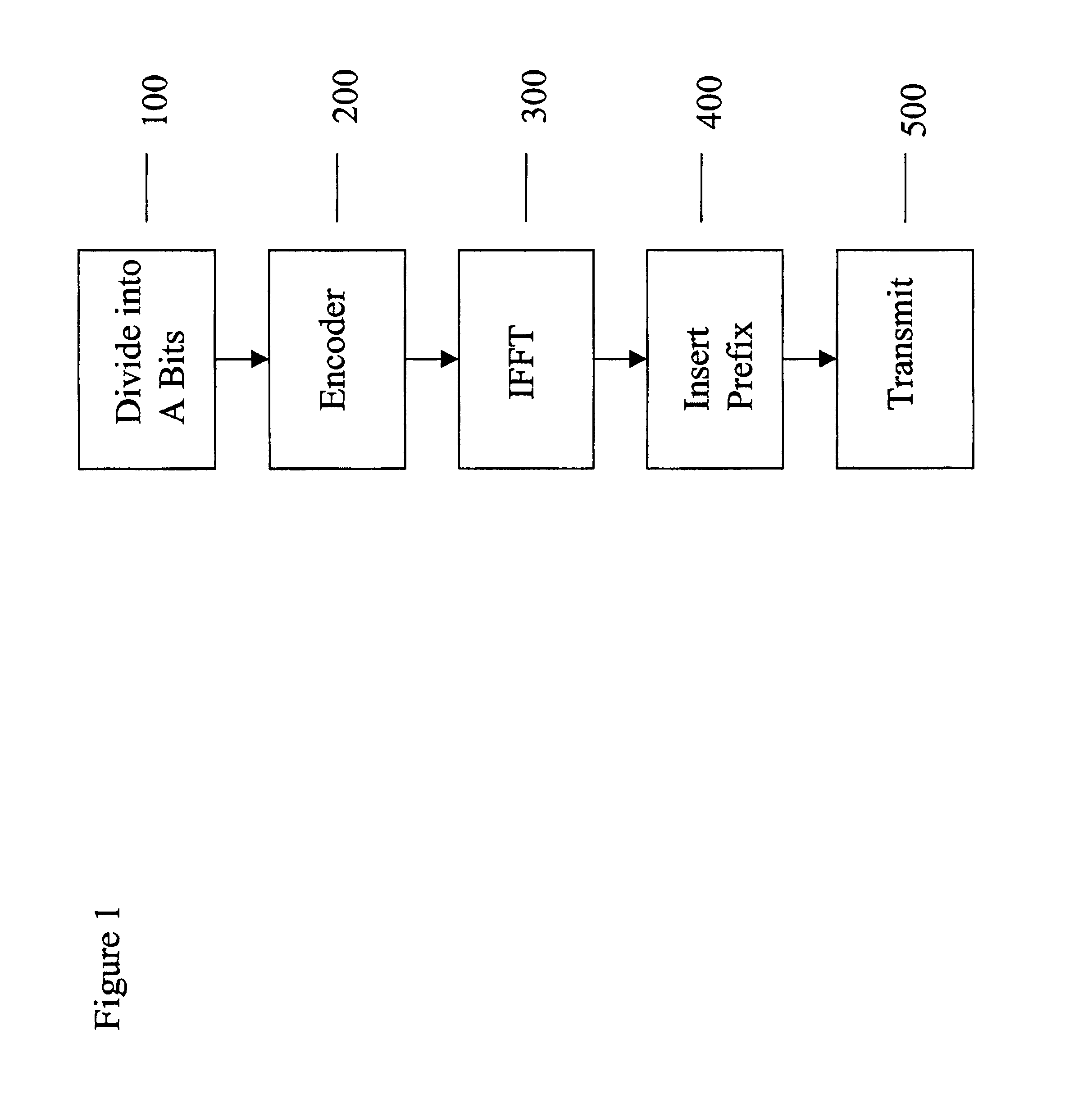

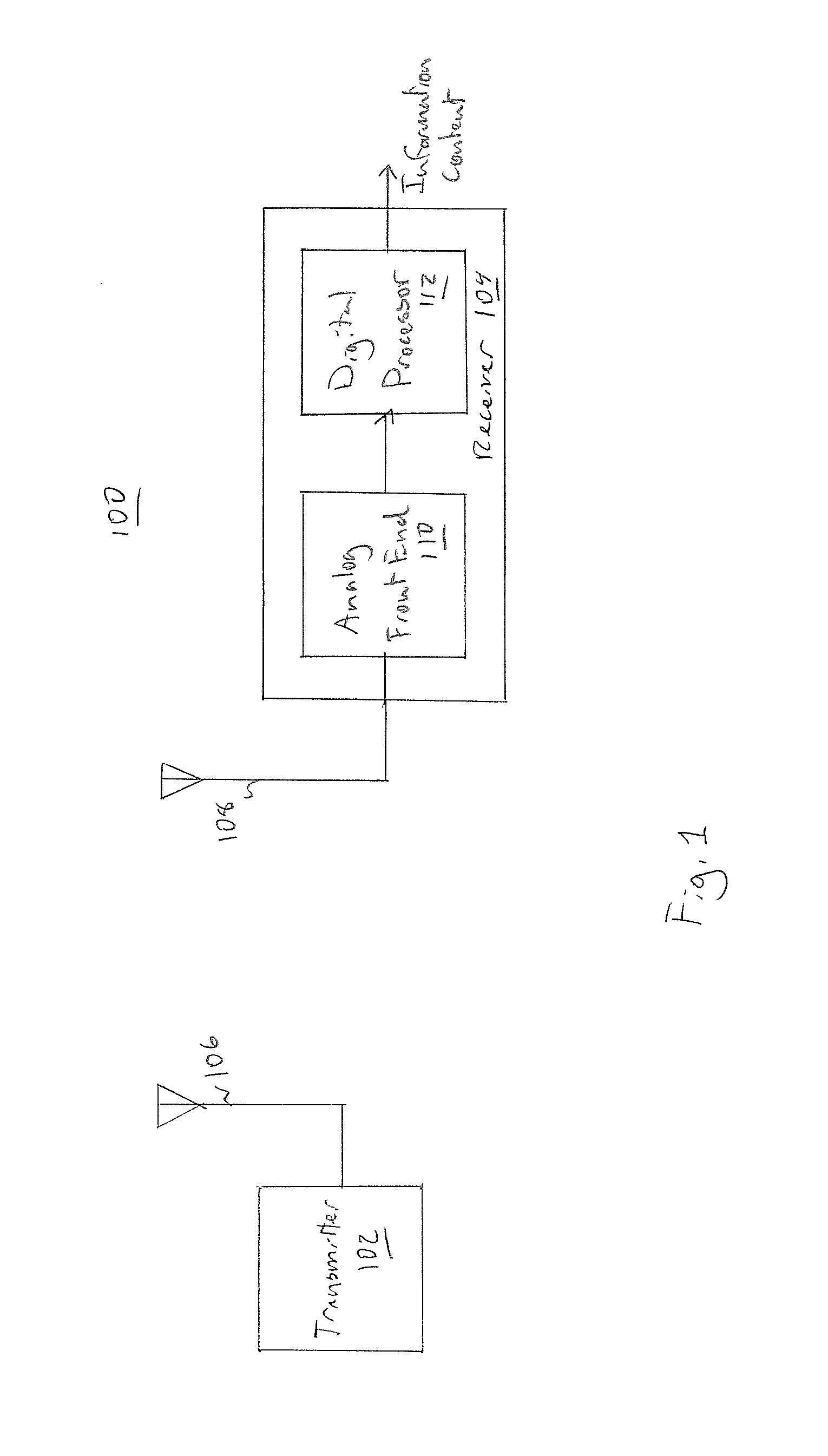

Synchronization in a multiple-input/multiple-output (MIMO) orthogonal frequency division multiplexing (OFDM) system for wireless applications

ActiveUS7009931B2Spatial transmit diversityFrequency-division multiplexSampling clock offsetFrequency-division multiplexing

Methods and apparatus are described for time synchronizing a receiver to orthogonal frequency division multiplexing (OFDM) signals in a multiple-input / multiple-output (MIMO) system, the signals being transmitted from multiple transmitters and received at multiple receivers. The method includes determining the frequency offset and the sampling clock offset of the received signals.

Owner:APPLE INC

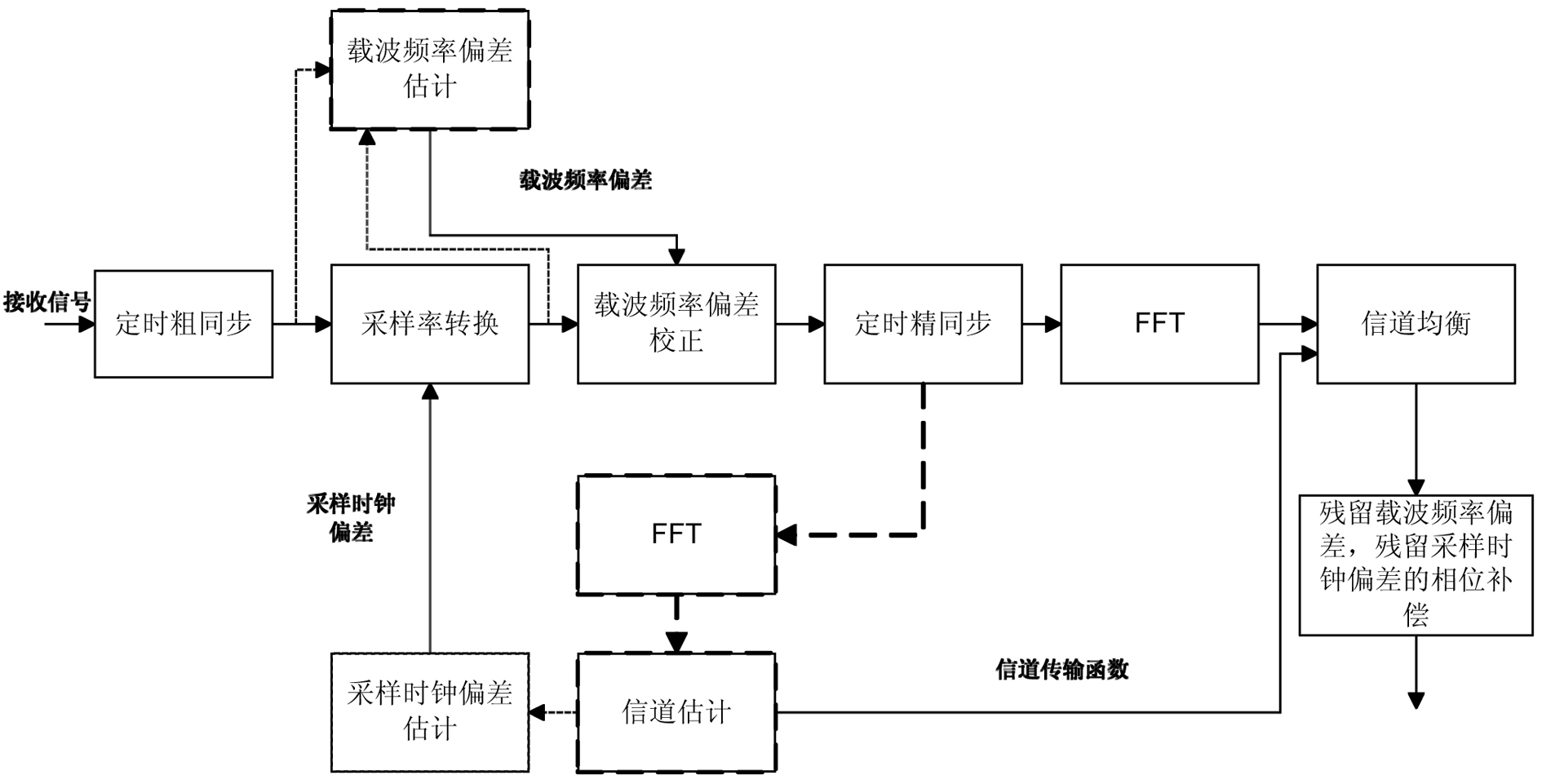

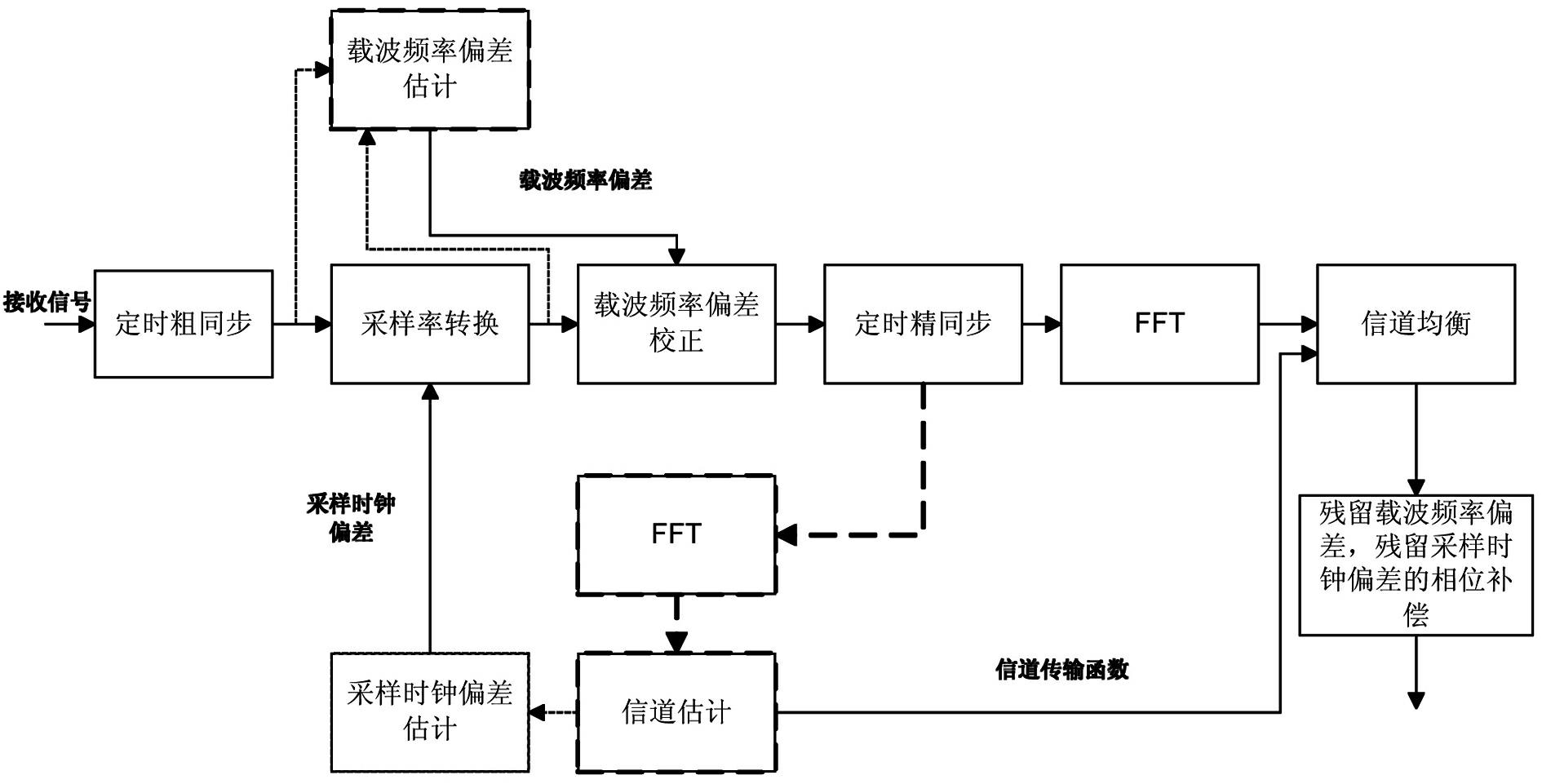

Synchronized method of orthogonal frequency division multiplexing (OFDM) system

InactiveCN102075486AAvoid the impact of timing fine synchronizationMeet needsMulti-frequency code systemsCarrier frequency offsetCarrier signal

The invention provides a synchronized method of an orthogonal frequency division multiplexing (OFDM) system. The invention discloses an associated synchronized method of frame synchronization, carrier frequency synchronization and sampling clock synchronization. Carrier frequency offset estimation, channel estimation and fine estimation of symbol timing offset are performed again after sampling clock offset correction is finished, thereby avoiding influences of sampling clock offset on the carrier frequency offset estimation, the channel estimation and the fine estimation of the symbol timing offset, compensating phase deflection caused by the residual carrier frequency offset and the sampling clock offset simultaneously, greatly improving the synchronized performance, and meeting the demands of a high-order modulated system. In addition, due to aiming at a low time-varying channel, the channel estimation is required to be performed once only, thereby reliving the complexity of the system.

Owner:深圳市阿派斯实业有限公司

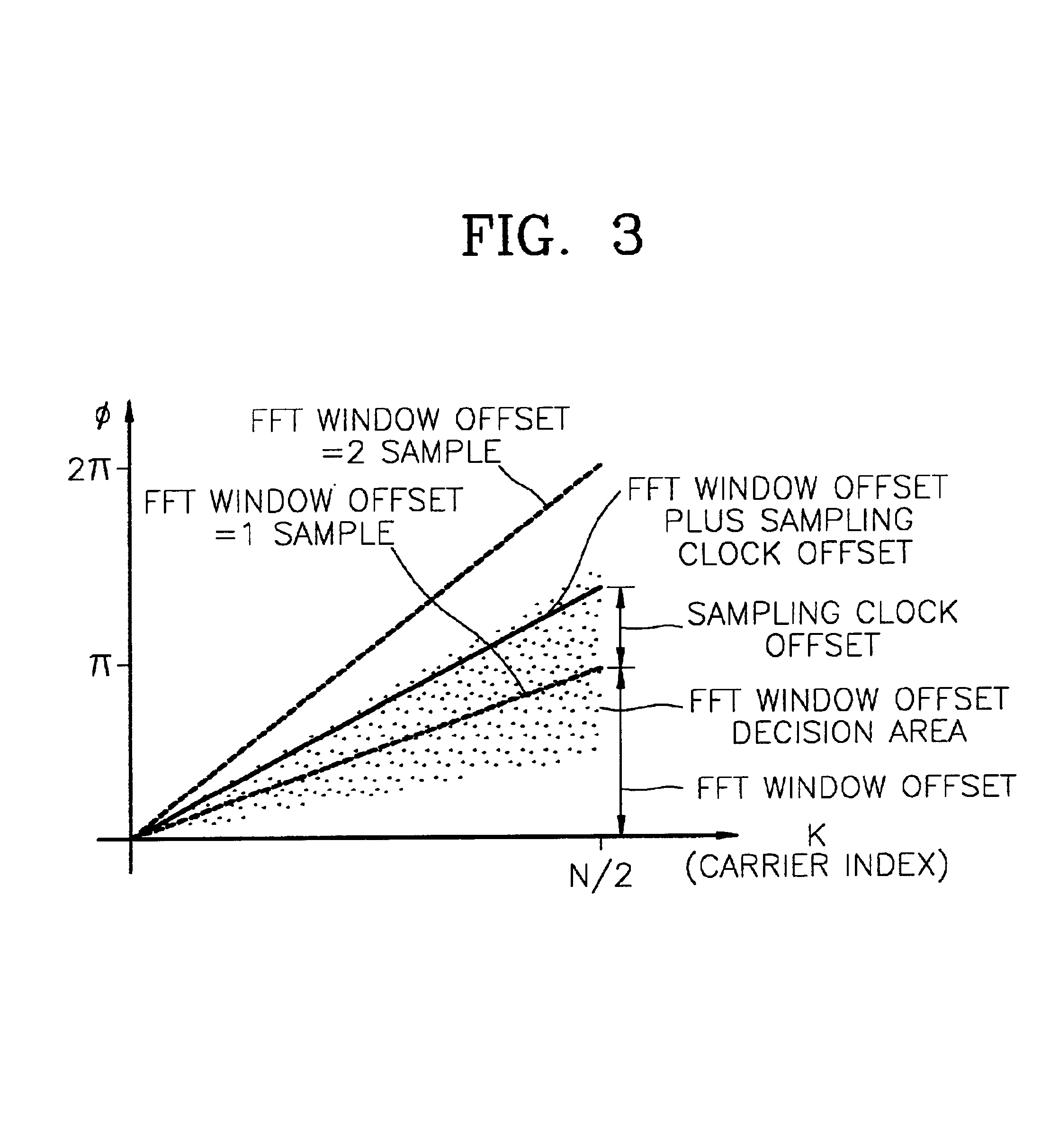

Orthogonal frequency division multiplexing receiver where FFT Window position recovery interlocks with sampling clock adjustment and method thereof

InactiveUS6853616B1Transmission control/equlisationSecret communicationPhase differenceFourier transform on finite groups

An OFDM receiver for interlocking FFT window position recovery with sampling clock control, and a method thereof are provided. This method includes the steps of: extracting a pilot signal from fast-Fourier-transformed OFDM received signals, and detecting inter-pilot phase differences; averaging the detected phase differences for a symbol and normalizing the mean phase difference by dividing it into reference values corresponding to phase differences generated when FFT window errors of at least one sample exist; and simultaneously controlling the FFT window position offset using a value obtained by rounding off the normalized value, and the sampling clock offset using the difference between the round-off value and the normalized value.

Owner:SAMSUNG ELECTRONICS CO LTD

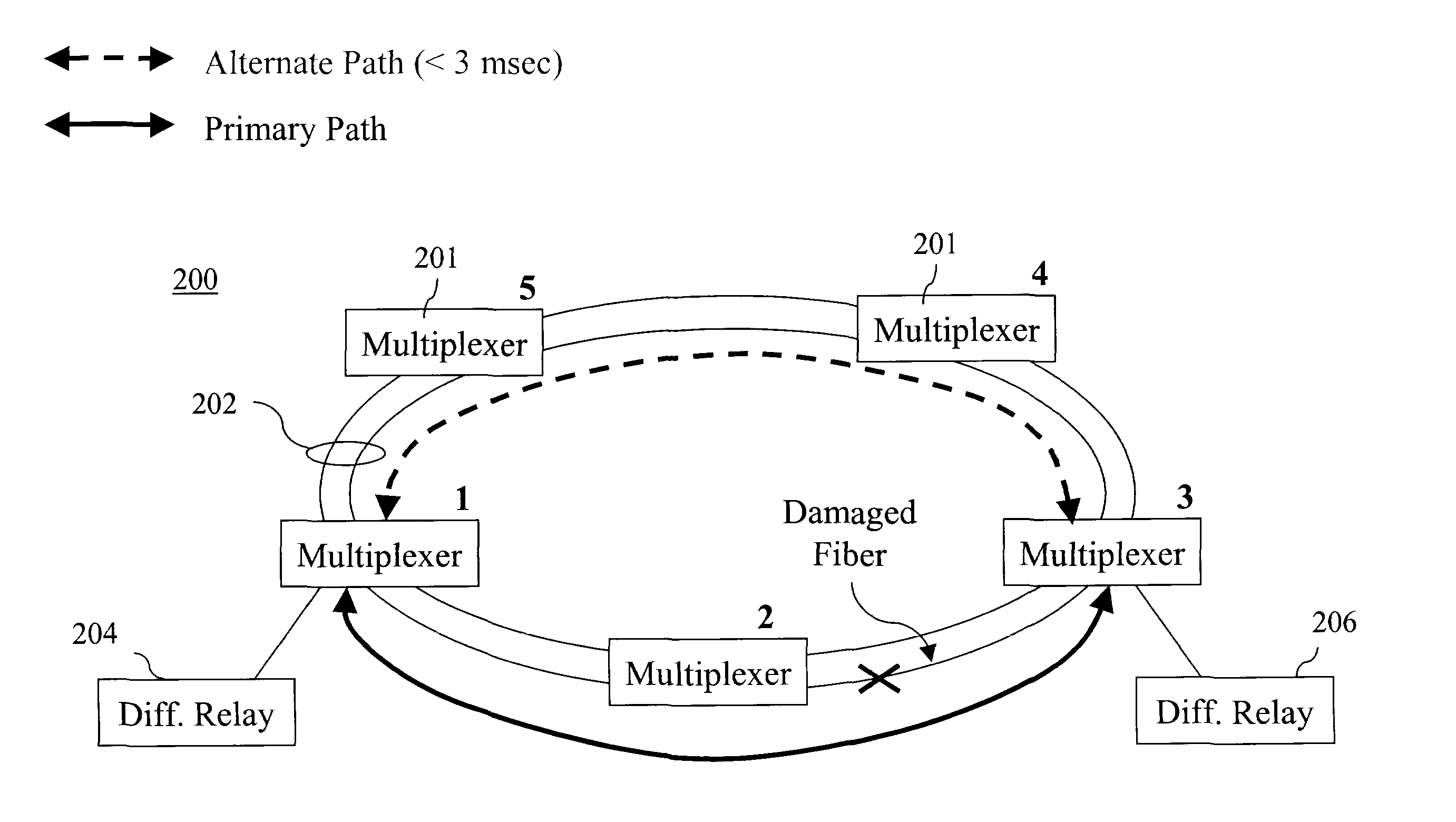

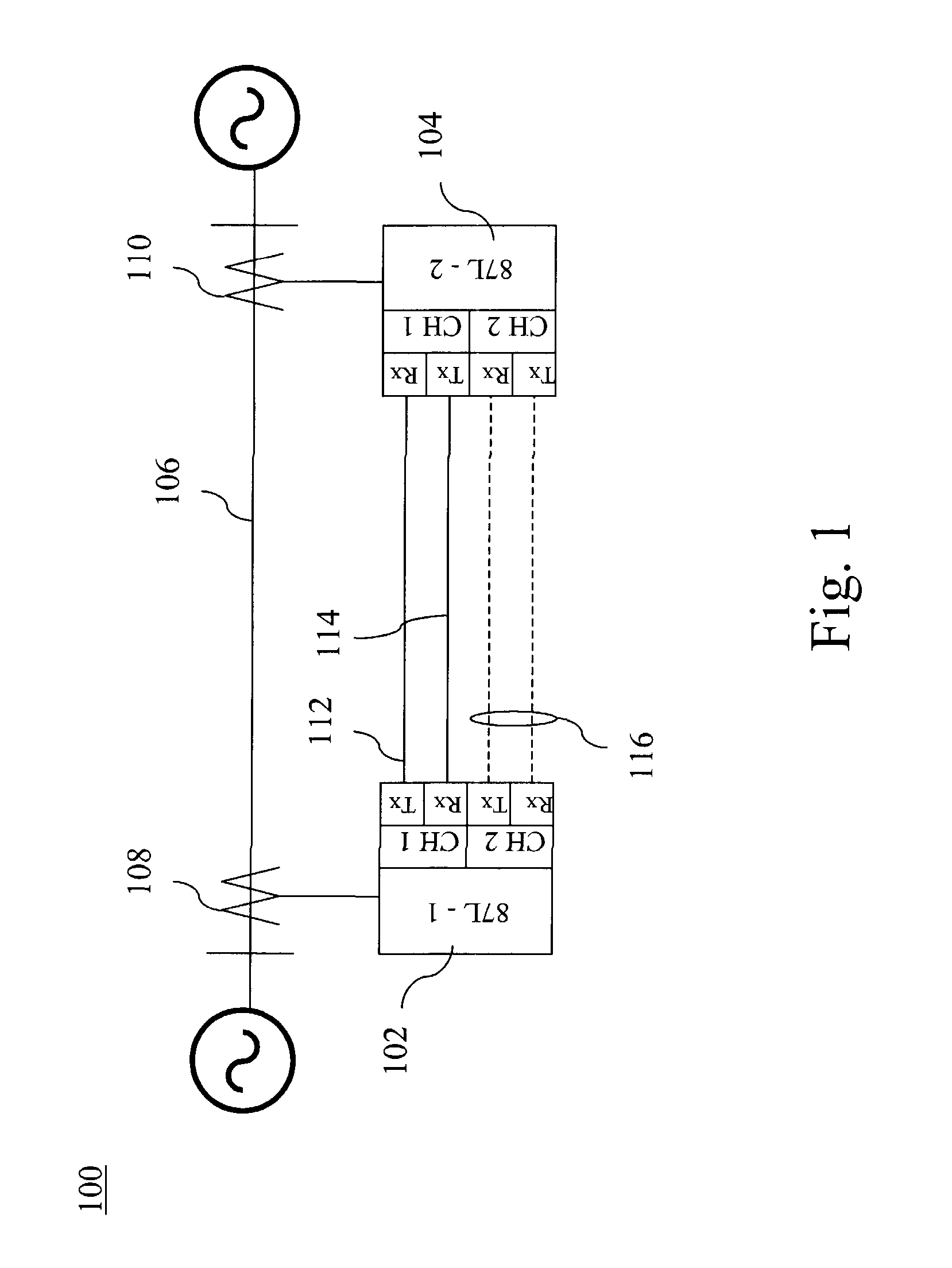

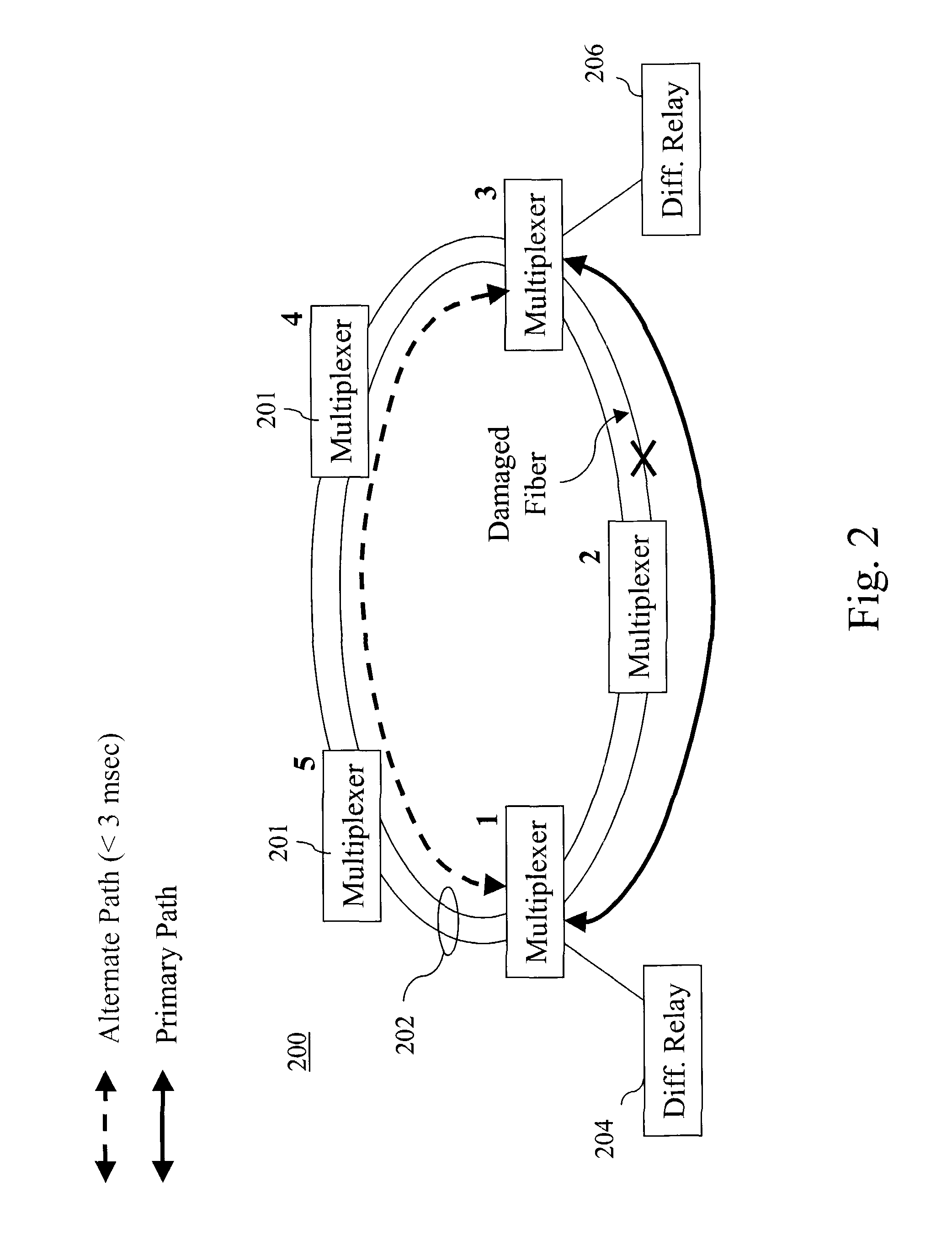

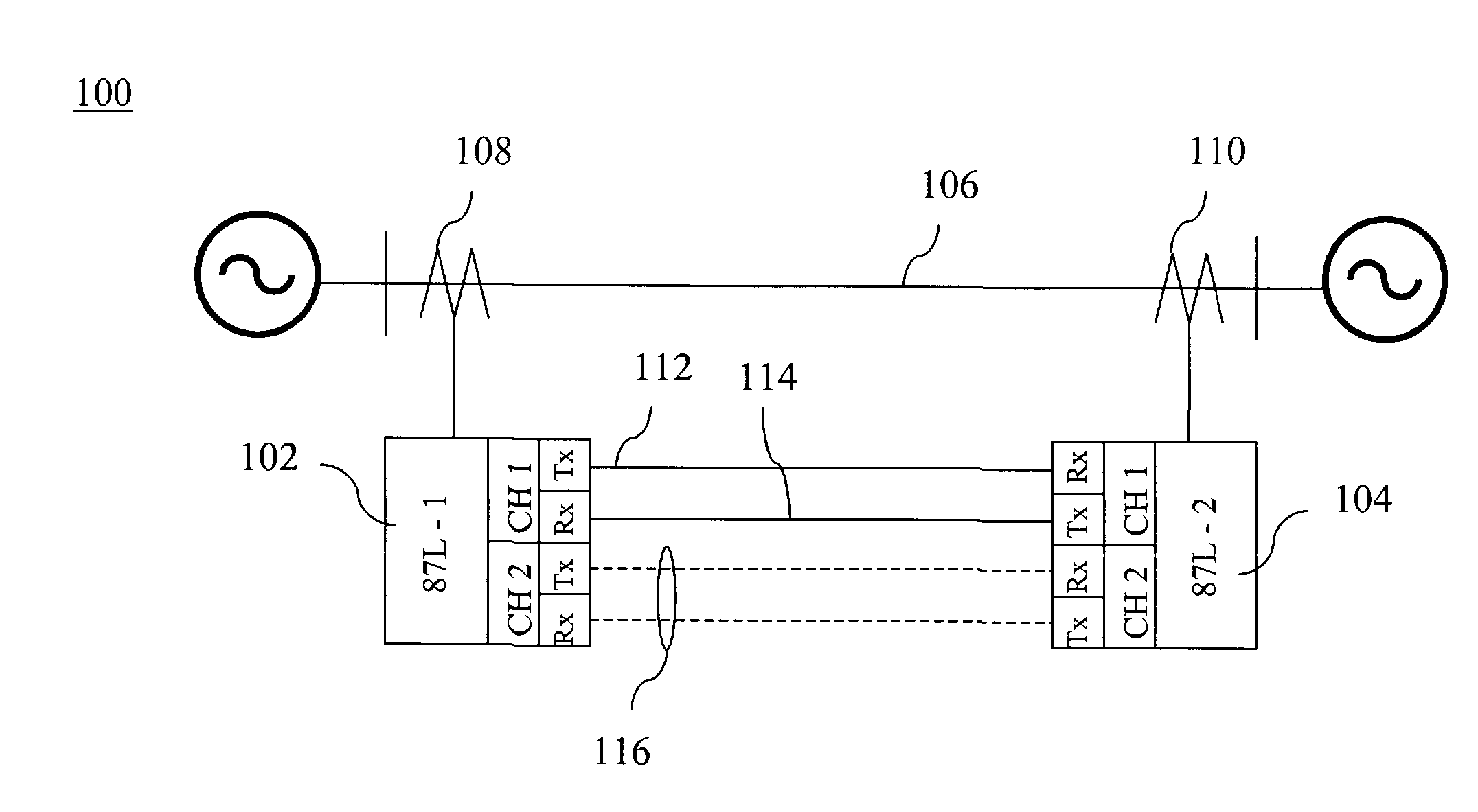

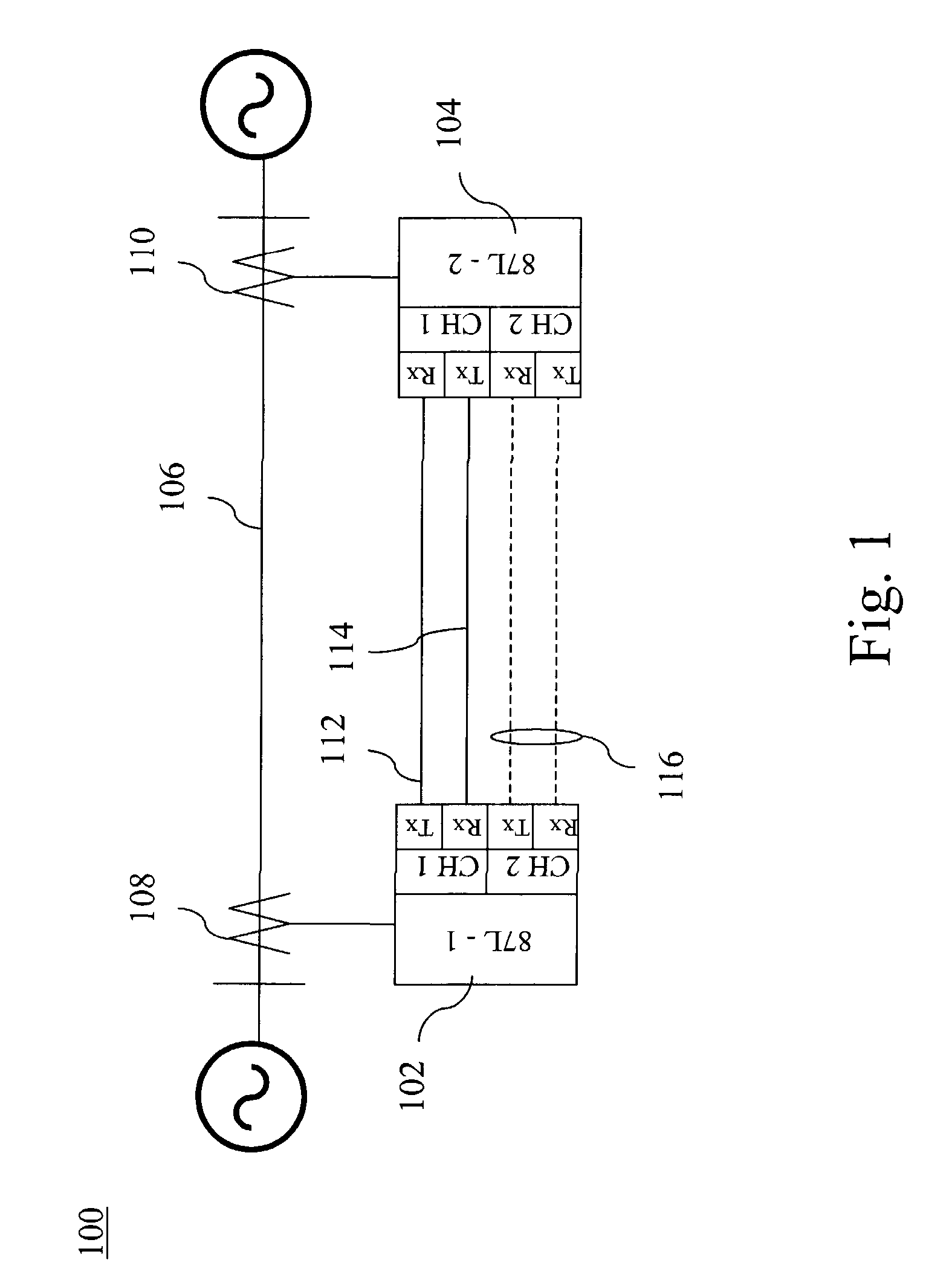

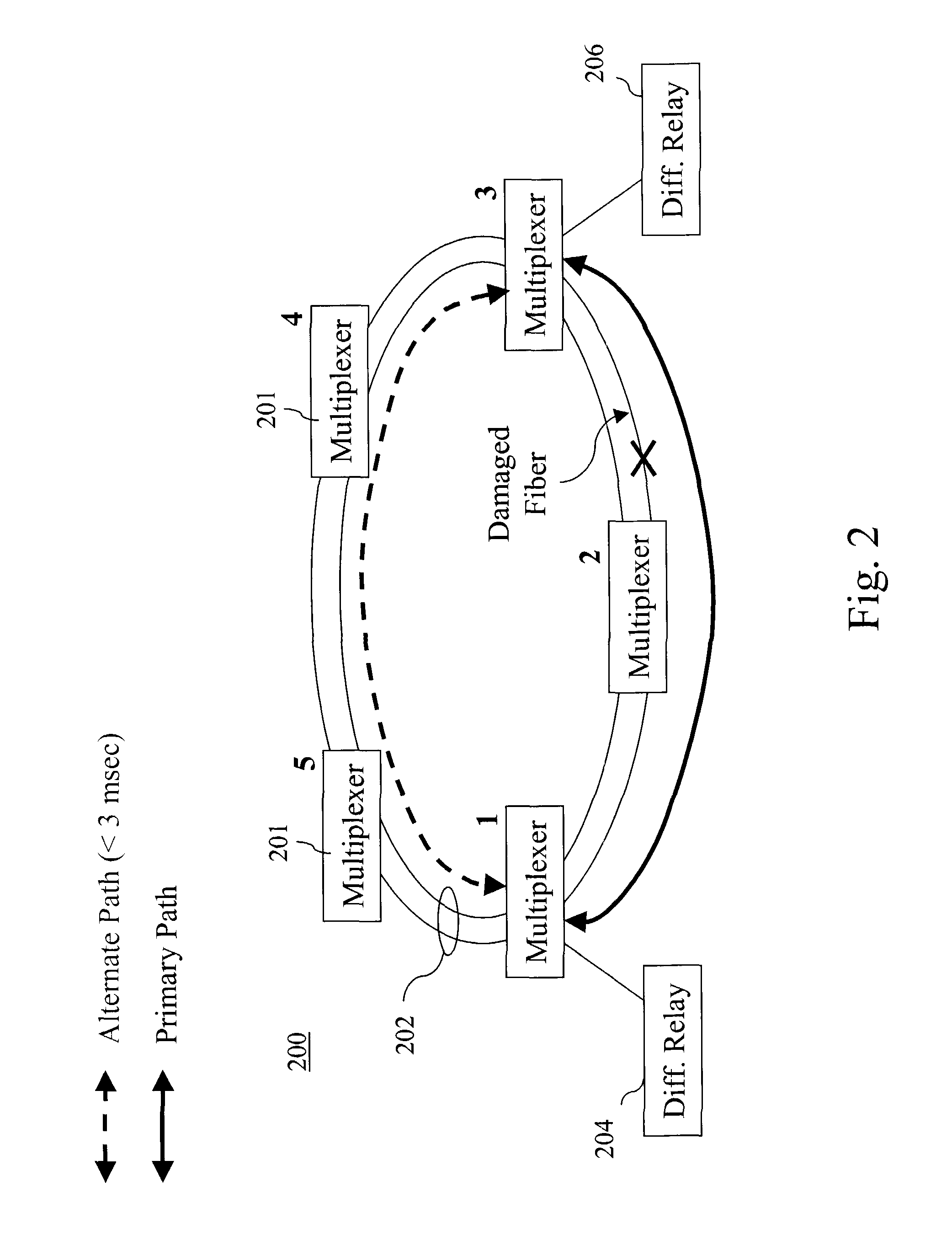

Method and system for communications channel delay asymmetry compensation using global positioning systems

ActiveUS20050036254A1Time-division multiplexEmergency protective arrangements for automatic disconnectionSampling clock offsetChannel asymmetry

A method for compensating for communications channel delay asymmetry in a current differential protection system includes determining an apparent sampling clock offset for a communications channel, the apparent sampling clock offset between a first sampling clock and a second sampling clock configured within the current differential protection system. An apparent global positioning system (GPS) clock offset is determined for the communications channel, the apparent GPS clock offset between a plurality of GPS time stamps corresponding to the first and said second sampling clocks. A compensated clock offset is determined by subtracting the apparent GPS clock offset from the apparent sampling clock offset so as to cancel out a channel asymmetry component of deviation in the apparent GPS and sampling clock off-sets.

Owner:GENERAL ELECTRIC CO

Synchronous estimation method and system for orthogonal frequency division multiplexing technique

InactiveCN101299737AAvoid the effects of bit errorsHigh precisionRadio transmission for post communicationMulti-frequency code systemsMutual correlationEstimation methods

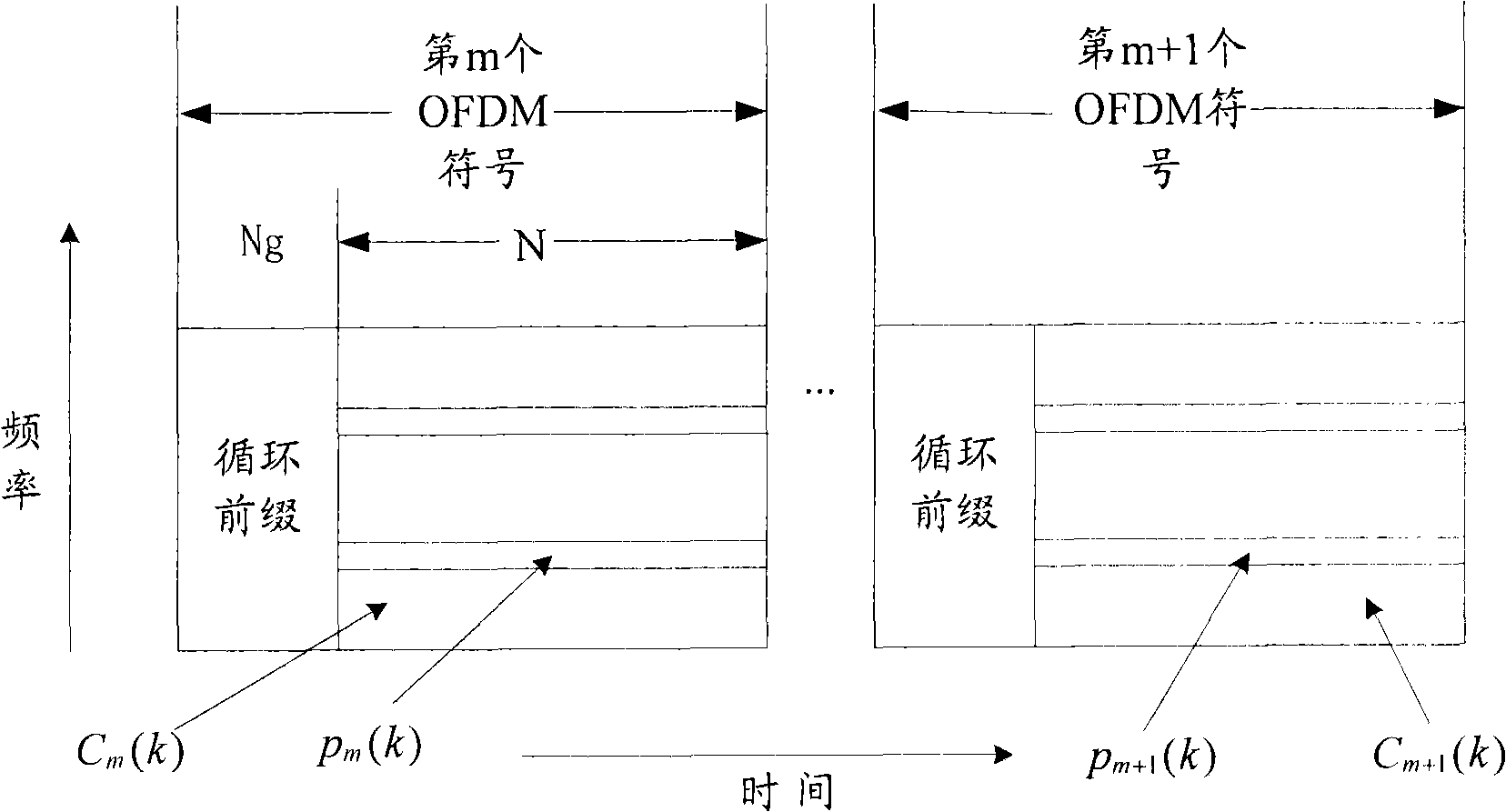

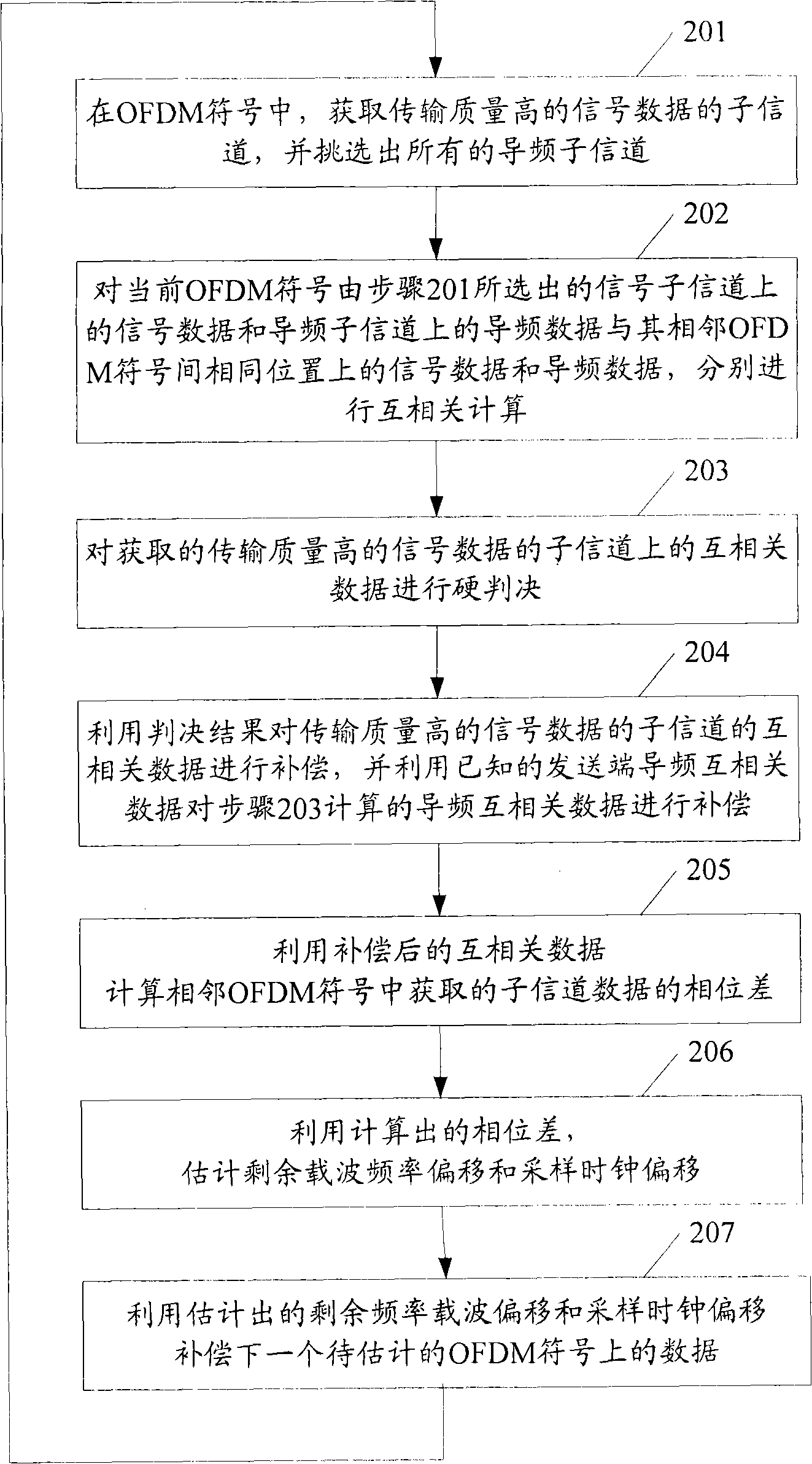

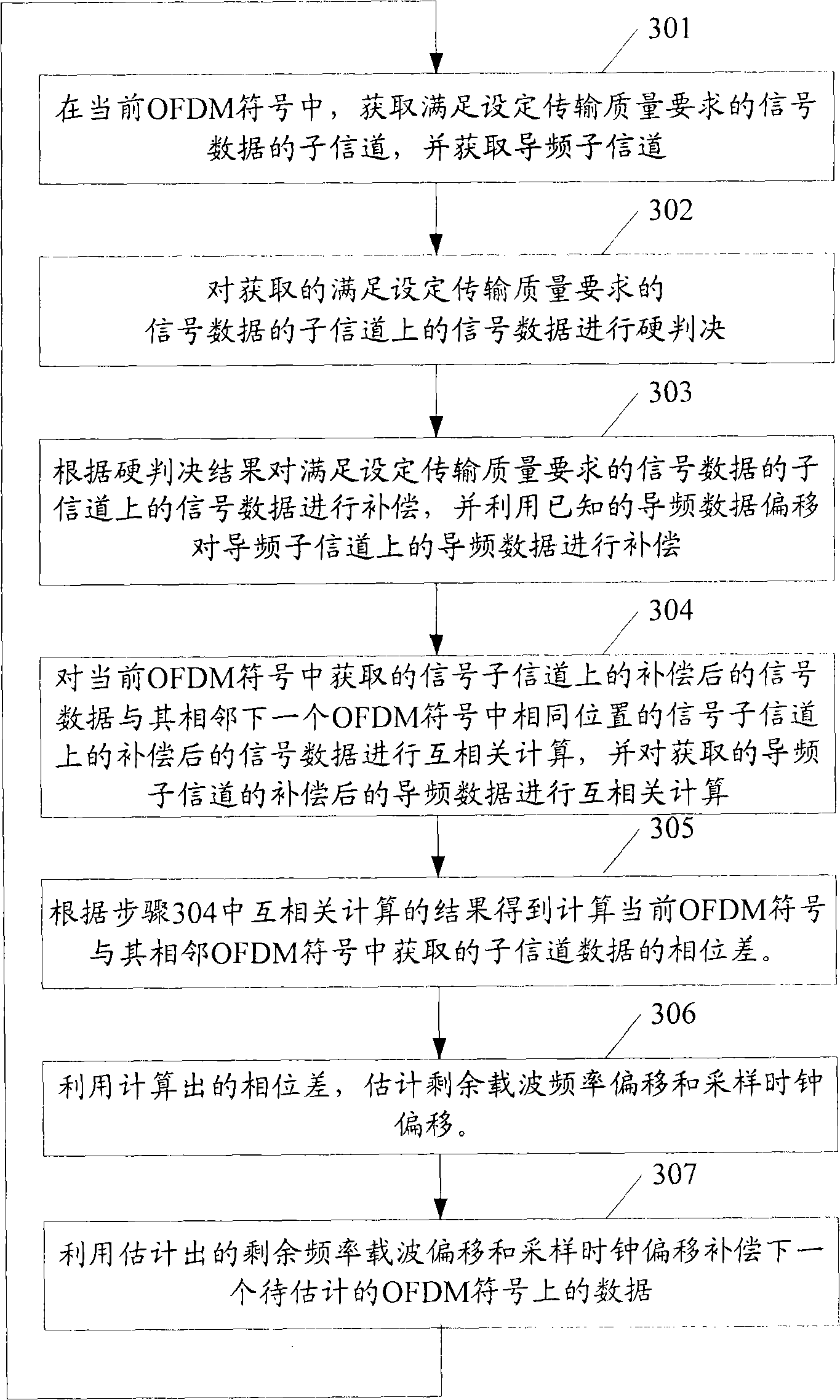

The invention provides an in-phase estimation method and a system of the orthogonal frequency division multiplexing (OFDM) technology, wherein the method includes: obtaining the sub-channels which satisfy the given transmission quality in the OFDM symbols; computing the phase offset between the data on the obtained sub-channels and the data on the sub-channels with the same position in the adjacent OFDM symbols; estimating the residual carrier frequency shift and the sampling clock shift of the current OFDM symbols. The method and the system estimates the residual carrier frequency shift and the sampling clock shift through the mutual correlation data on the sub-channels which satisfy the given transmission quality, overcomes the effect of the sub-channel with bad quality to generate the error code, advances the precision of the in-phase estimation to a great extent.

Owner:HUAWEI TECH CO LTD +1

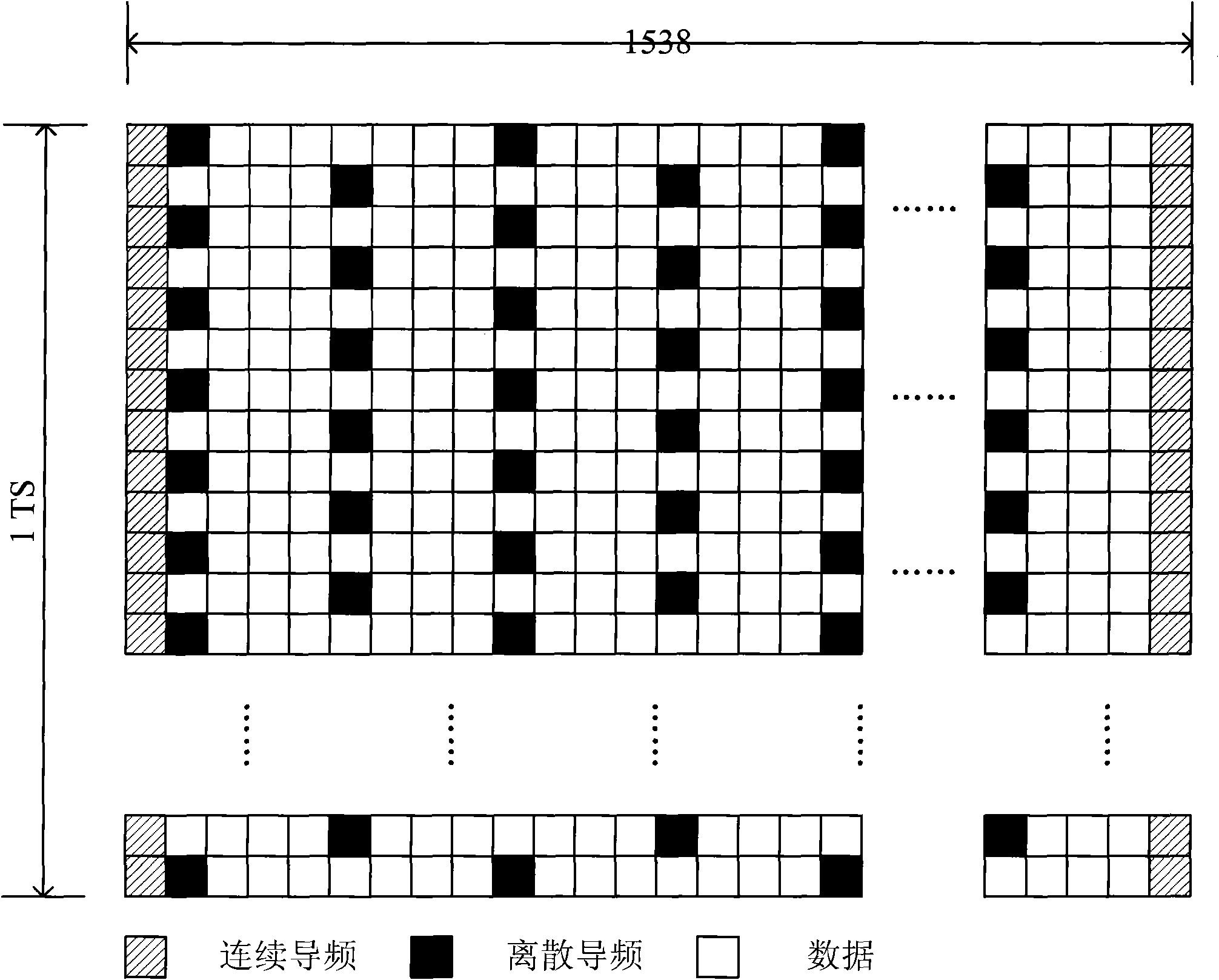

Method for estimating and compensating sampling clock offset and receiving device

ActiveCN101841509AFast adjustmentGuaranteed robustnessMulti-frequency code systemsStable stateTwo step

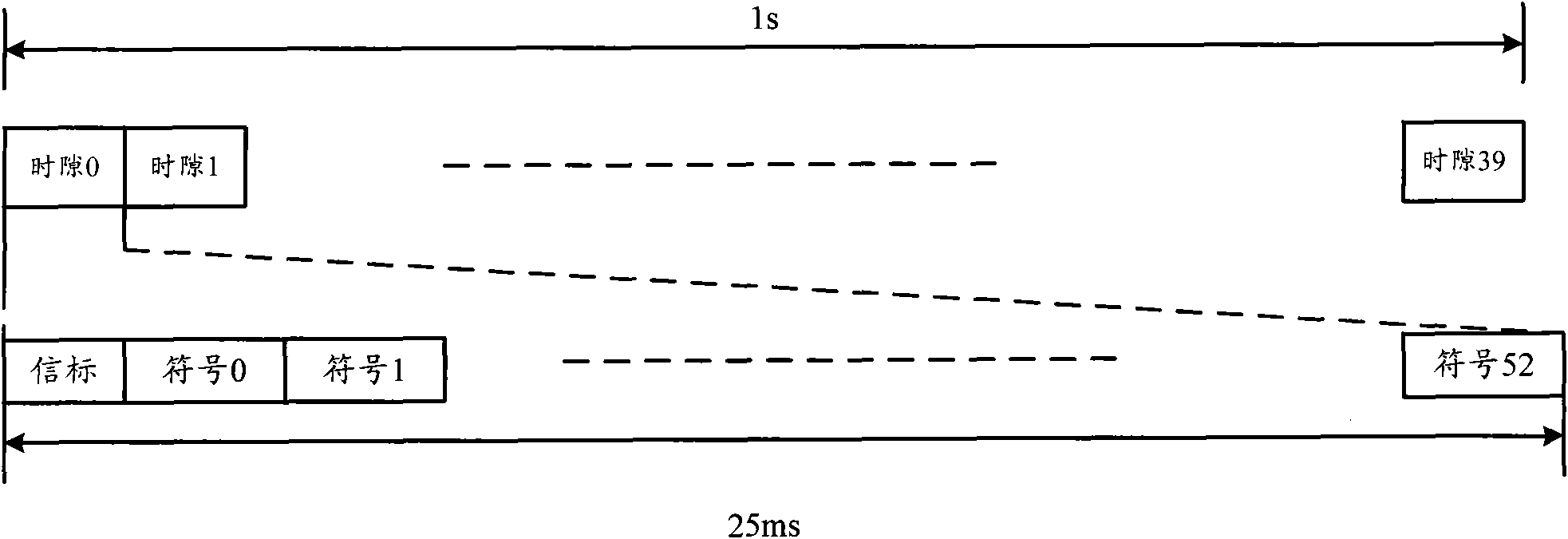

The invention relates to the field of communication, in particular to a method for estimating and compensating a sampling clock offset and a receiving device. In the invention, a sampling clock offset is estimated and comprehended by two steps. In the first step, the sampling clock offset is sampled according to two synchronous symbols in a time slot and compensated in the next time slot according to an estimating result; and in the second step, the sampling clock offset of every two adjacent data symbols in the time slot is finely estimated by utilizing the continuous pilot frequency symmetry of the data symbols and the sampling clock offset of the currently received data symbols is compensated according to a current estimating result after the sampling clock offset of every two adjacent data symbols is estimated every time. By the invention, the adjusting speed is greatly improved, and the system can rapidly enter a stable state.

Owner:SPREADTRUM COMM (SHANGHAI) CO LTD

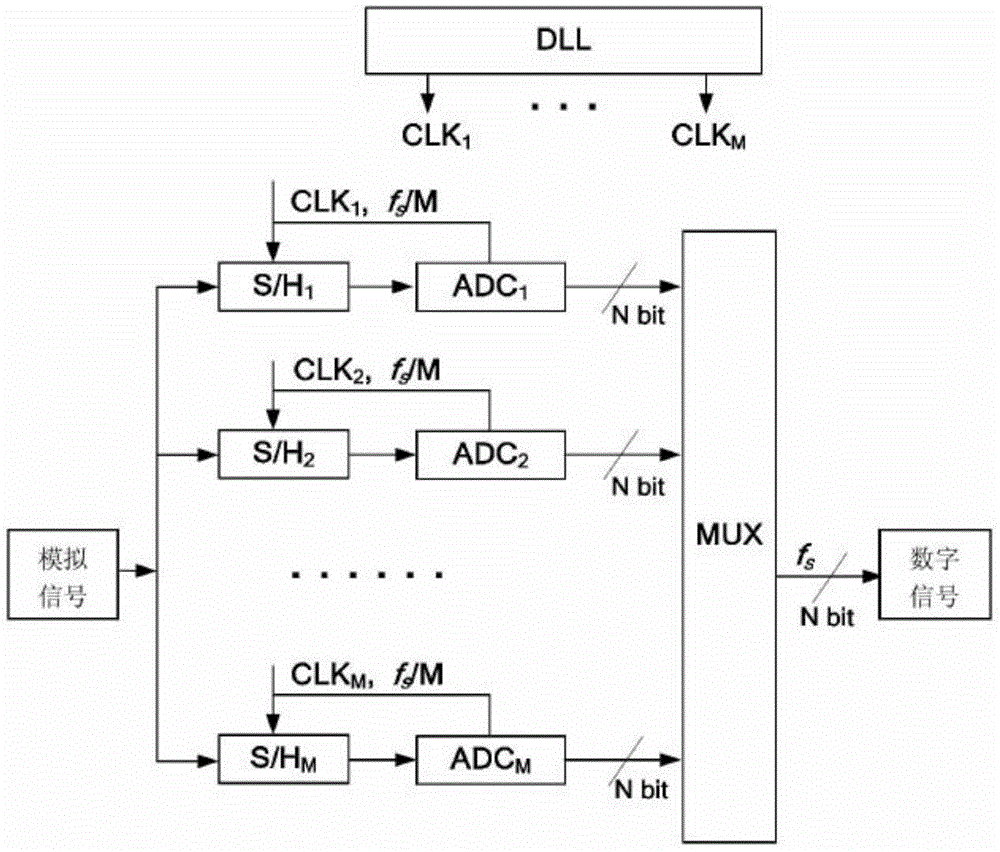

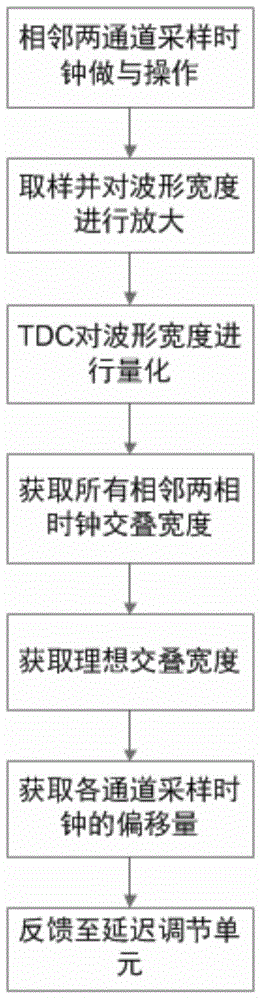

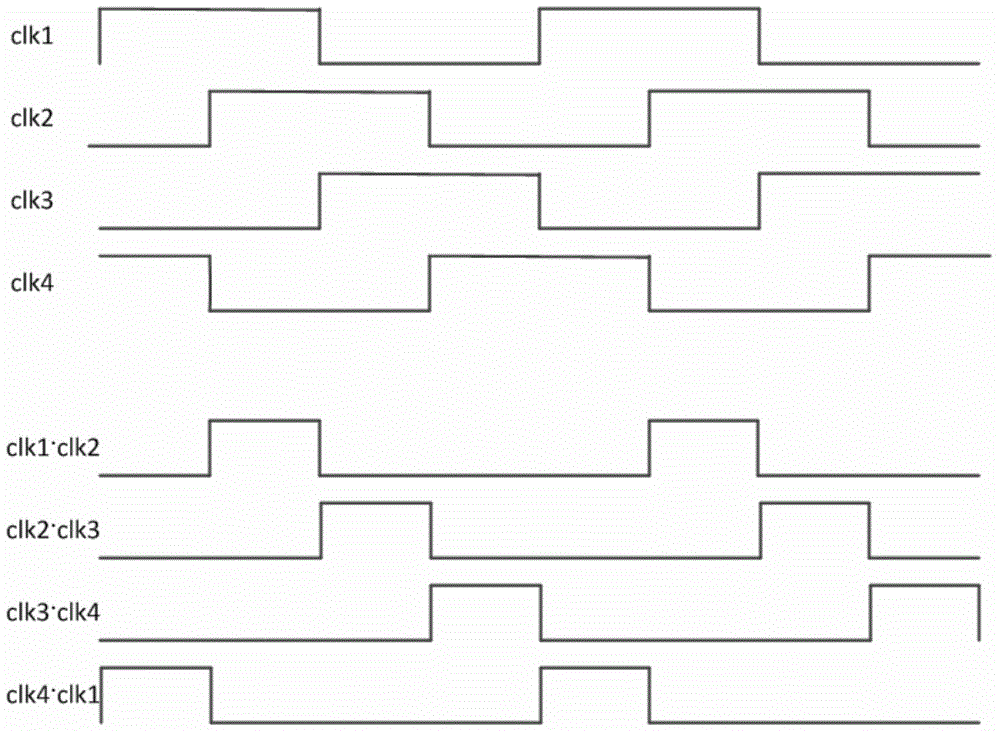

Sampling clock?mismatch?background?correction method based on time-to-digital?converter

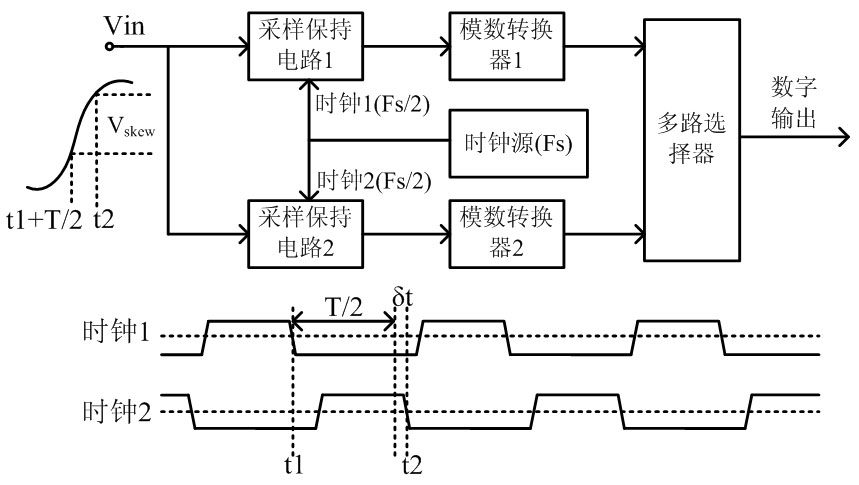

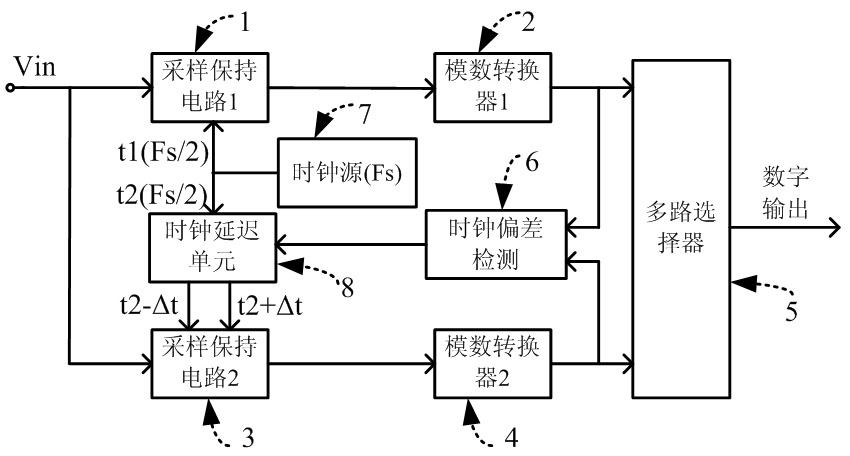

InactiveCN103825612AImprove and guarantee performanceDoes not affect normal workAnalogue/digital conversion calibration/testingClock correctionTime interleaved

The invention relates to a clock?correction technology in the field of microelectronics and discloses a sampling clock?mismatch?background?correction method based on a time-to-digital?converter, which is used for carrying out background?correction on mismatch of a sampling clock?of a time-interleaved analog-to-digital converter and improving performances of the time-interleaved analog-to-digital converter. AND operation is carried out on each adjacent two-phase sampling clock of the time-interleaved analog-to-digital converter, the overlapping part waveform Ai of the adjacent sampling clocks is obtained, a?time domain?waveform width?amplifier is adopted to amplify the width of Ai to obtain Ci, the time-to-digital?converter is used for quantifying Ci to obtain Di, the average value of Di D represents a digital code corresponding to the ideal overlapping width of adjacent two-phase sampling clocks, sampling clock offset in the i channel is obtained through calculation Ei=Di-D, and multiphase?sampling?clock?mismatch?correction can then be realized through Ei statistics and feeding the statistical result to a clock delay?adjustment unit. The sampling clock?mismatch?background?correction method based on time-to-digital?converter is particularly suitable for mismatch correction on the sampling clock of the time-interleaved analog-to-digital converter.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

Method and system for communications channel delay asymmetry compensation using global positioning systems

ActiveUS7126800B2Time-division multiplexEmergency protective arrangements for automatic disconnectionClock offsetGlobal Positioning System

A method for compensating for communications channel delay asymmetry in a current differential protection system includes determining an apparent sampling clock offset for a communications channel, the apparent sampling clock offset between a first sampling clock and a second sampling clock configured within the current differential protection system. An apparent global positioning system (GPS) clock offset is determined for the communications channel, the apparent GPS clock offset between a plurality of GPS time stamps corresponding to the first and said second sampling clocks. A compensated clock offset is determined by subtracting the apparent GPS clock offset from the apparent sampling clock offset so as to cancel out a channel asymmetry component of deviation in the apparent GPS and sampling clock off-sets.

Owner:GENERAL ELECTRIC CO

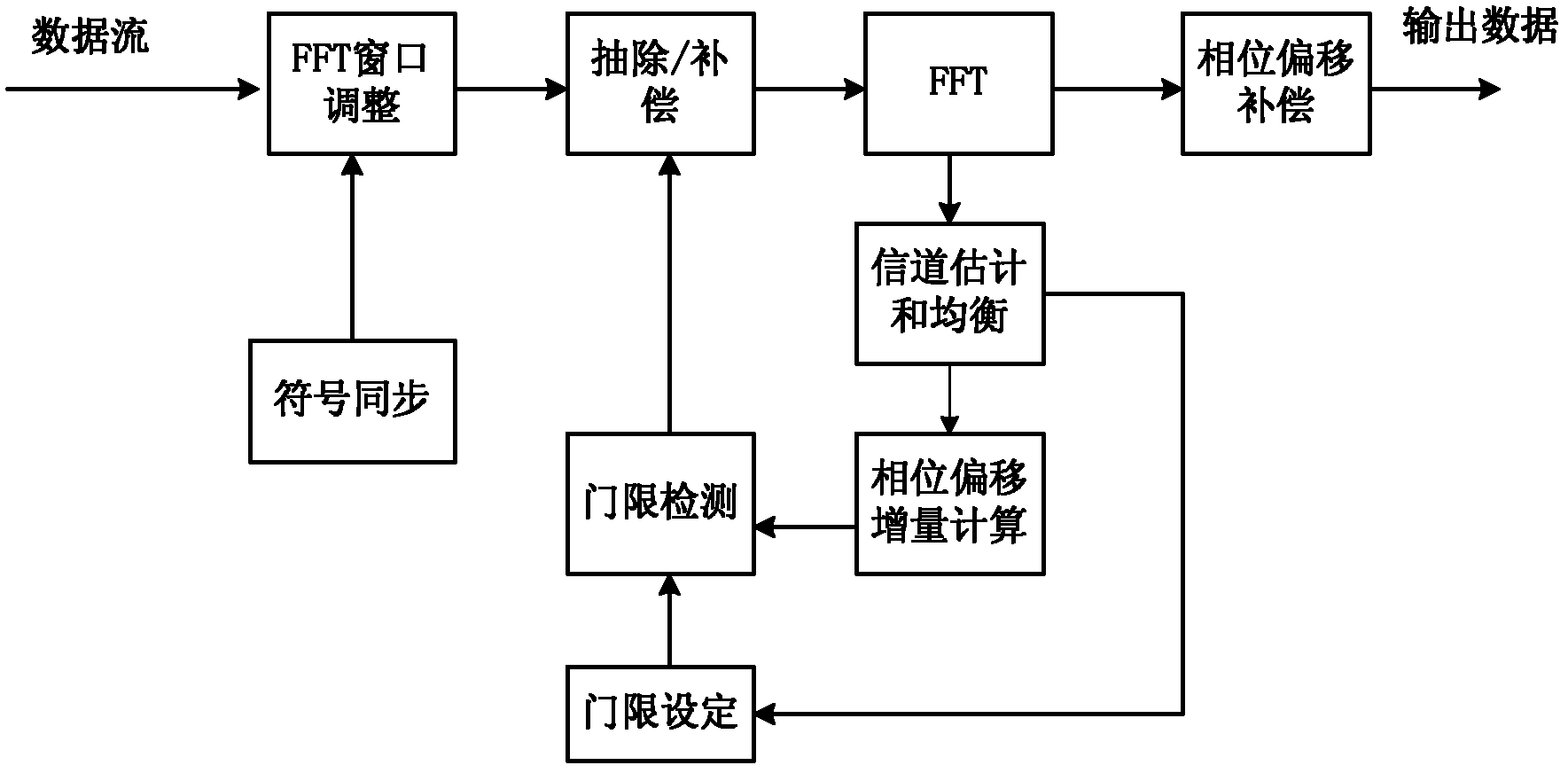

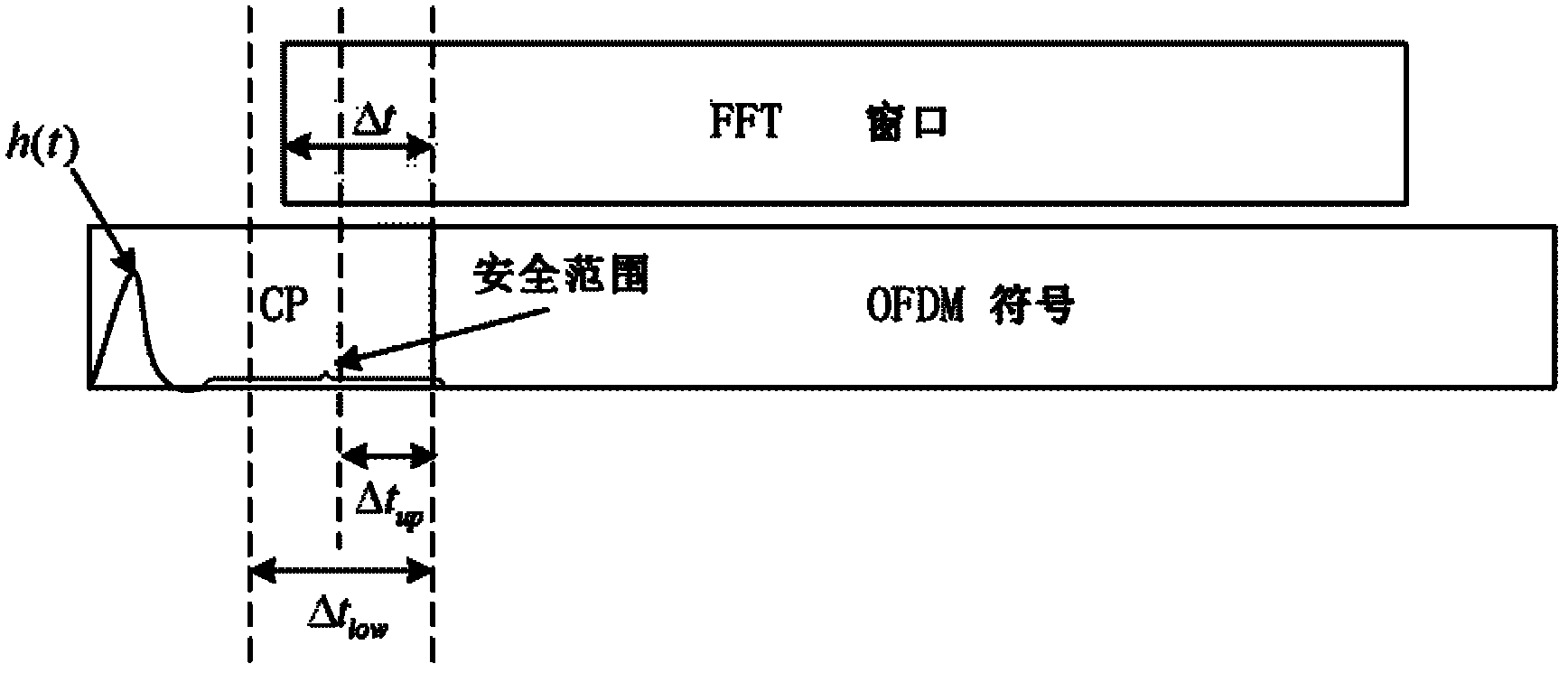

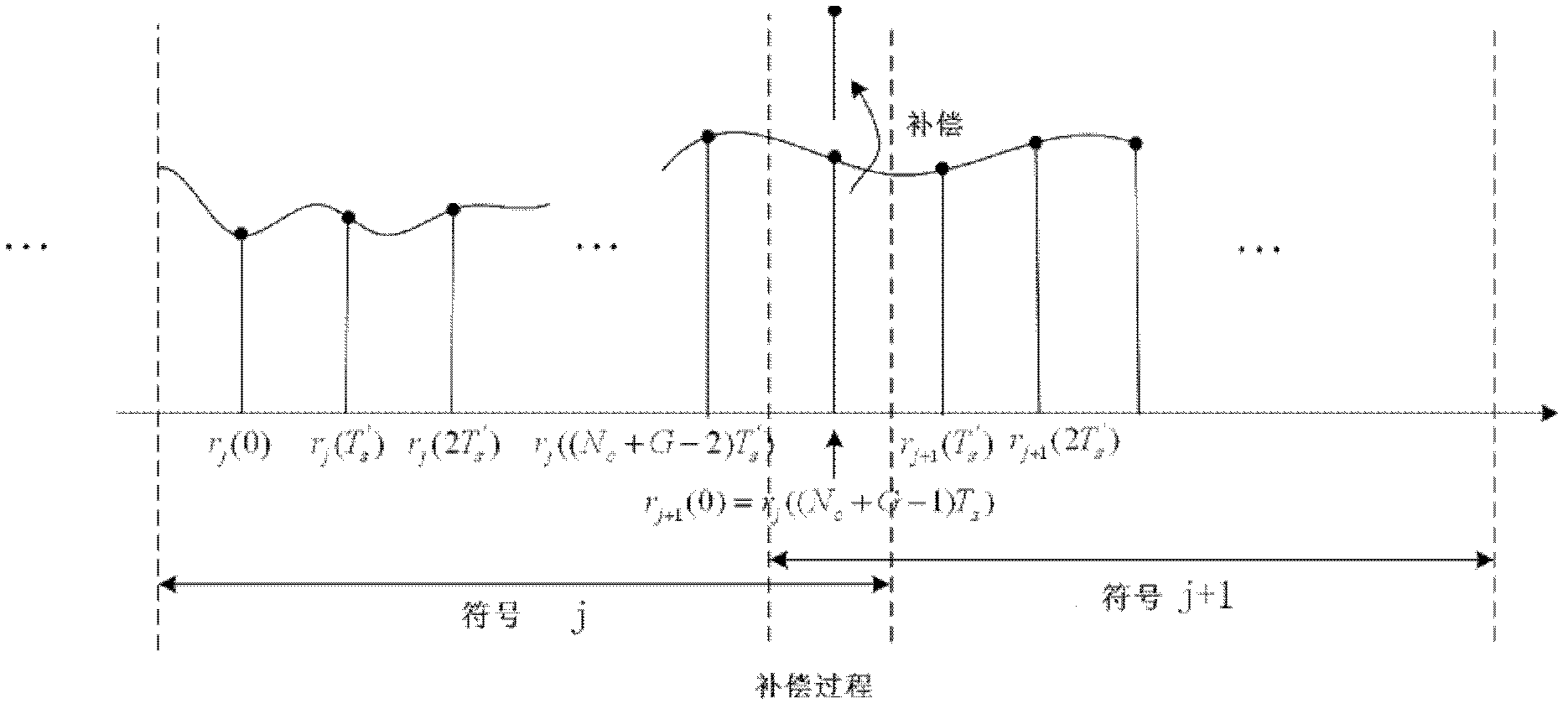

Extraction/compensation mechanism-based sampling clock synchronization method in OFDM system

ActiveCN102333370AReduce deflectionOvercome costsSynchronisation arrangementBaseband system detailsCarrier signalPhase deviation

The invention discloses an extraction / compensation mechanism-based sampling clock synchronization method in an OFDM (Orthogonal Frequency Division Multiplexing) system. The method combines a sampling clock skew estimation method based on pilot sub-carrier average phase deviation increment detection with an extraction / compensation clock synchronization compensation mechanism according to sampling clock skew quantity. The method is used for solving the problem of sampling time migration caused by mismatching of clock frequency in the analog / digital conversion process of a receiving end and a digital / analog conversion process of a transmitting end of the OFDM system, so that interference between OFDM sub-carriers and phase deviation of a constellation diagram after demodulation are effectively reduced. With the method, use of an expensive voltage-controlled oscillator is avoided, and decline of system performance caused by frequently searching an FFT (Fast Fourier Transform) window by a conventional symbol synchronization module is also avoided, so that the sampling clock synchronization method provided by the invention is low in hardware cost and high in efficiency.

Owner:SOUTH CHINA UNIV OF TECH

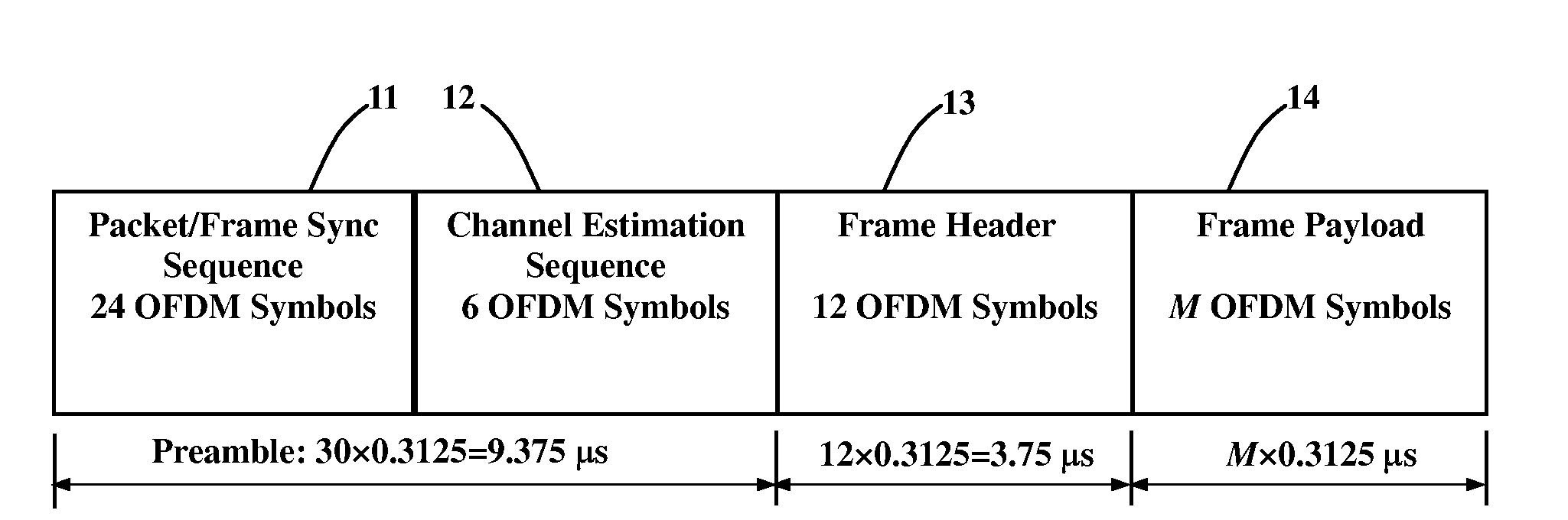

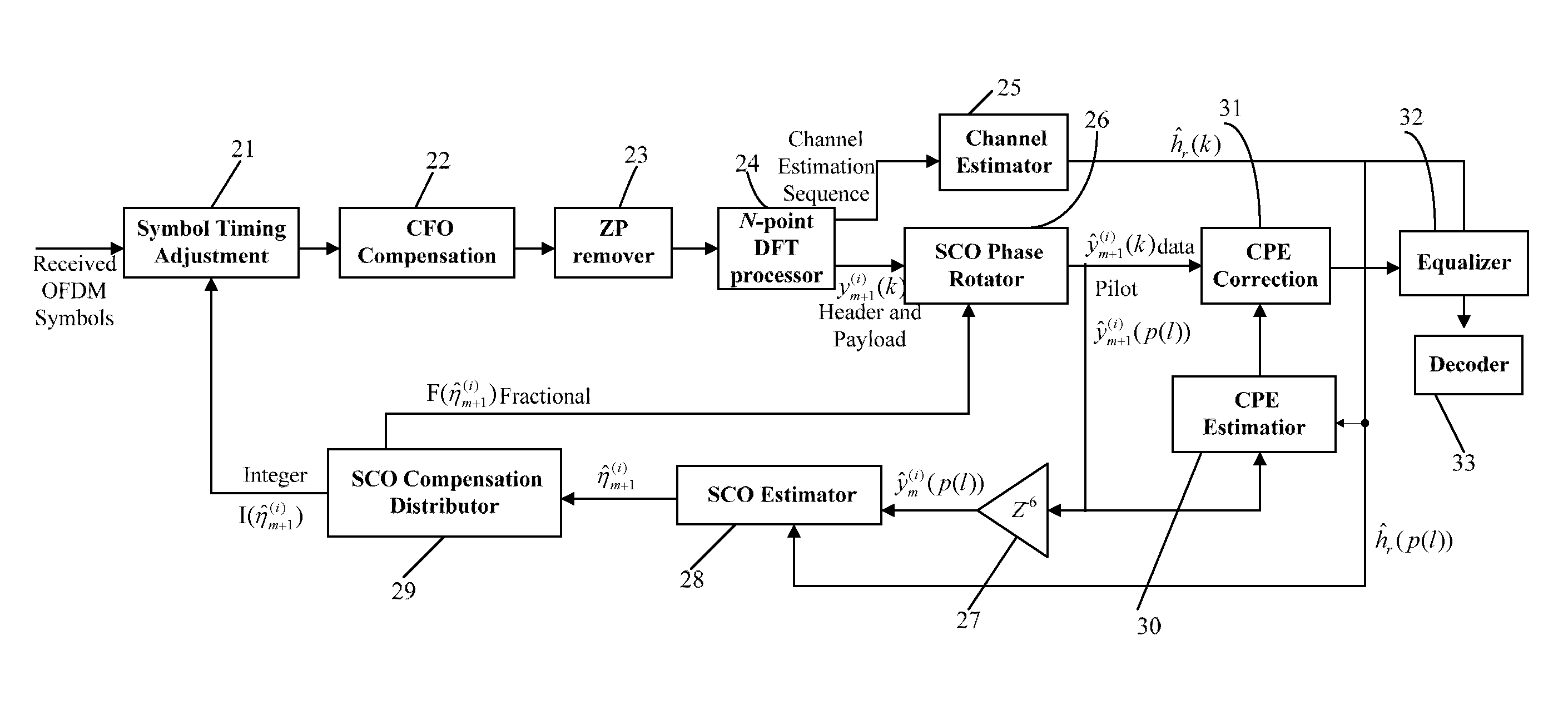

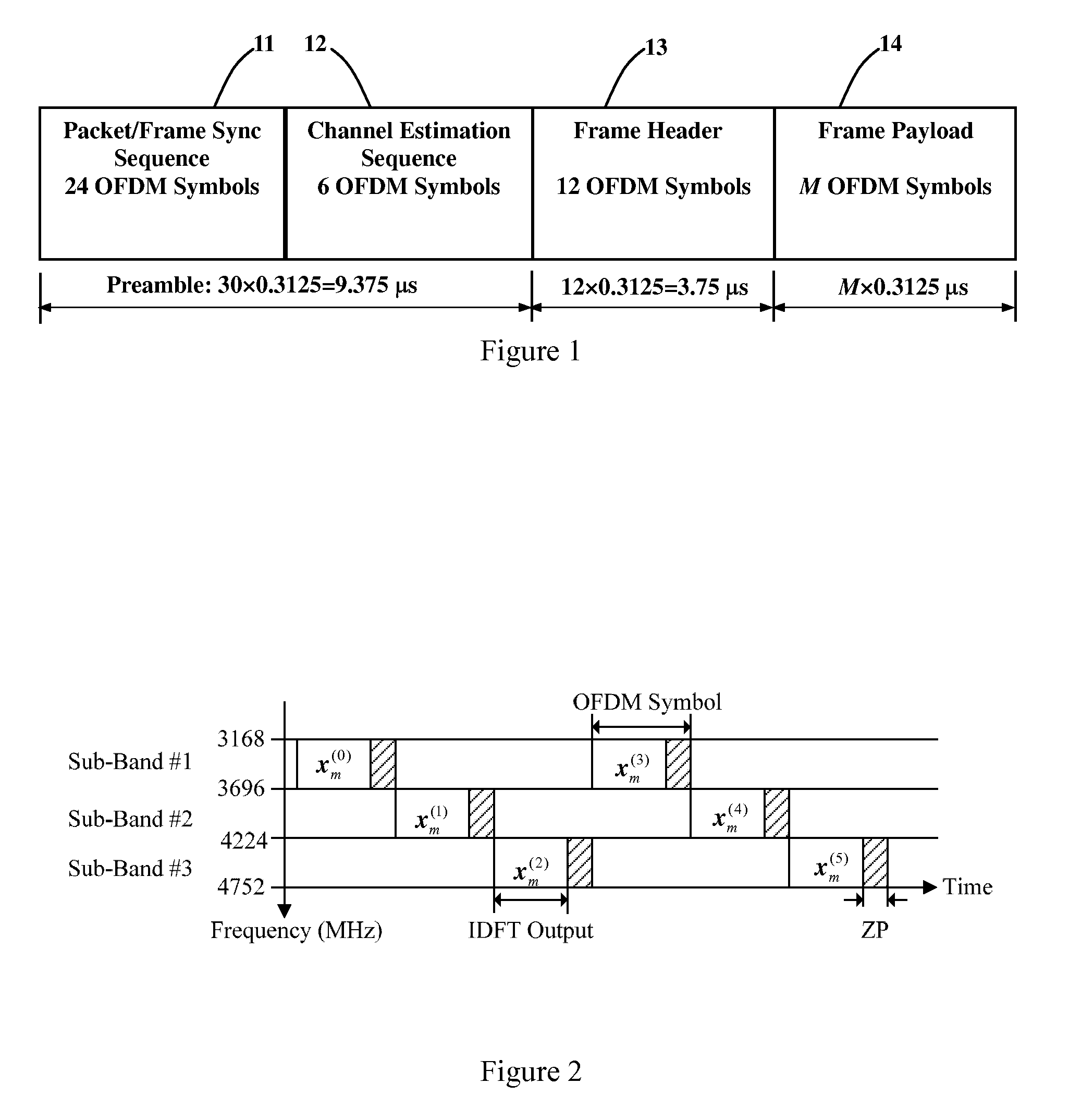

Apparatus and methods for estimating and compensating sampling clock offset

ActiveUS20090279421A1Reduce complexityImprove anti-interference abilitySecret communicationMulti-frequency code systemsPhase shiftedClock recovery

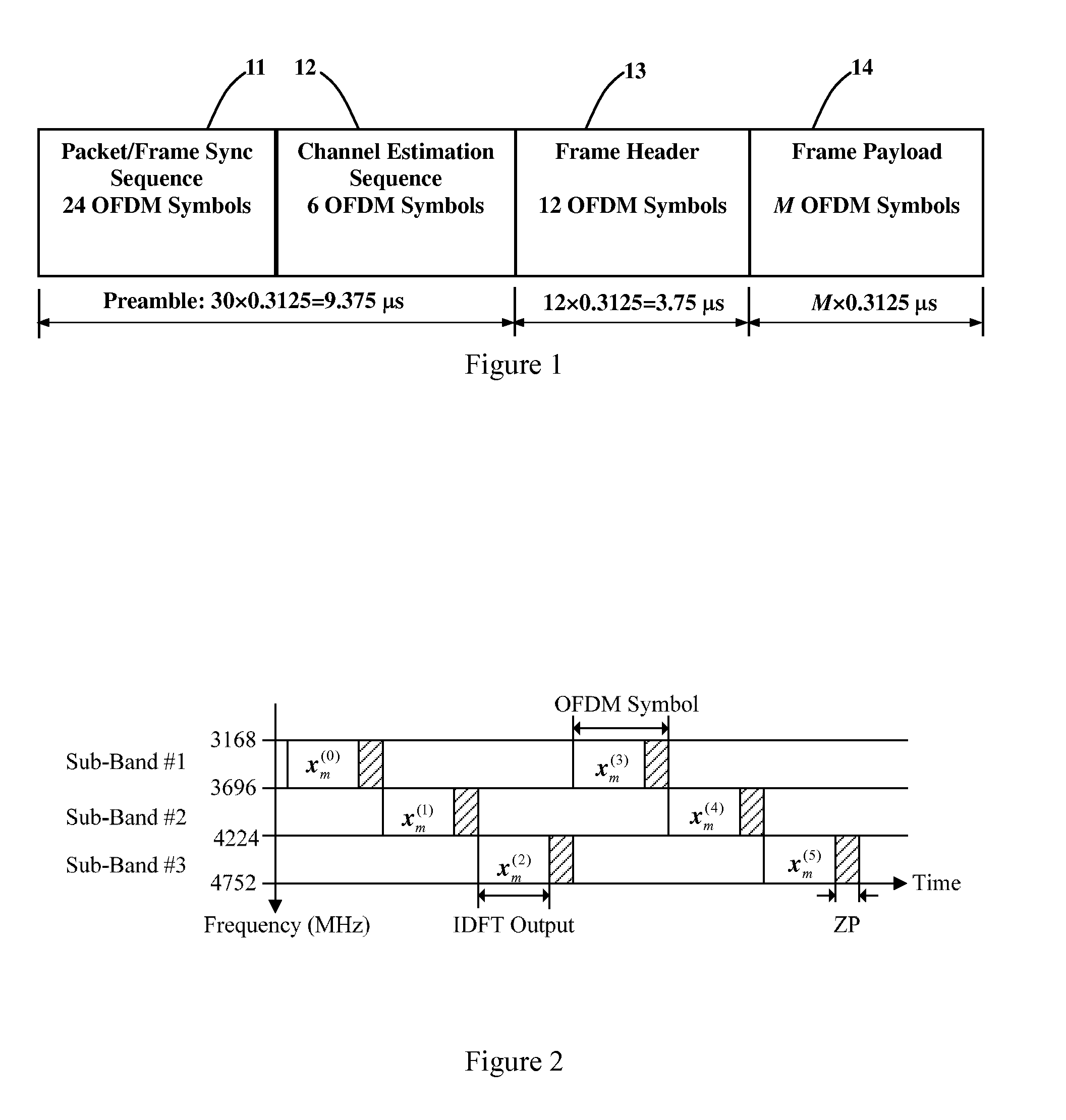

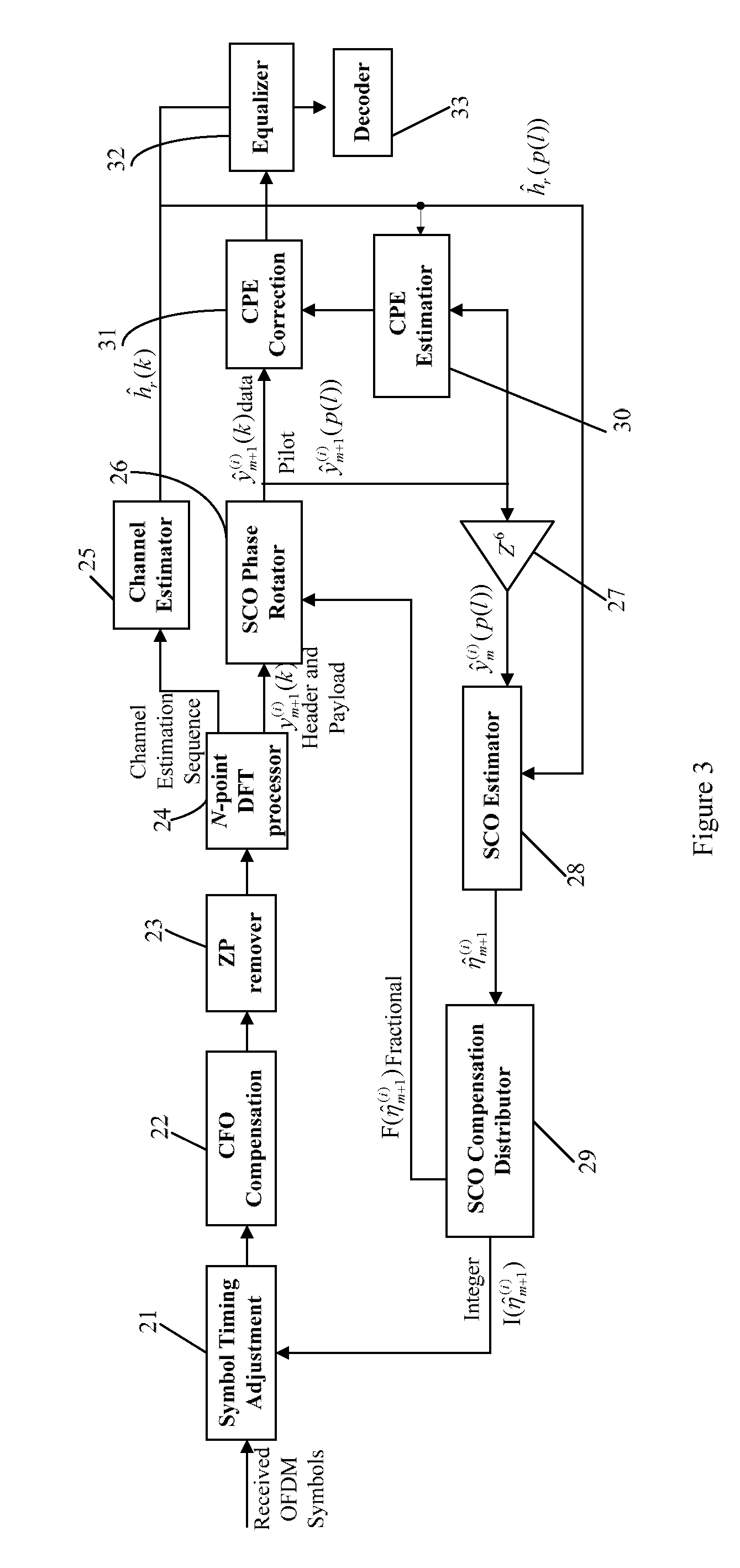

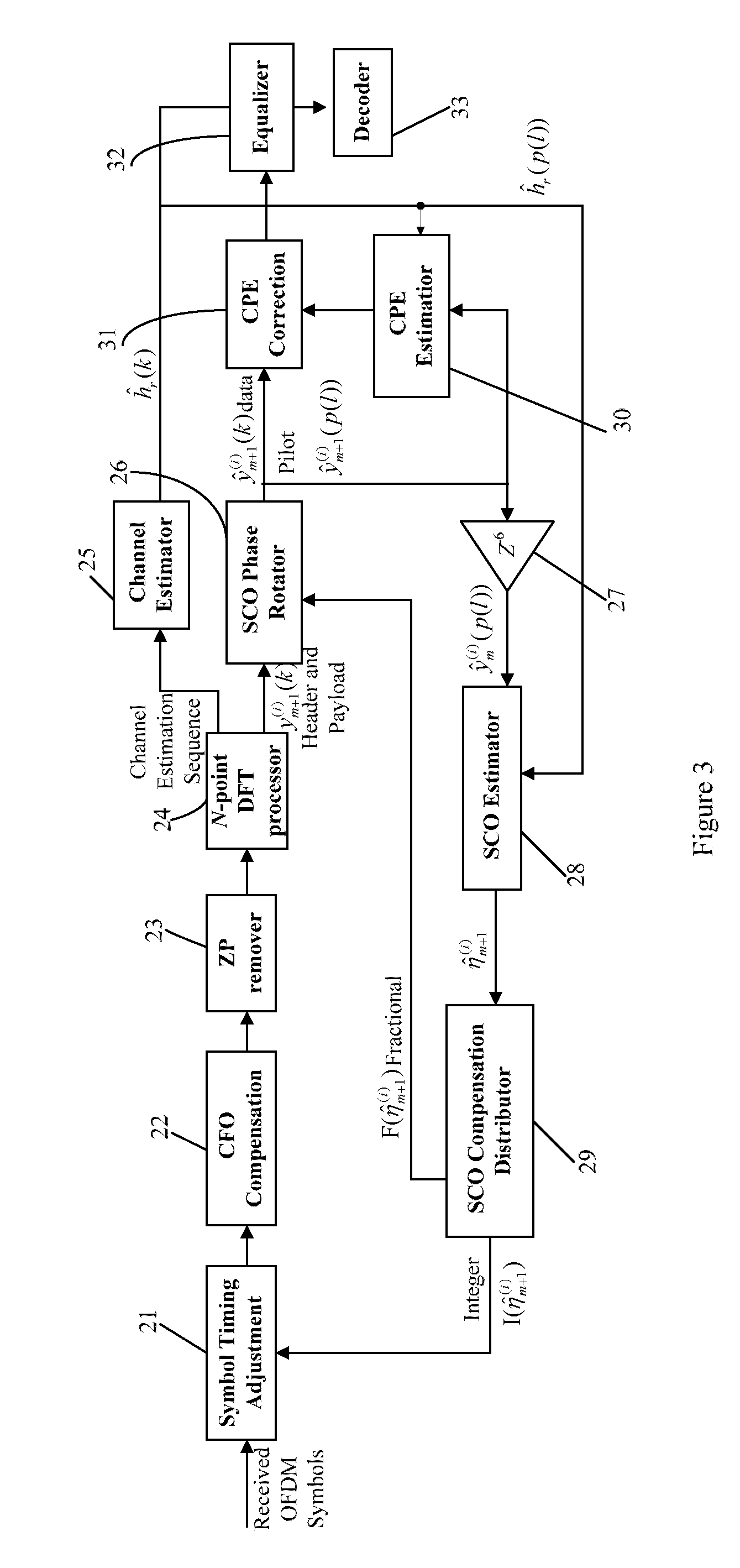

An apparatus for sampling clock recovery (SCO) and methods for estimating and compensating SCO are provided. The apparatus comprises a symbol timing adjustment module for shifting forward or backward symbol timing of the transmitted OFDM symbols; a discrete Fourier transform (DFT) processor for performing DFT to an output from the symbol timing adjustment module; a channel estimator for undertaking a channel frequency response estimation based on a channel estimation sequence; a SCO phase rotator for receiving and performing phase shift on the transmitted OFDM symbols of a frame header and a frame payload; an SCO estimation stage for undertaking an SCO estimation based on a pilot-subcarrier-related output of the SCO phase rotator and the CFR estimation; and an SCO compensation distributor for dividing the SCO estimation into integer and fractional portions and then distributing them into the symbol timing adjustment module and the SCO phase rotator, respectively.

Owner:WIPRO LTD

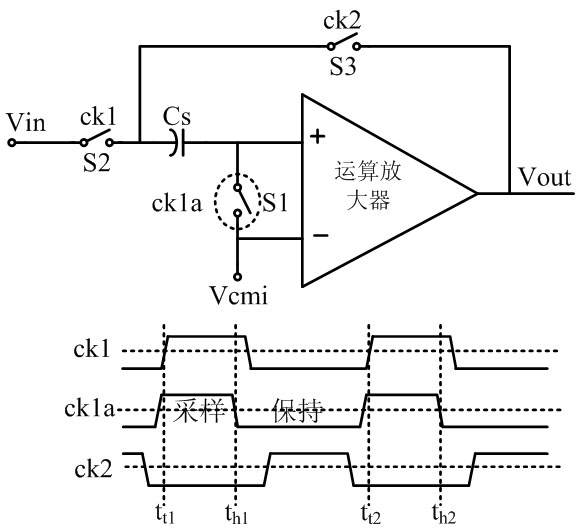

Metal oxide semiconductor (MOS) bootstrap switch circuit for calibrating sampling clock offset

ActiveCN102075171AClock Skew EliminationAdjust sampling timeElectronic switchingClock offsetControl signal

The invention belongs to the technical field of integrated circuits, and in particular relates to a metal oxide semiconductor (MOS) bootstrap switch circuit for calibrating sampling clock offset. The circuit is used for eliminating the sampling clock offset among channels of a time interleaving analog-digital converter. In the circuit, an MOSbootstrap switch is taken as a main body; a control signal is added to a bootstrap input end; and a control voltage signal is obtained by a clock offset detection module. A grid voltage bootstrapped circuit is used for bootstrapping a supply voltage for the control signal, so that the bootstrapped voltage follows with the control voltage signal. The bootstrapped voltage is added to the grid end of a switching tube so as to control the on and off of the switching tube. Thus, the control signal can adjust the on / off time of the switching tube, thereby effectively calibrating the clock offset and eliminating sampling mismatch among the channels.

Owner:FUDAN UNIV

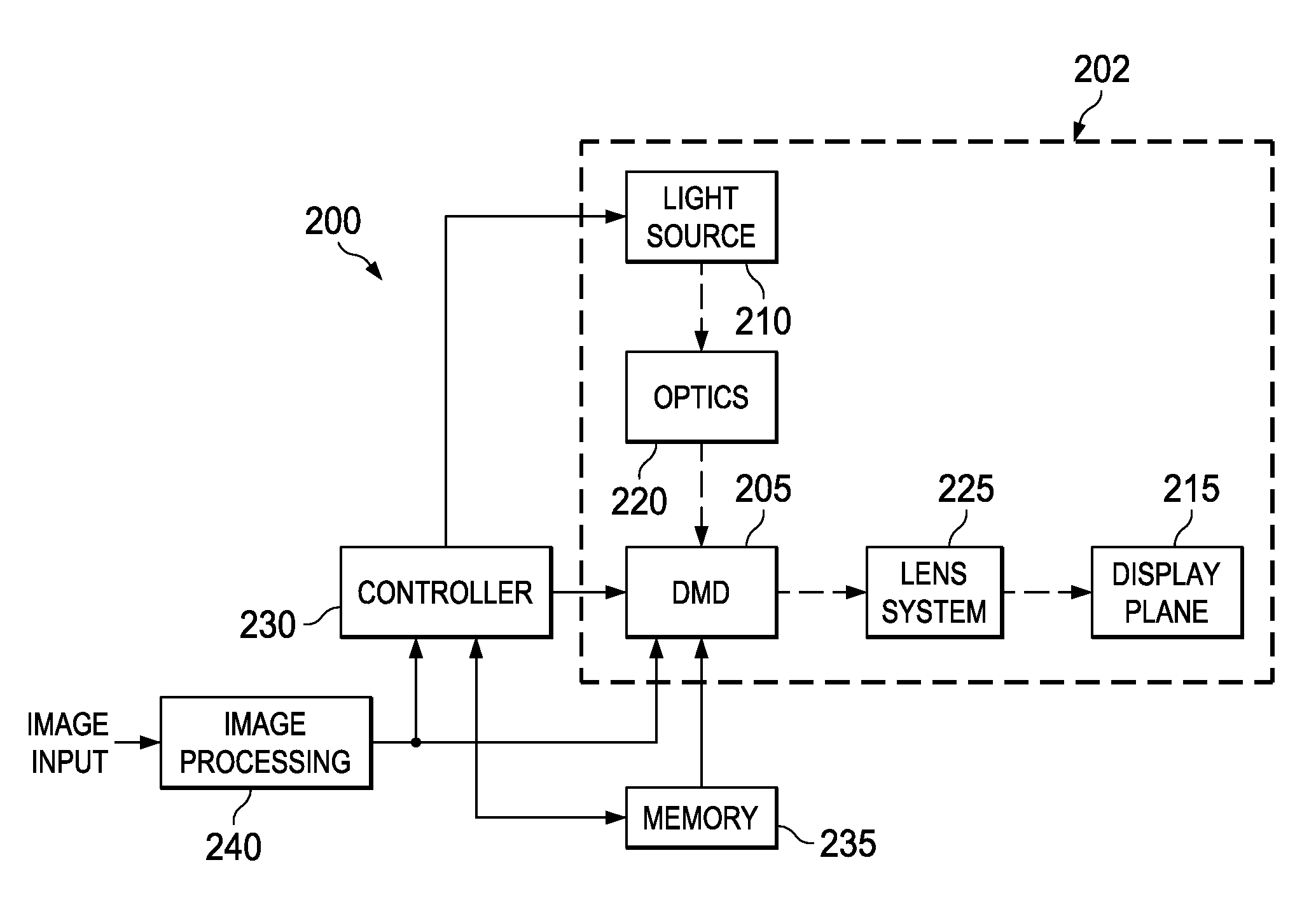

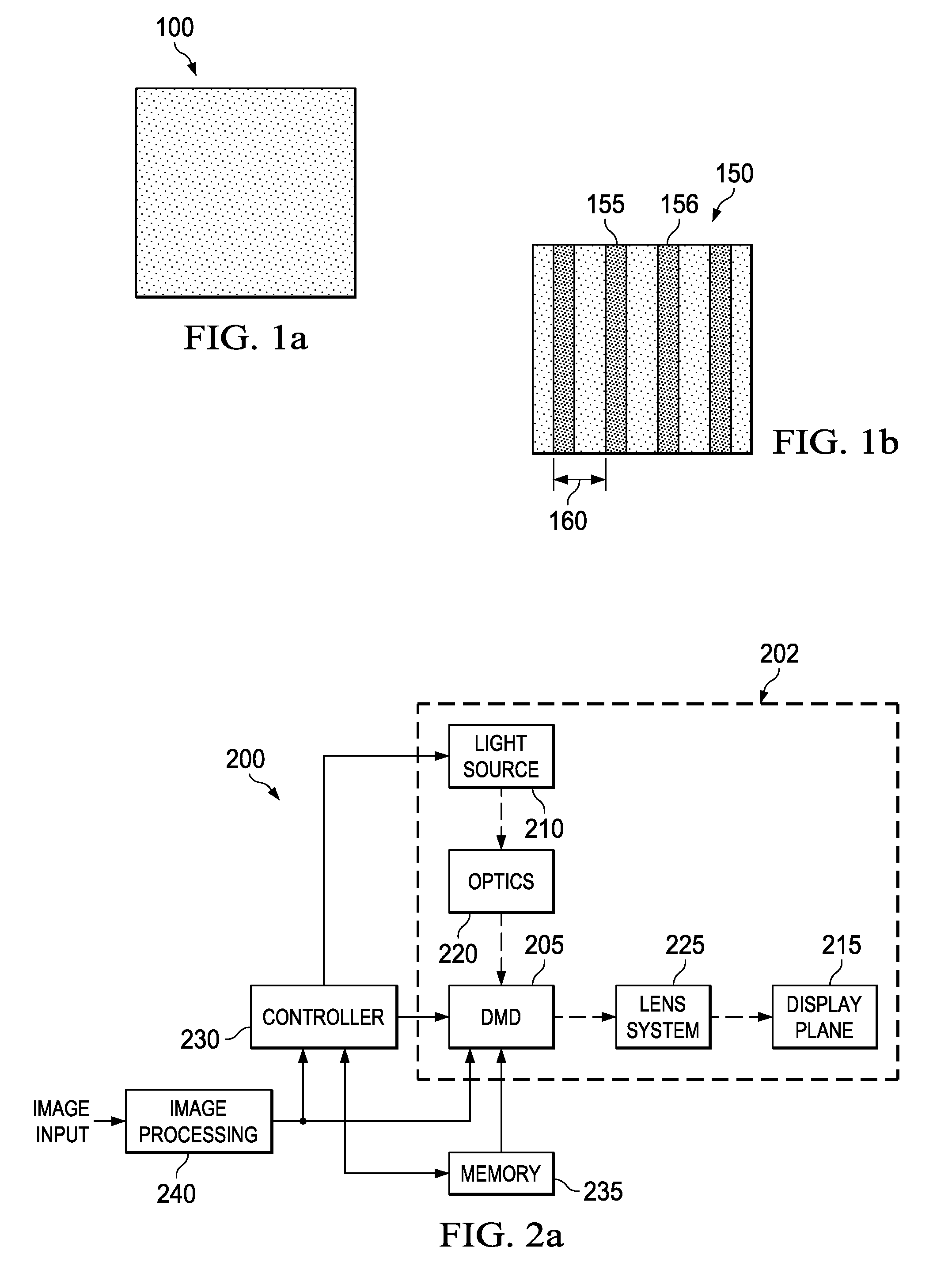

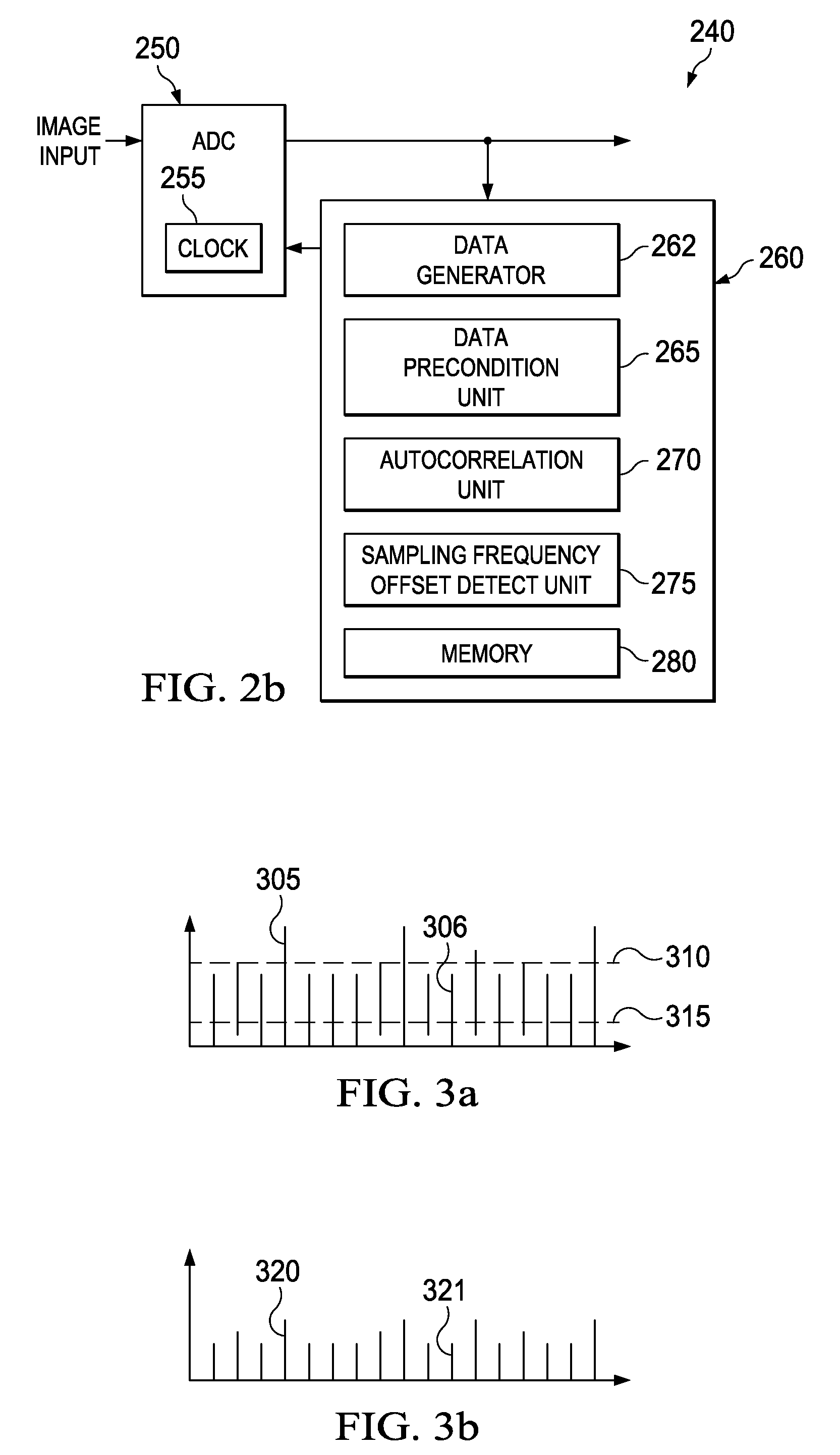

System and Method for Clock Offset Detection

ActiveUS20100007795A1Short timeReduce the amount requiredTelevision system detailsElectric signal transmission systemsSampling frequency offsetCorrelation function

A system and method for detecting a sampling clock offset of an analog-to-digital converter used to digitize an analog image signal. A method comprises buffering samples of an analog image signal, computing a value of an autocorrelation function using the buffered samples and a delayed version of the buffered samples, and repeating the computing a value for delays in a range of delays. The method also comprises computing a sampling frequency offset from the values of the autocorrelation function and changing a sampling frequency using the sampling frequency offset.

Owner:TEXAS INSTR INC

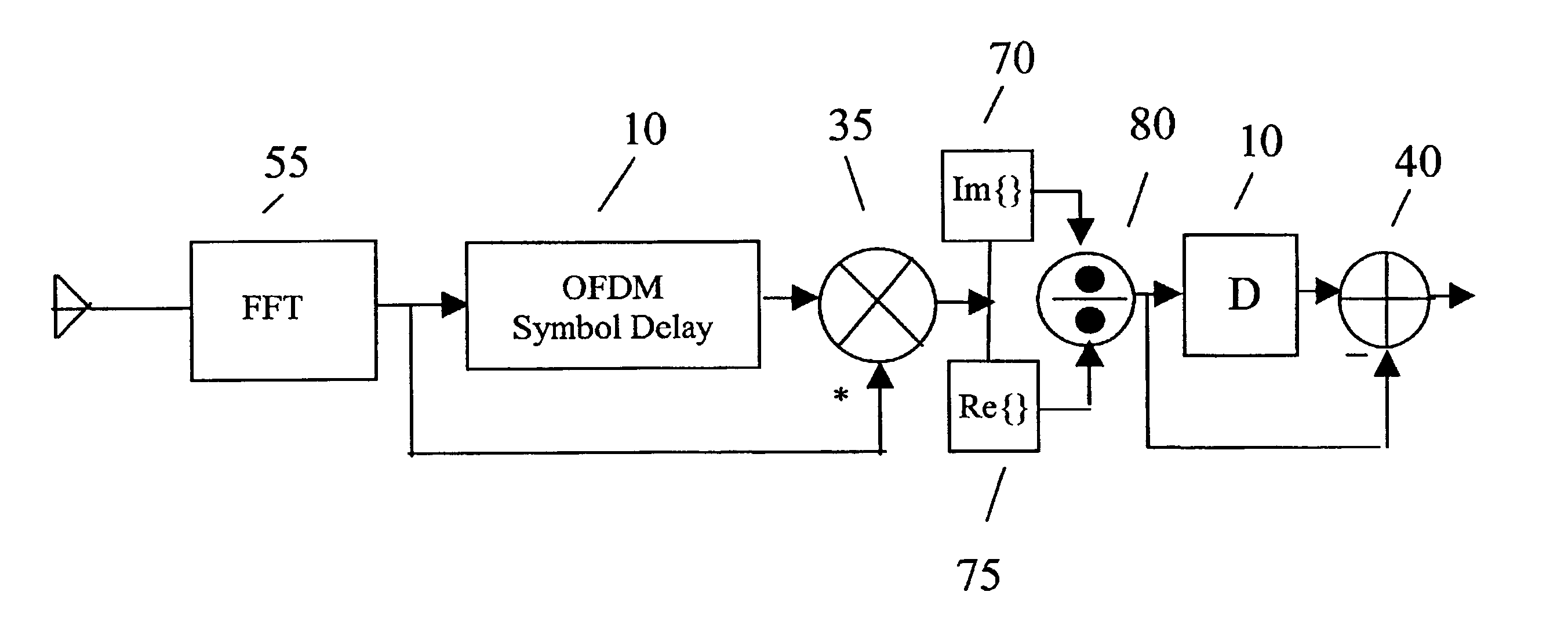

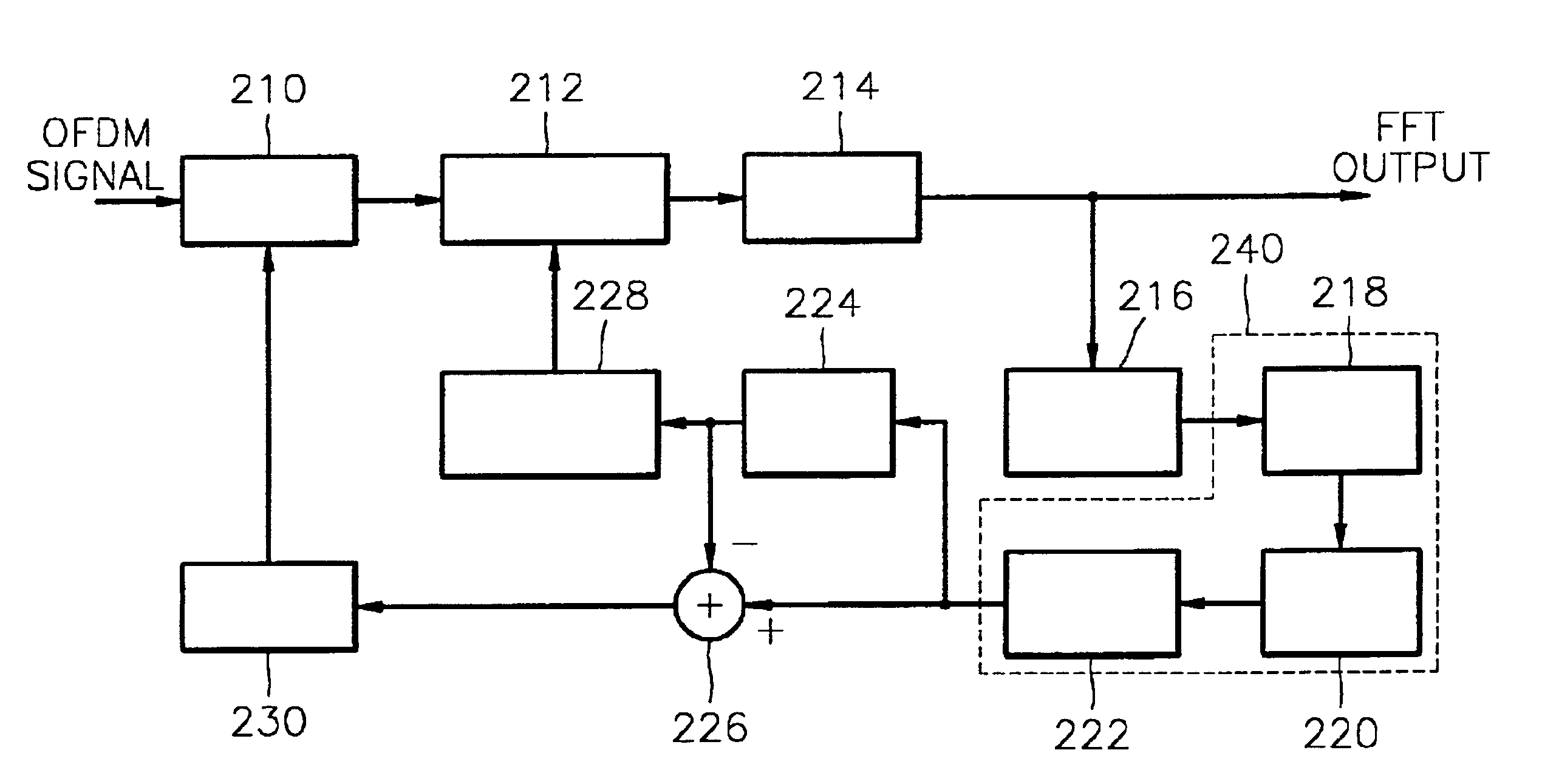

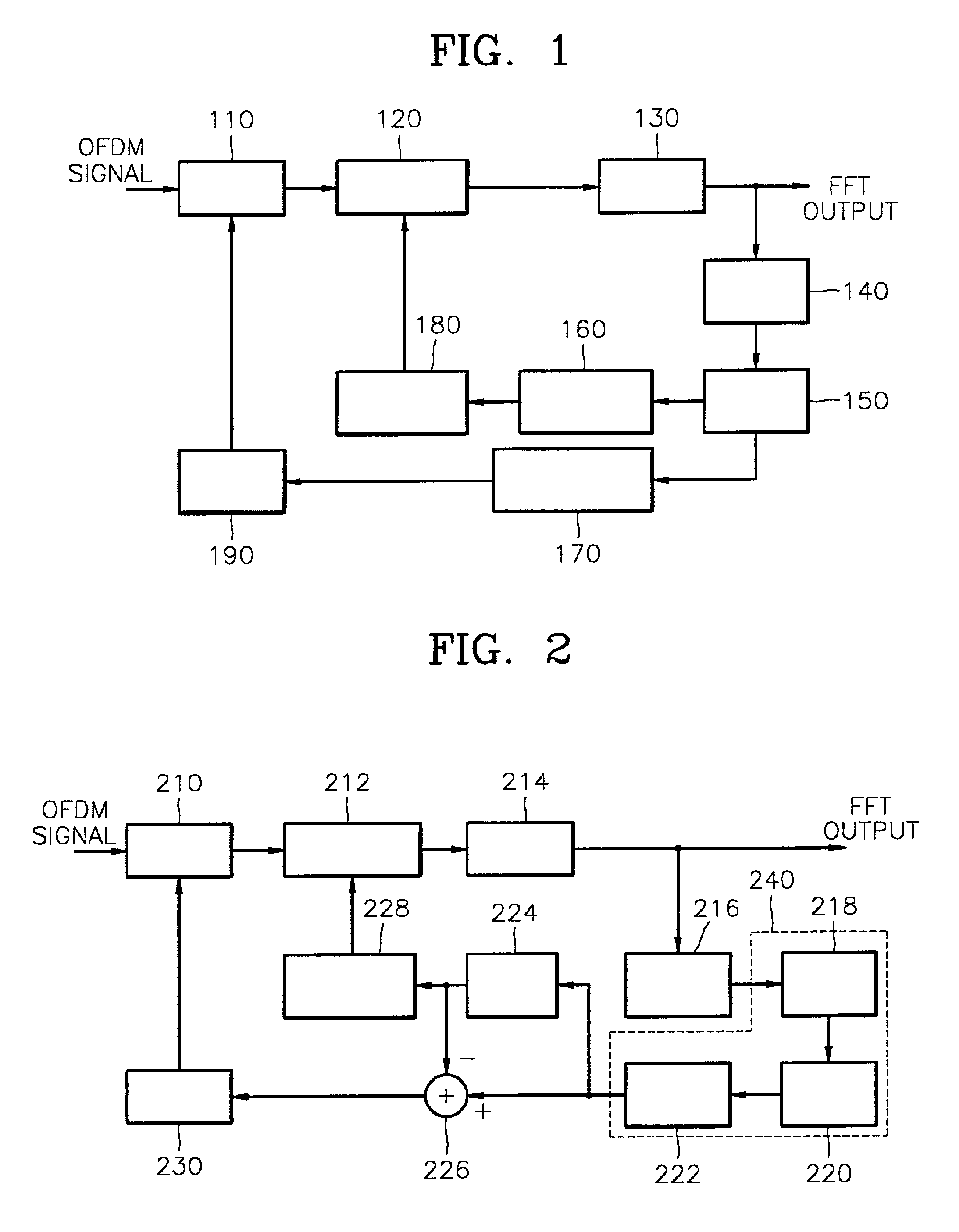

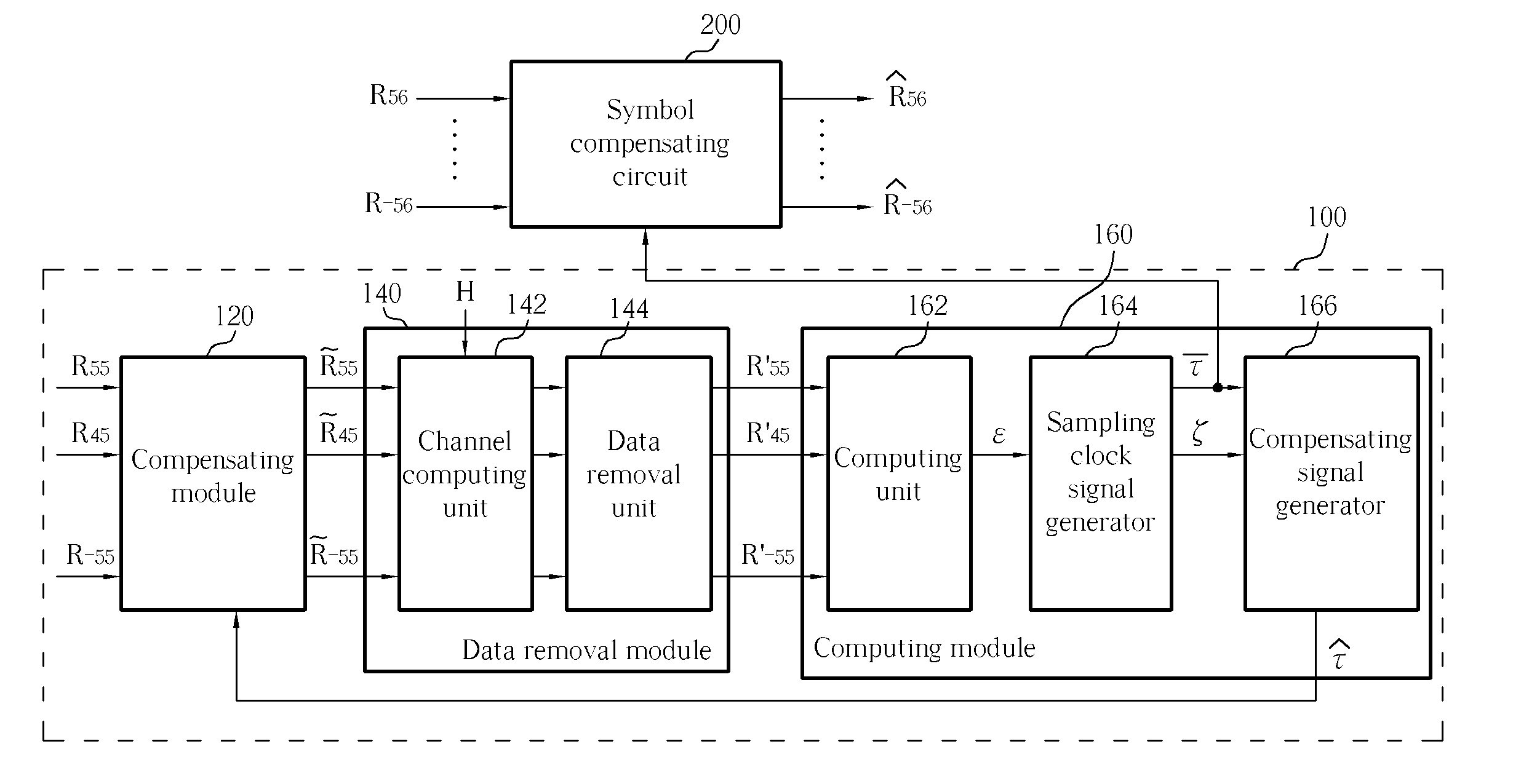

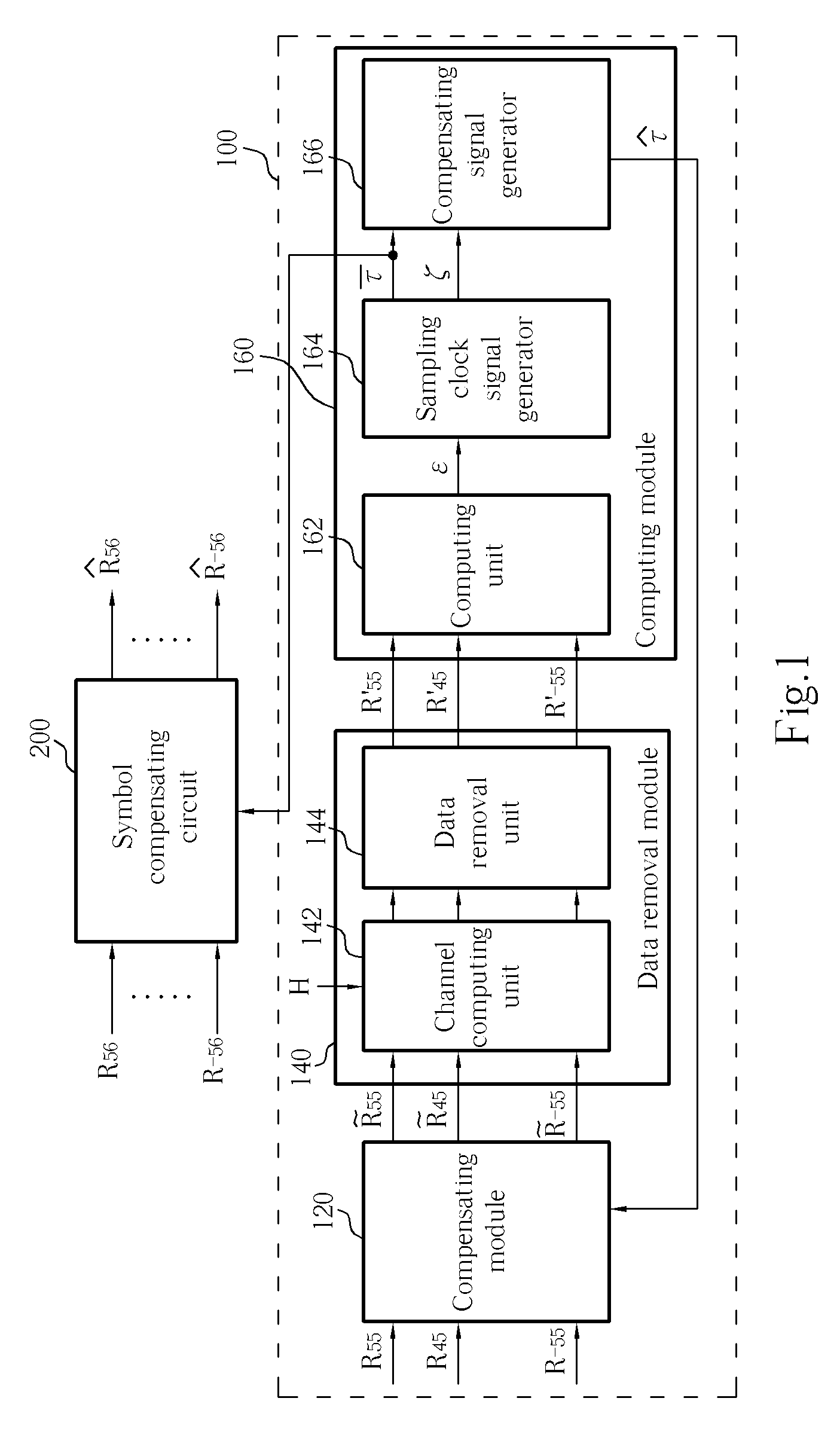

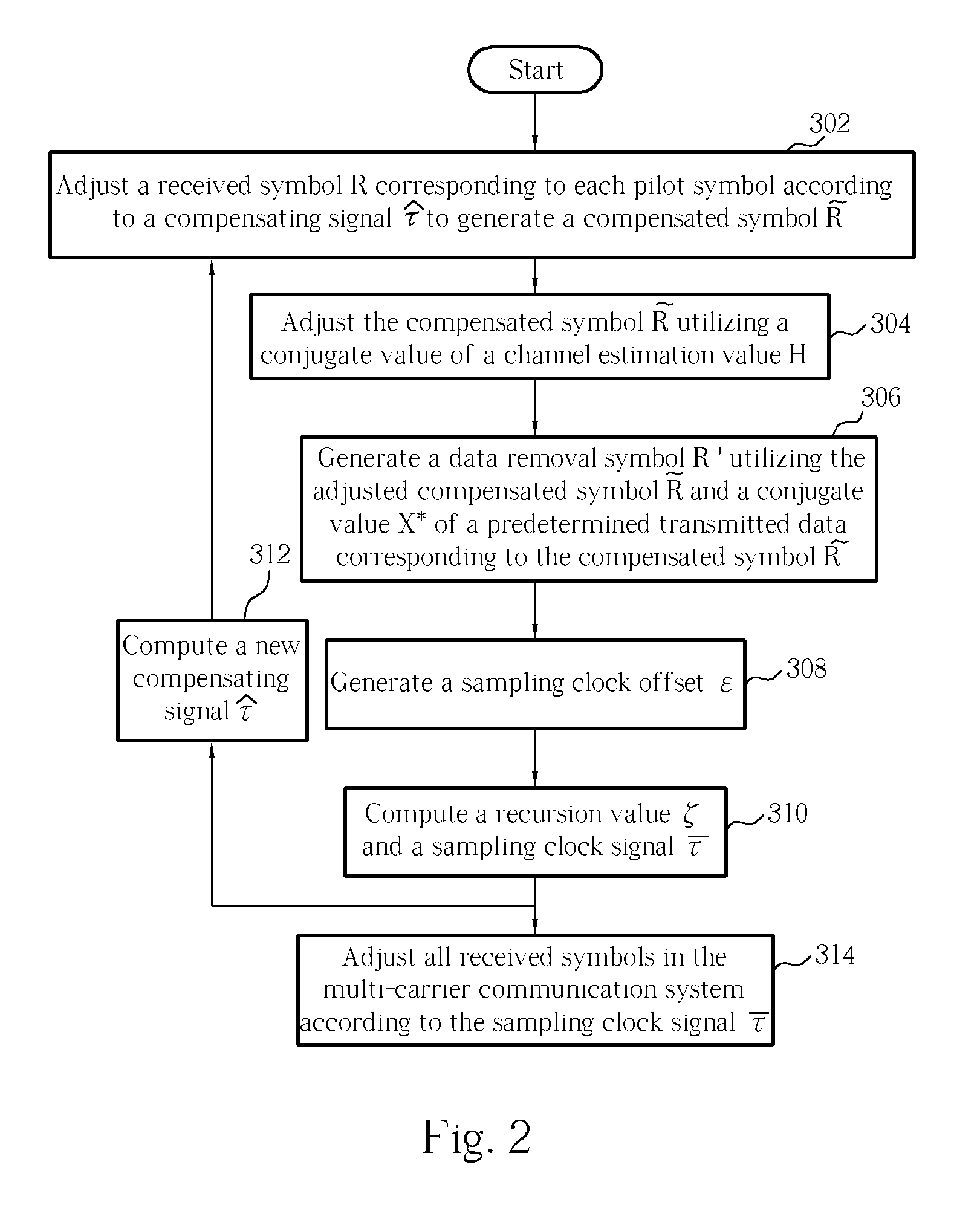

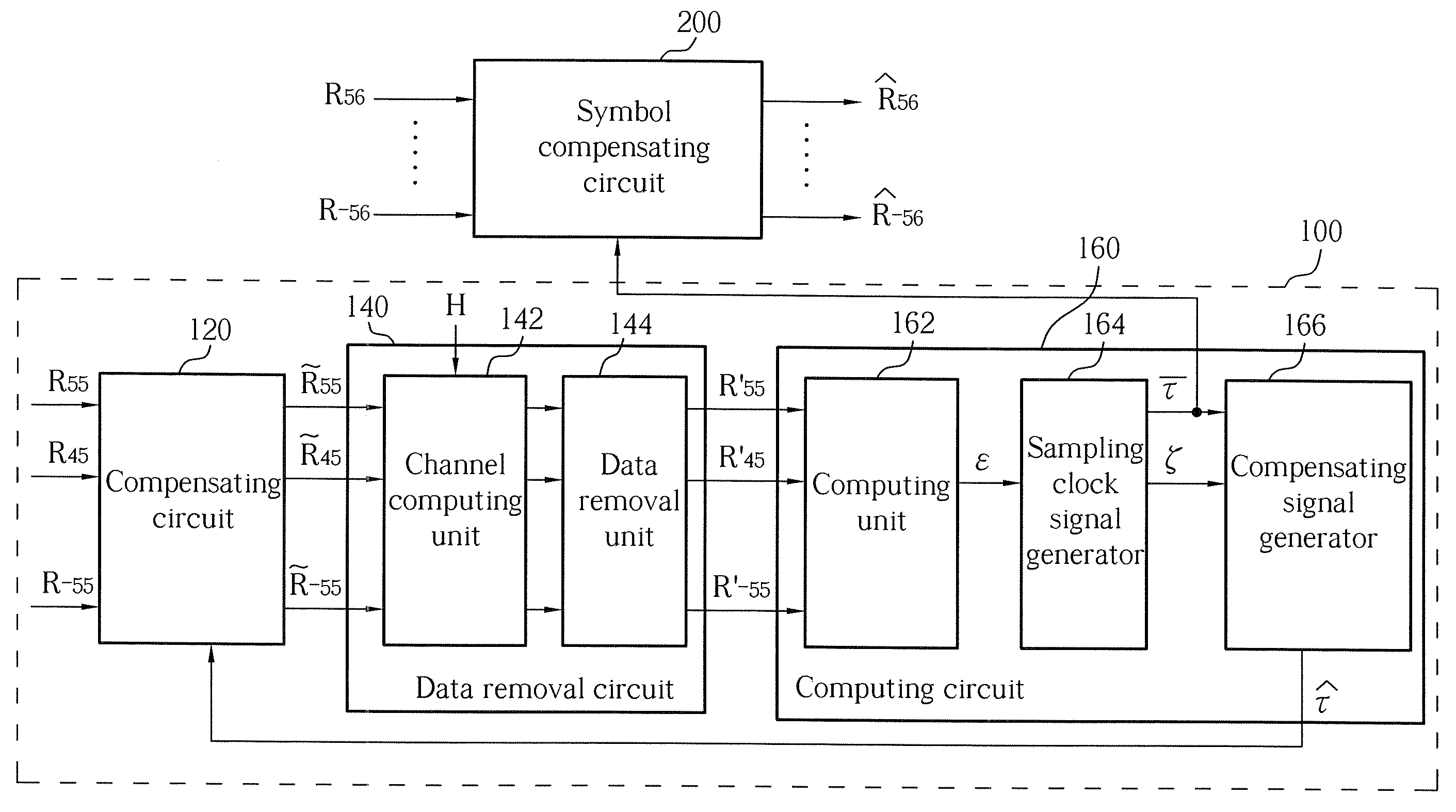

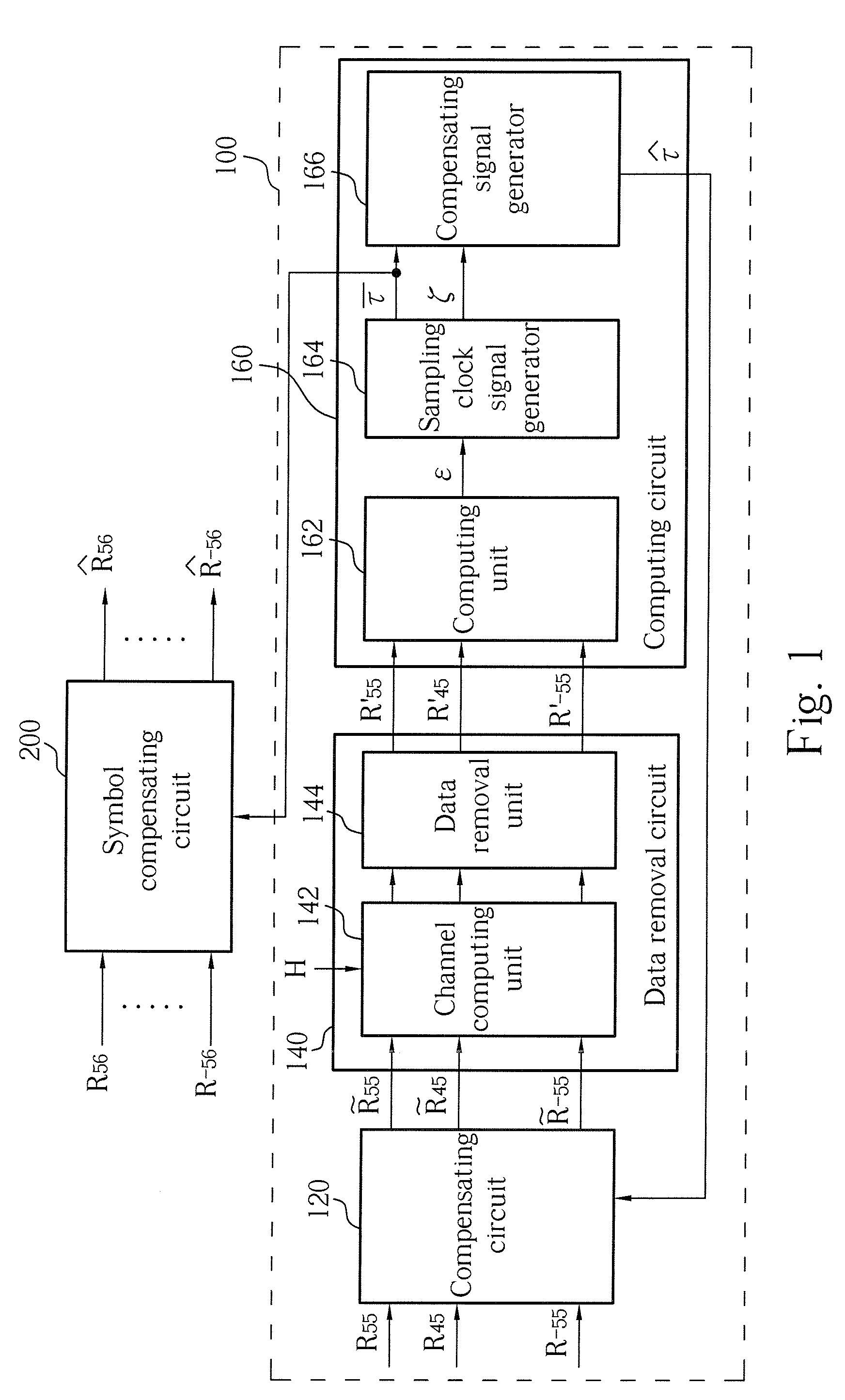

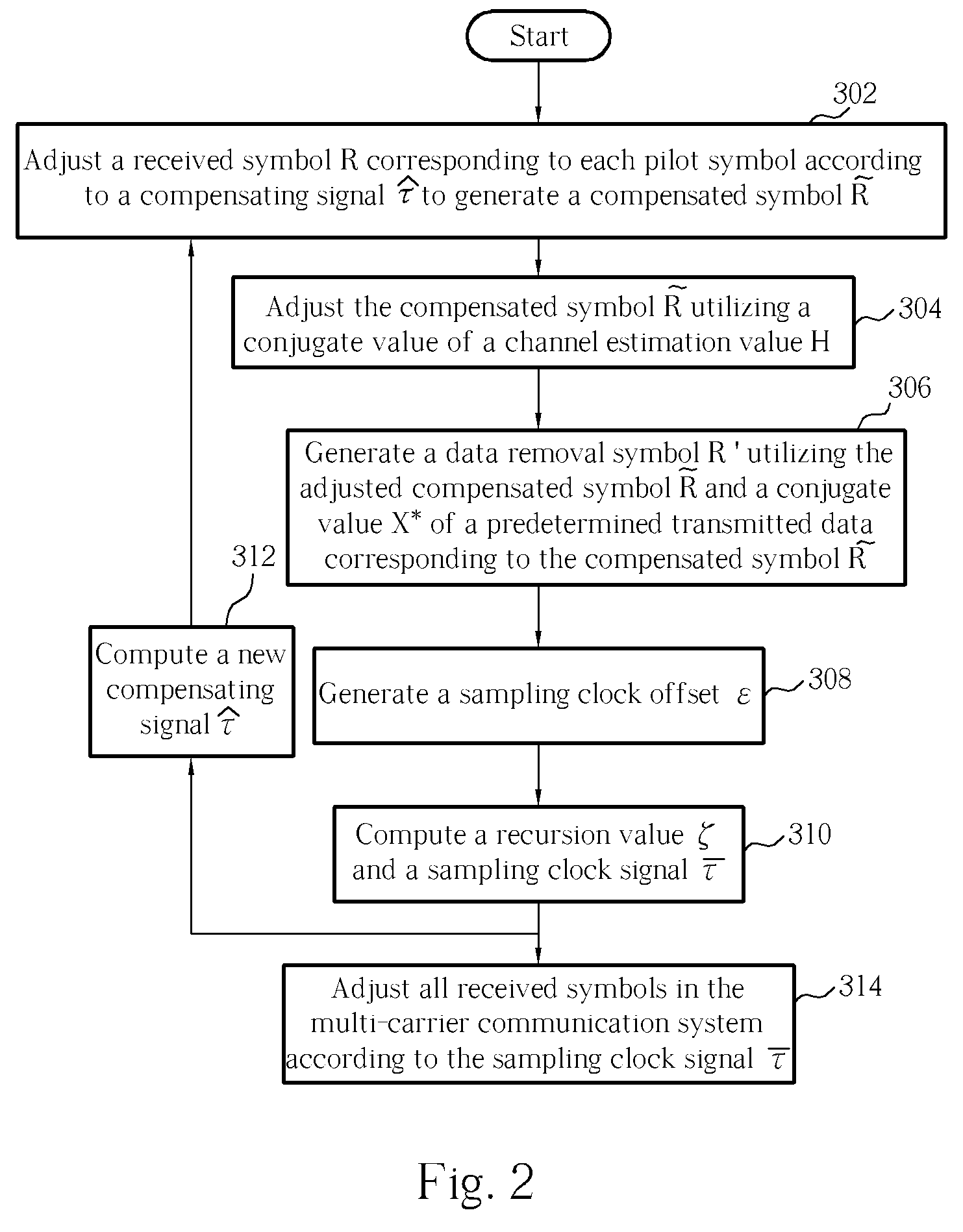

Apparatus and method for tracking sampling clock in multi-carrier communication system

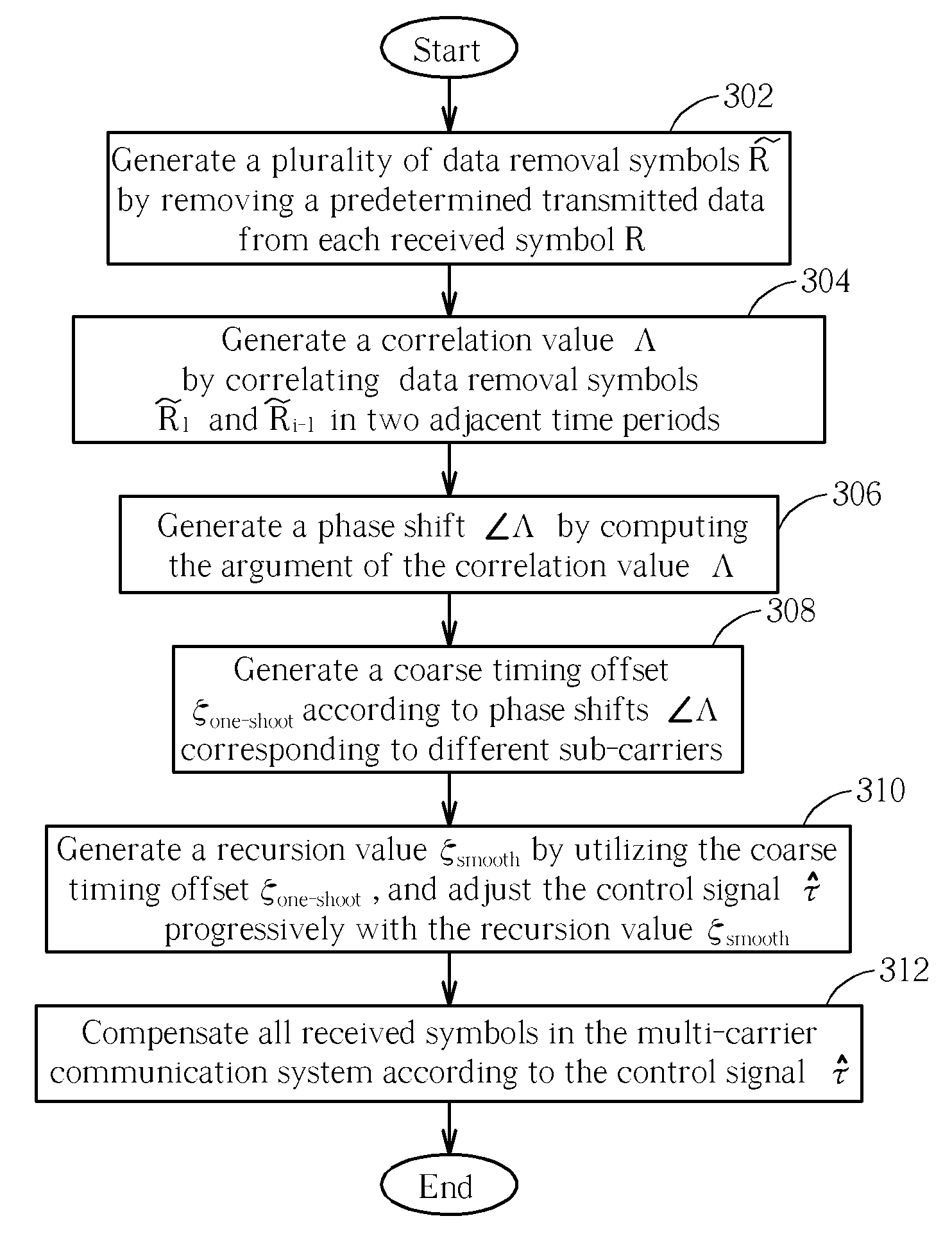

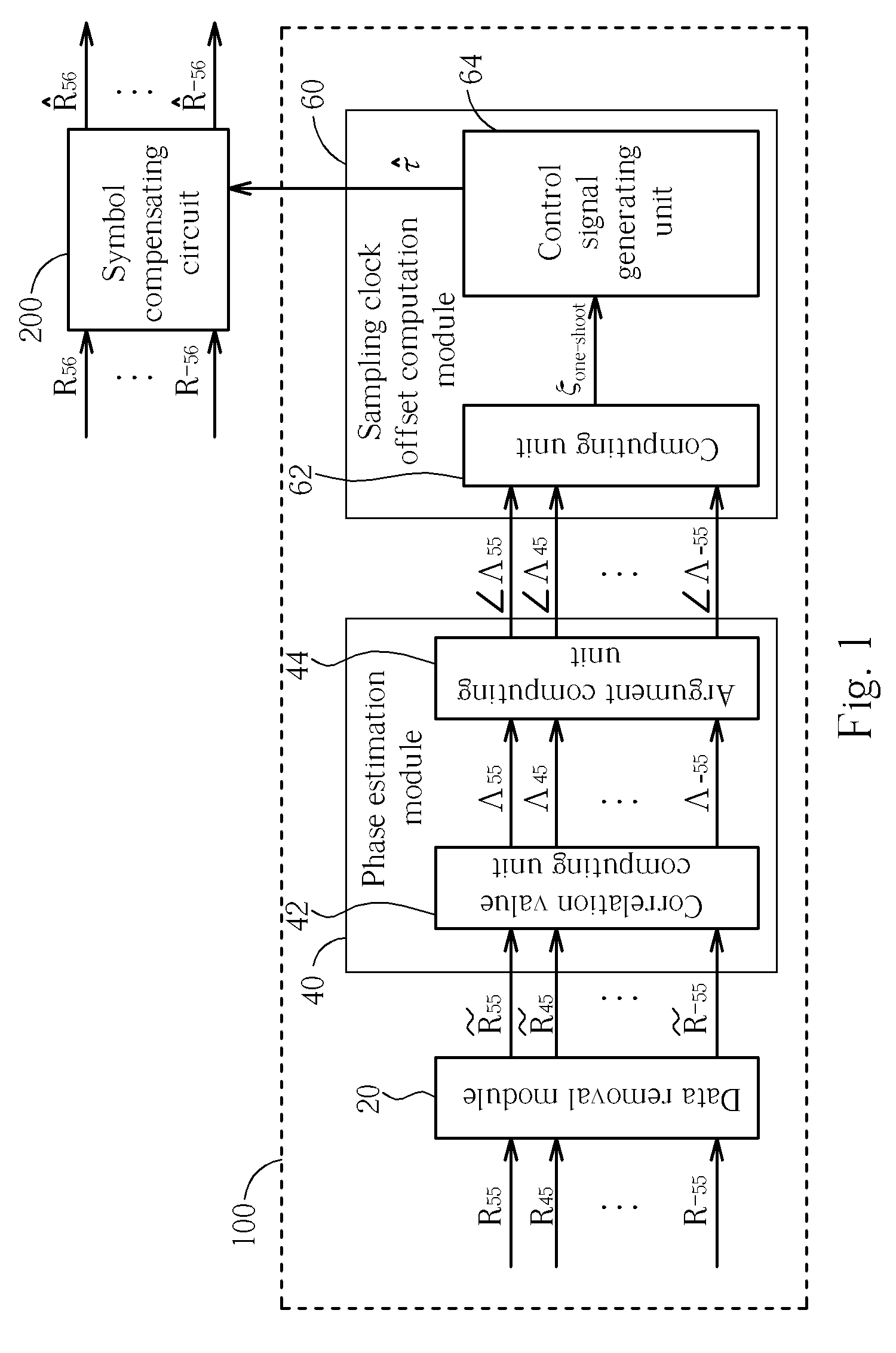

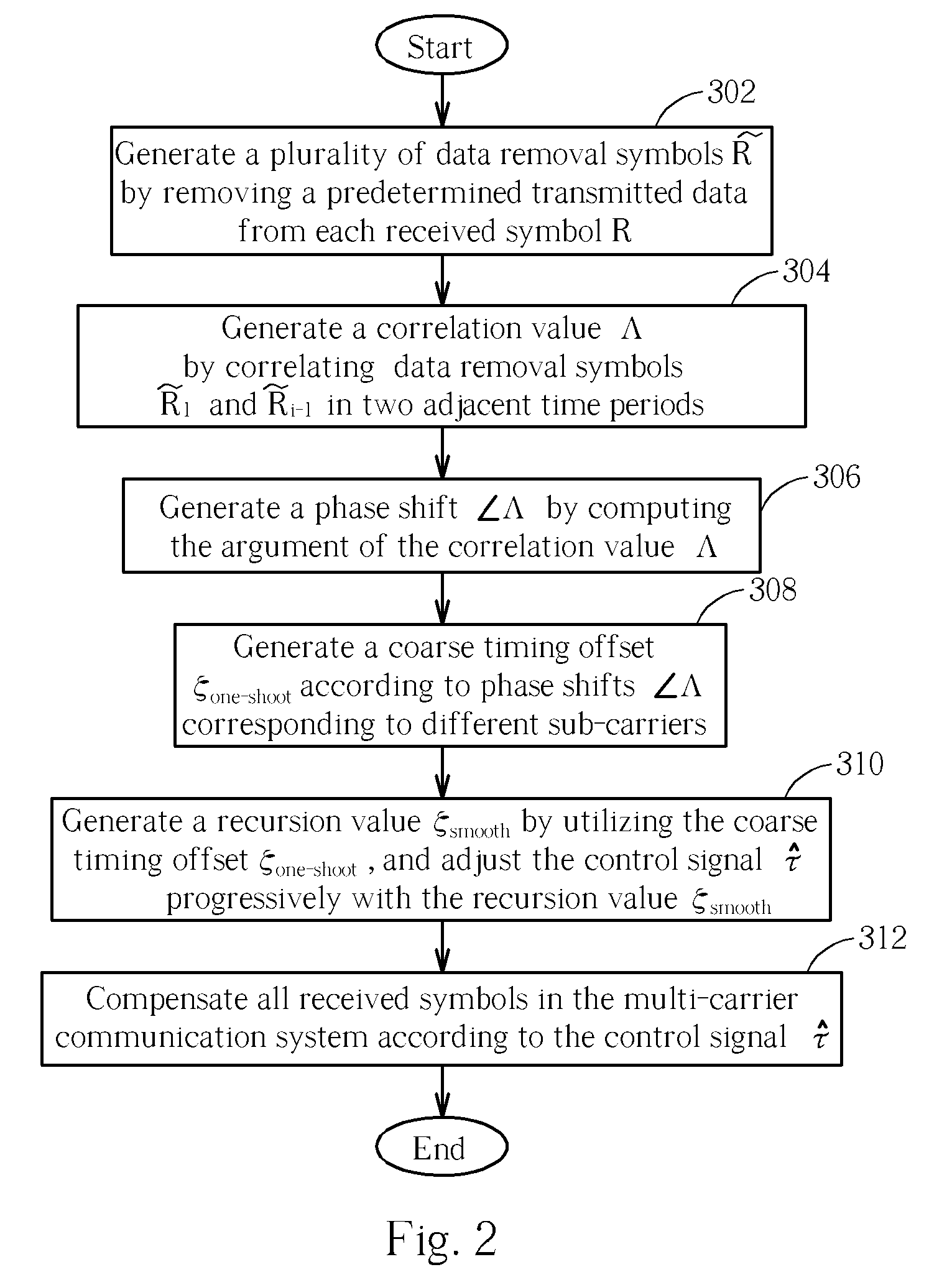

ActiveUS20060215776A1Reduce receiver complexityReduce computing loadAmplitude-modulated carrier systemsSecret communicationCommunications systemComputer science

An apparatus and method for tracking a sampling clock are disclosed. The apparatus includes a compensating unit compensating phases of a first and a second received symbols according to a compensating signal and thereby generating a first and a second compensated symbols; a data removal module removing a first predetermined transmitted data from the first compensated symbol, and a second predetermined transmitted data from the second compensated symbol and thereby generating a first and a second data removal symbols; and a computing module generating a sampling clock offset according to the first and the second data removal symbols, and adjusting the sampling clock signal according to the sampling clock offset.

Owner:REALTEK SEMICON CORP

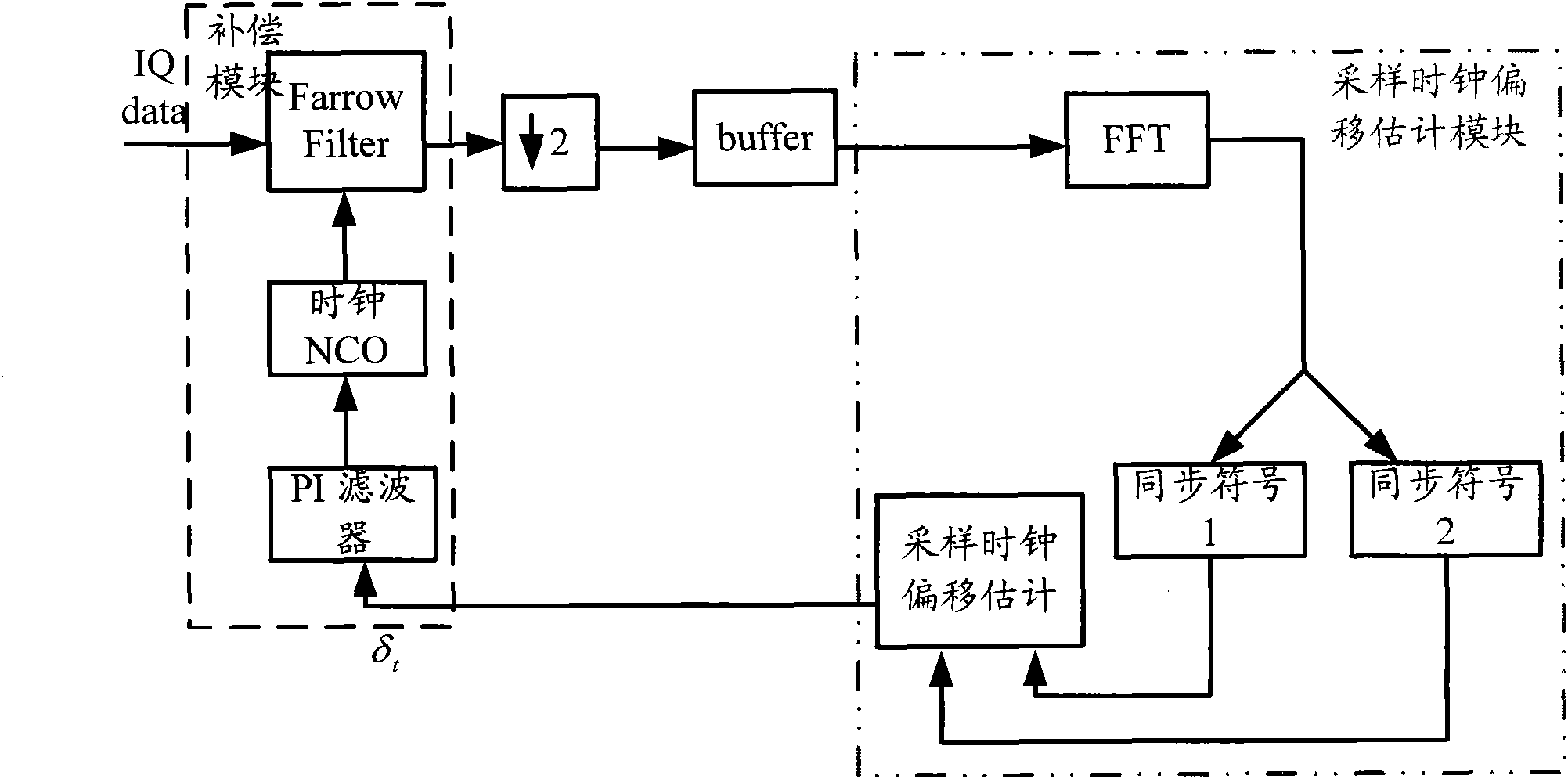

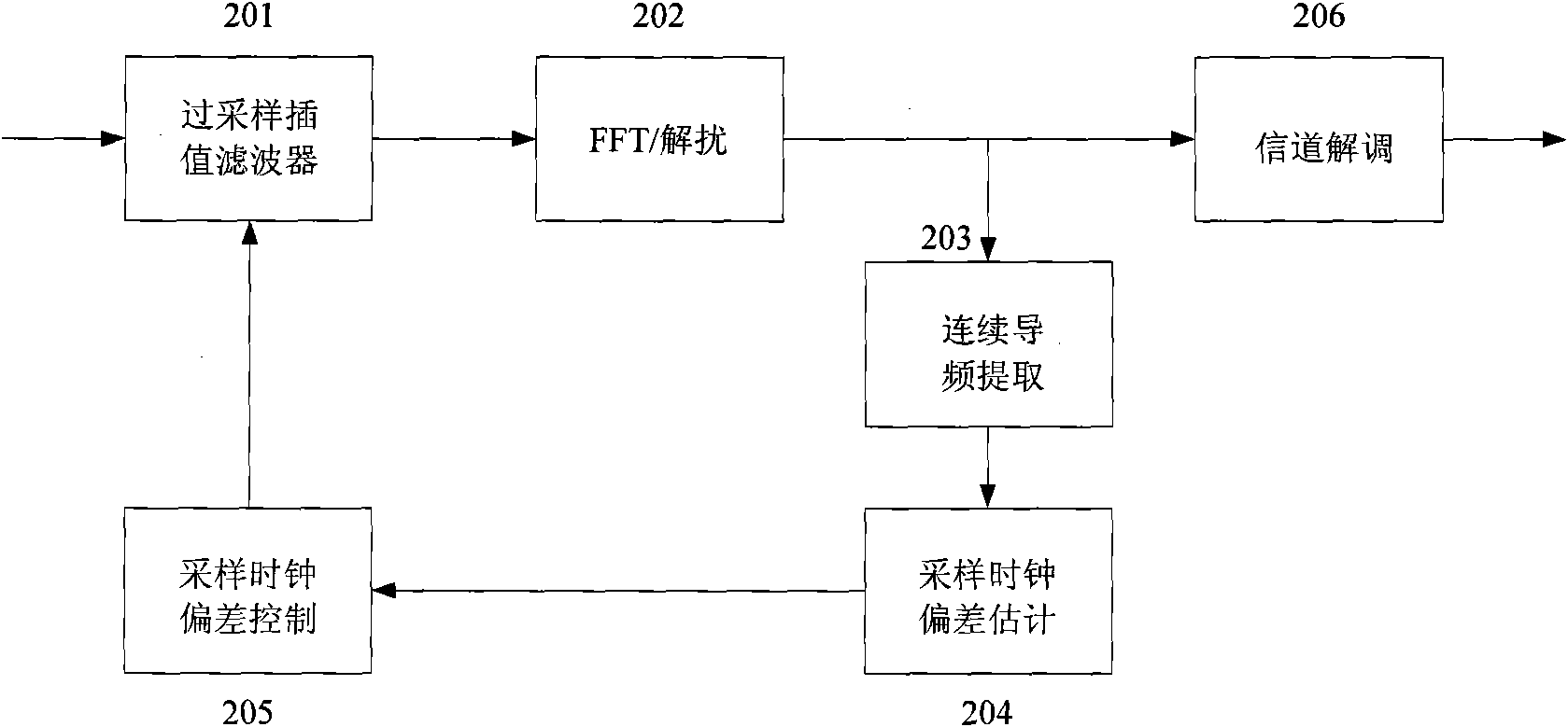

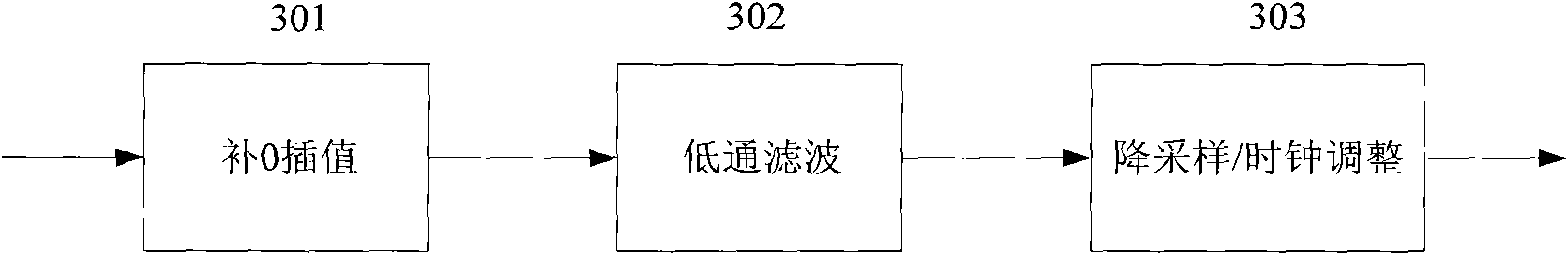

Device and method for estimating and compensating sampling clock offset of handset television terminal

InactiveCN101562597AReduce phase rotationAvoid complexityMulti-frequency code systemsCarrier signalComputer science

The invention provides a device for estimating and compensating sampling clock offset of a handset television terminal, comprising the following modules of an over-sampling interpolation filter module, an FFT / descrambling module, a continuous pilot extraction module, a sampling clock offset estimation module and a sampling clock offset control module, wherein the over-sampling interpolation filter module completes the over-sampling interpolation, filtering and desampling extraction of the input data and adjusts the sampling clock offset according to the final sampling clock offset estimation result; the FFT / descrambling module carries out FFT operation and descrambling treatment; the continuous pilot extraction module extracts continuous pilot sub-carrier data from the descrambled data; the sampling block offset estimation module completes the estimation of the sampling clock offset; and the sampling clock offset control module obtains the final sampling clock offset estimation result according to the provided estimation results and supplies the results to the over-sampling interpolation filter module. Simultaneously, the invention provides a method for estimating and compensating sampling clock offset of a handset television terminal. The device and the method can simplify the treatment and ensure receiving performance.

Owner:ZTE CORP

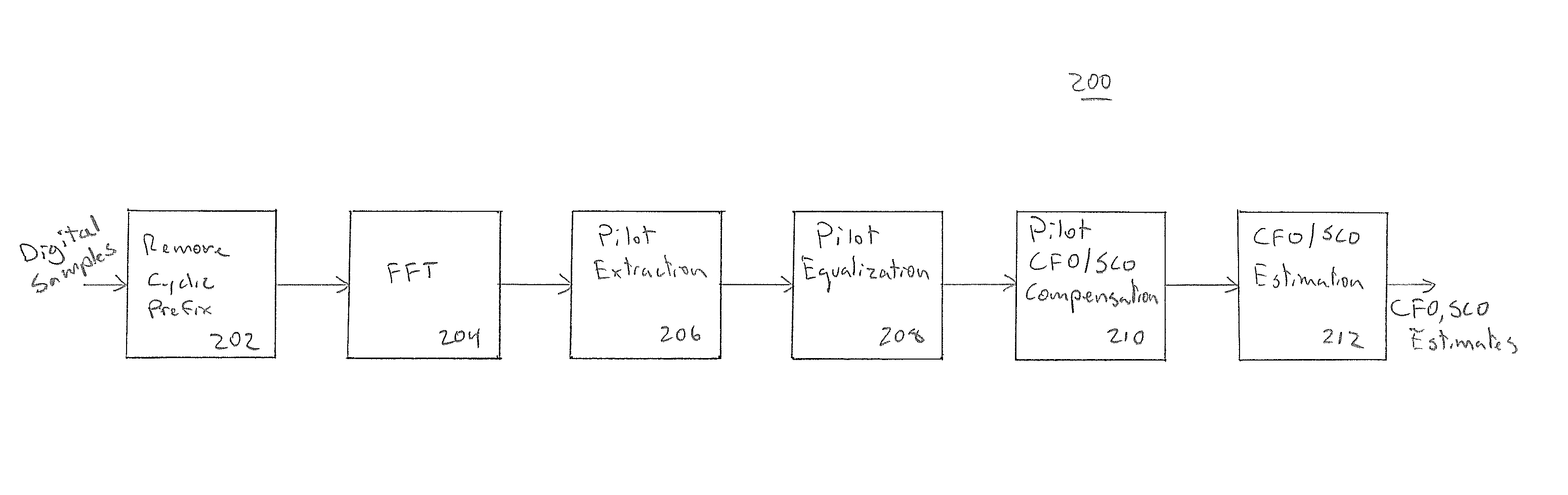

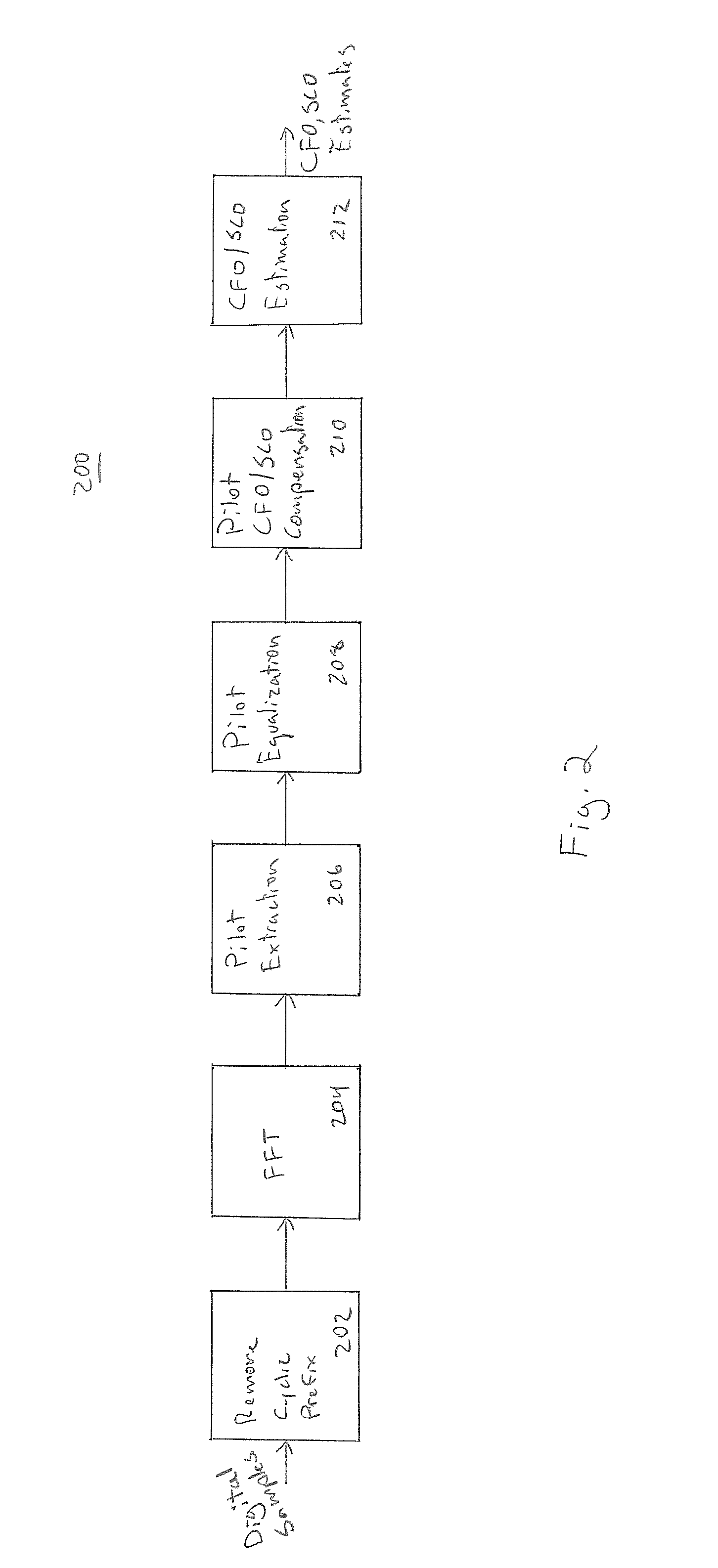

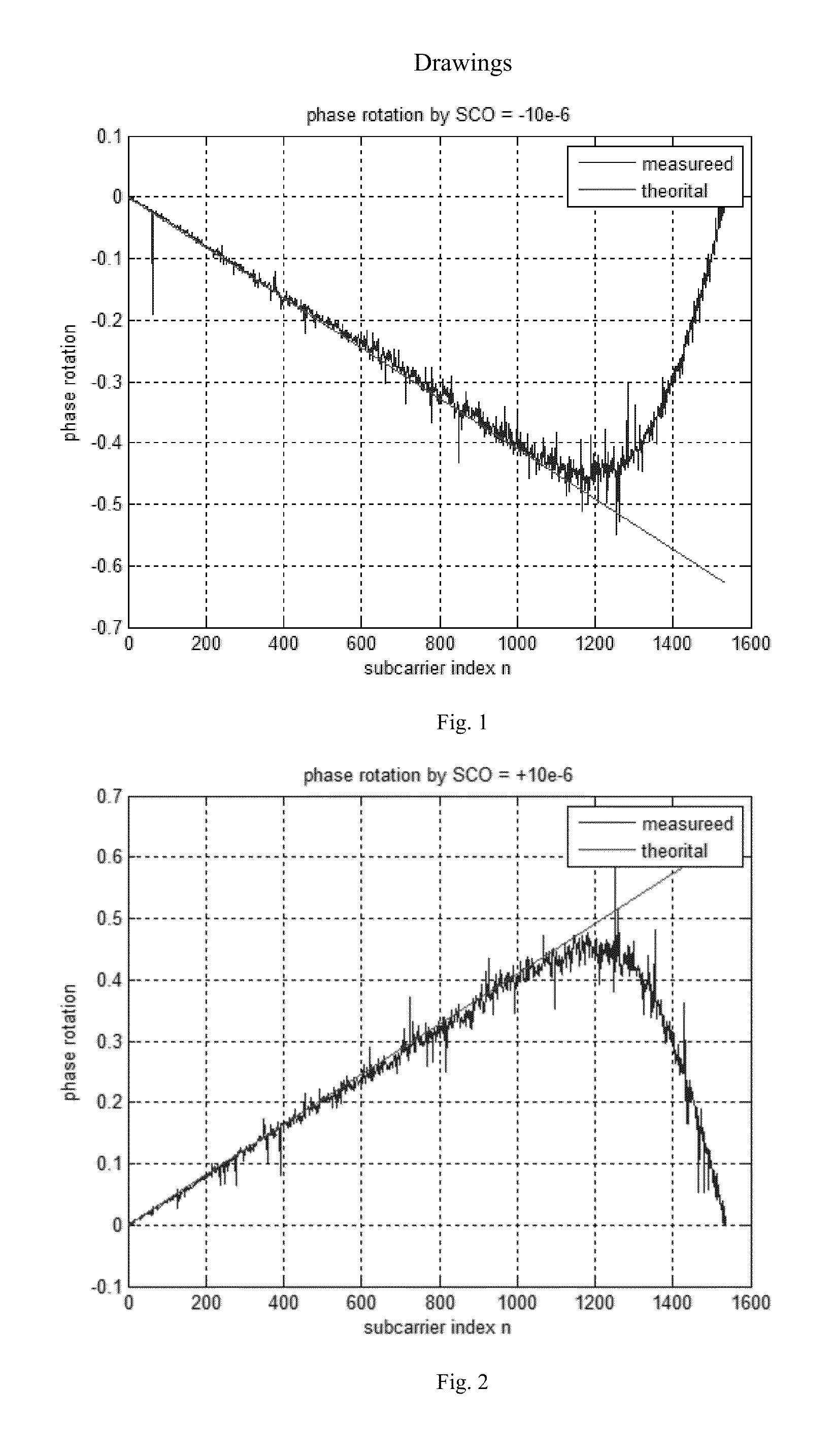

Estimation and compensation for carrier frequency offset and sampling clock offset in a communication system

ActiveUS8804804B1Multiple-port networksSynchronisation error correctionCommunications systemPhase difference

A system for estimating clock frequency offset and sampling clock offset in a communication system is provided. A receiver is configured to receive a communication signal having been transmitted from a transmitter via a communication channel. The receiver has a signal processor, wherein the signal processor is configured to generate an estimate of a carrier frequency offset and an estimate of a sampling clock offset from the received communication signal by: extracting a vector of pilot symbols from the received signal; performing equalization on the pilot symbols; performing clock frequency offset and sampling clock offset compensation on the pilot symbols; generating the estimate of a carrier frequency offset by estimating a common phase rotation using a first Taylor series approximation; and generating the estimate of the sampling clock offset by estimating phase differences between pairs of pilot symbols using a second Taylor series approximation.

Owner:U-BLOX

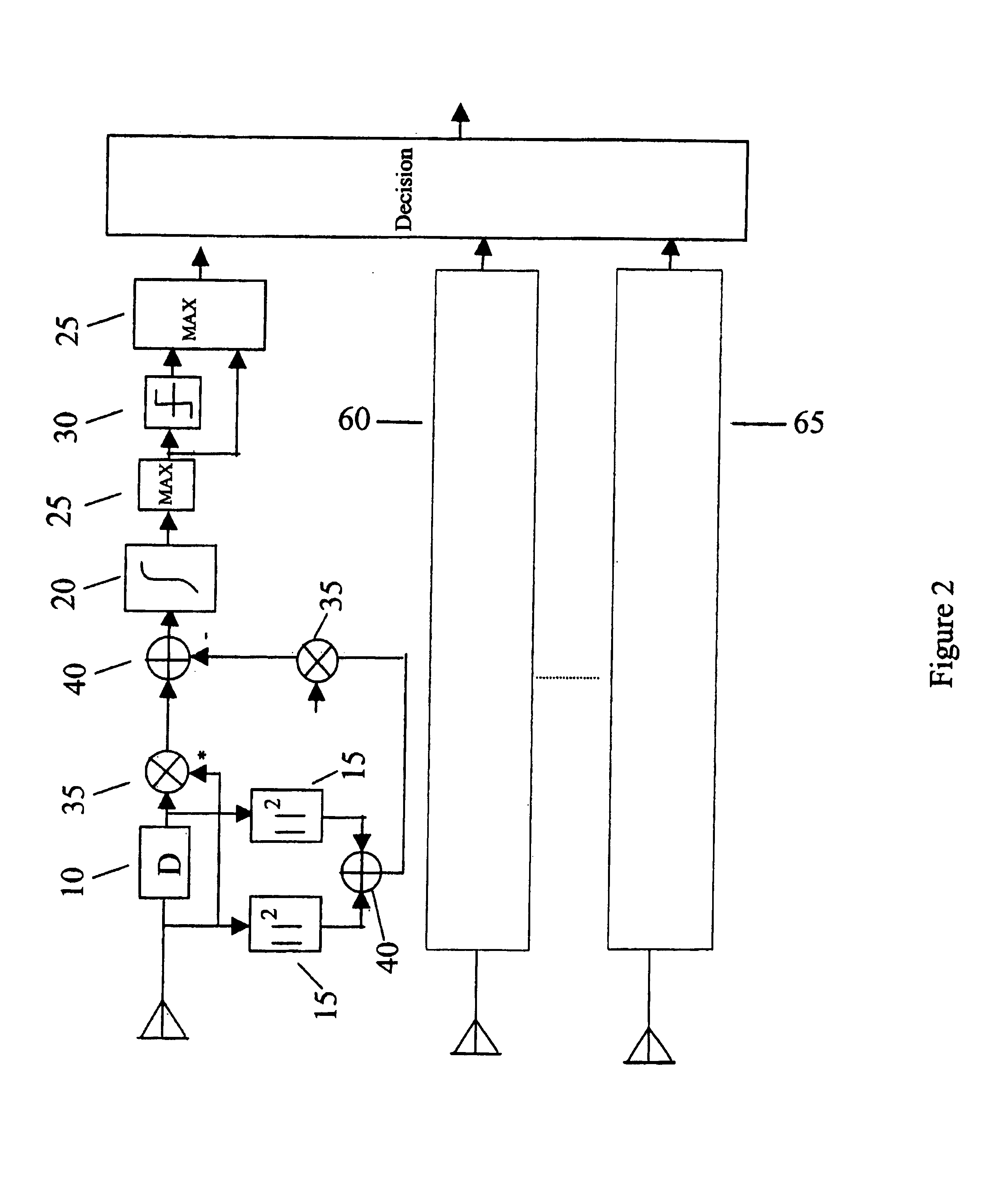

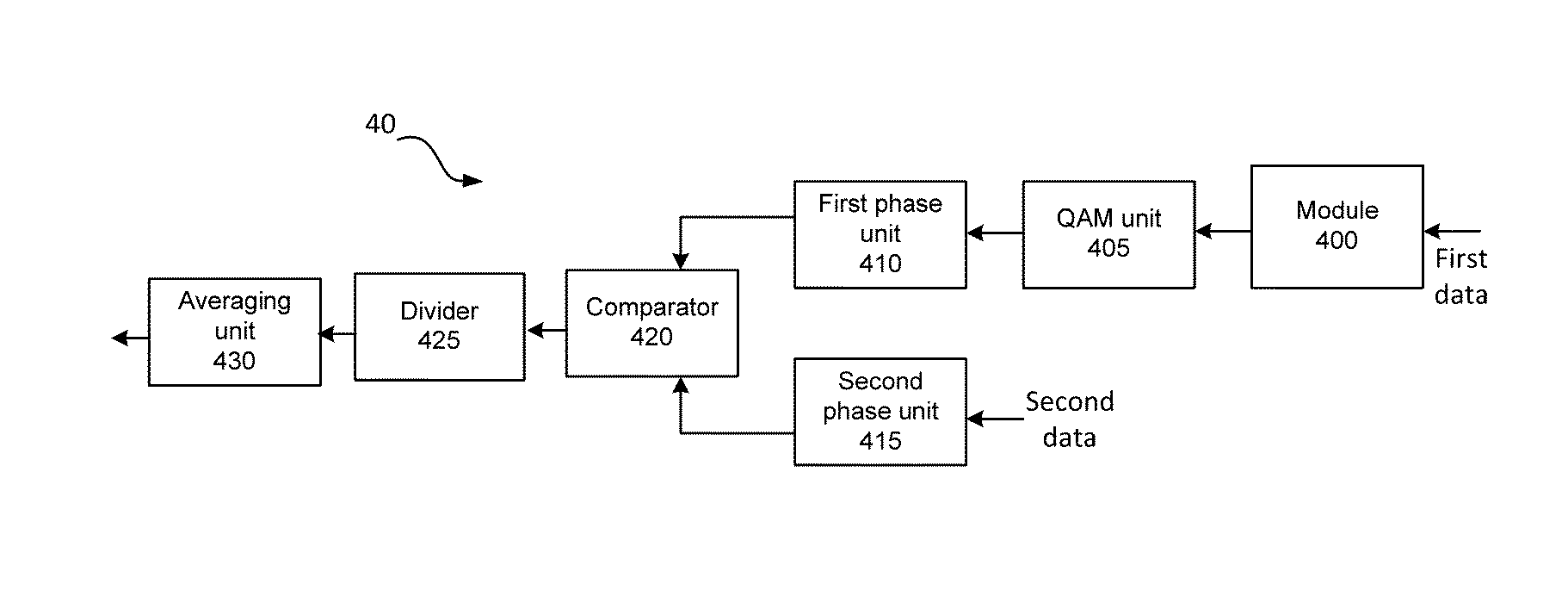

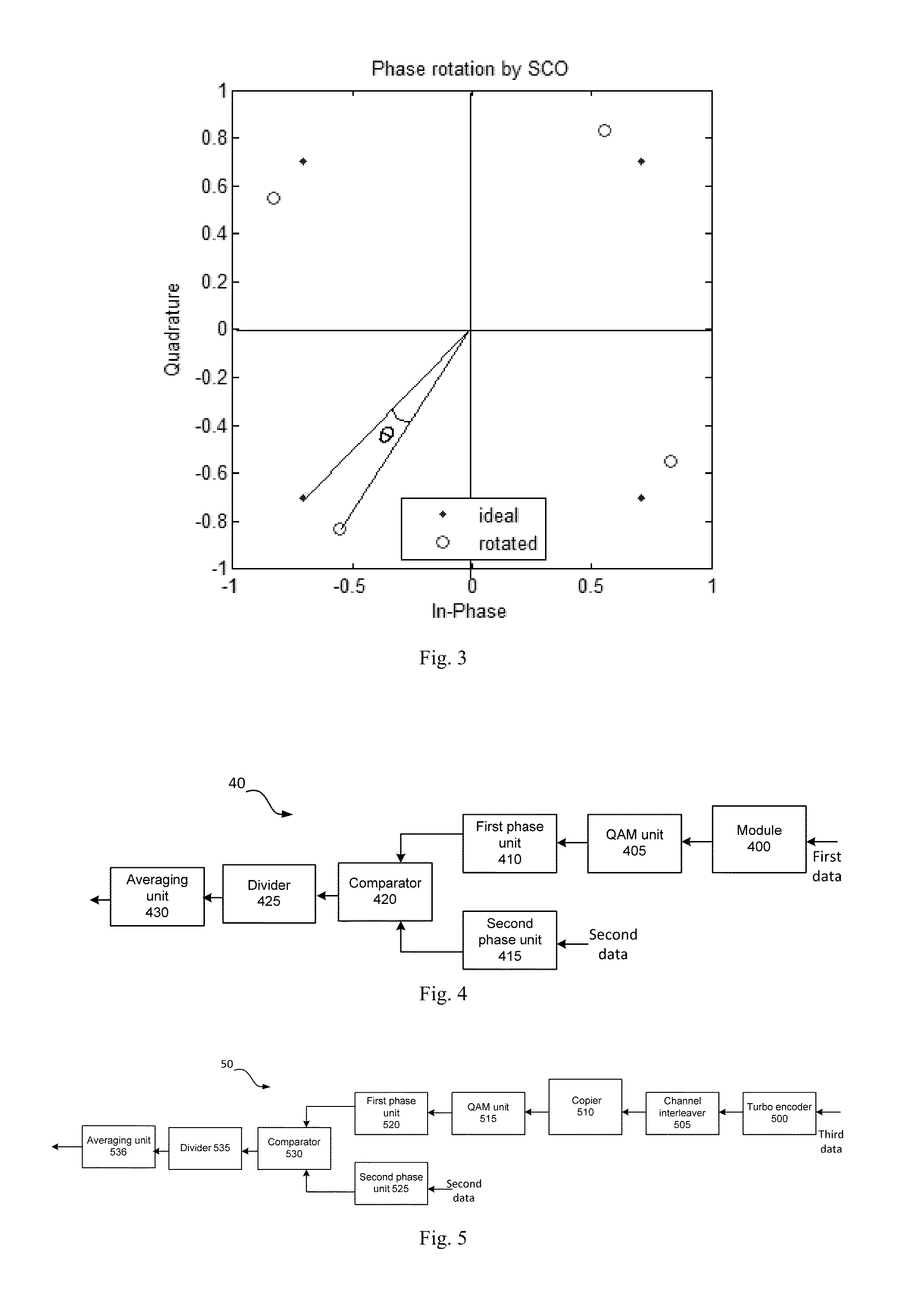

Method of estimating sampling clock offset, a sampling clock offset estimator and a receiver comprising the same

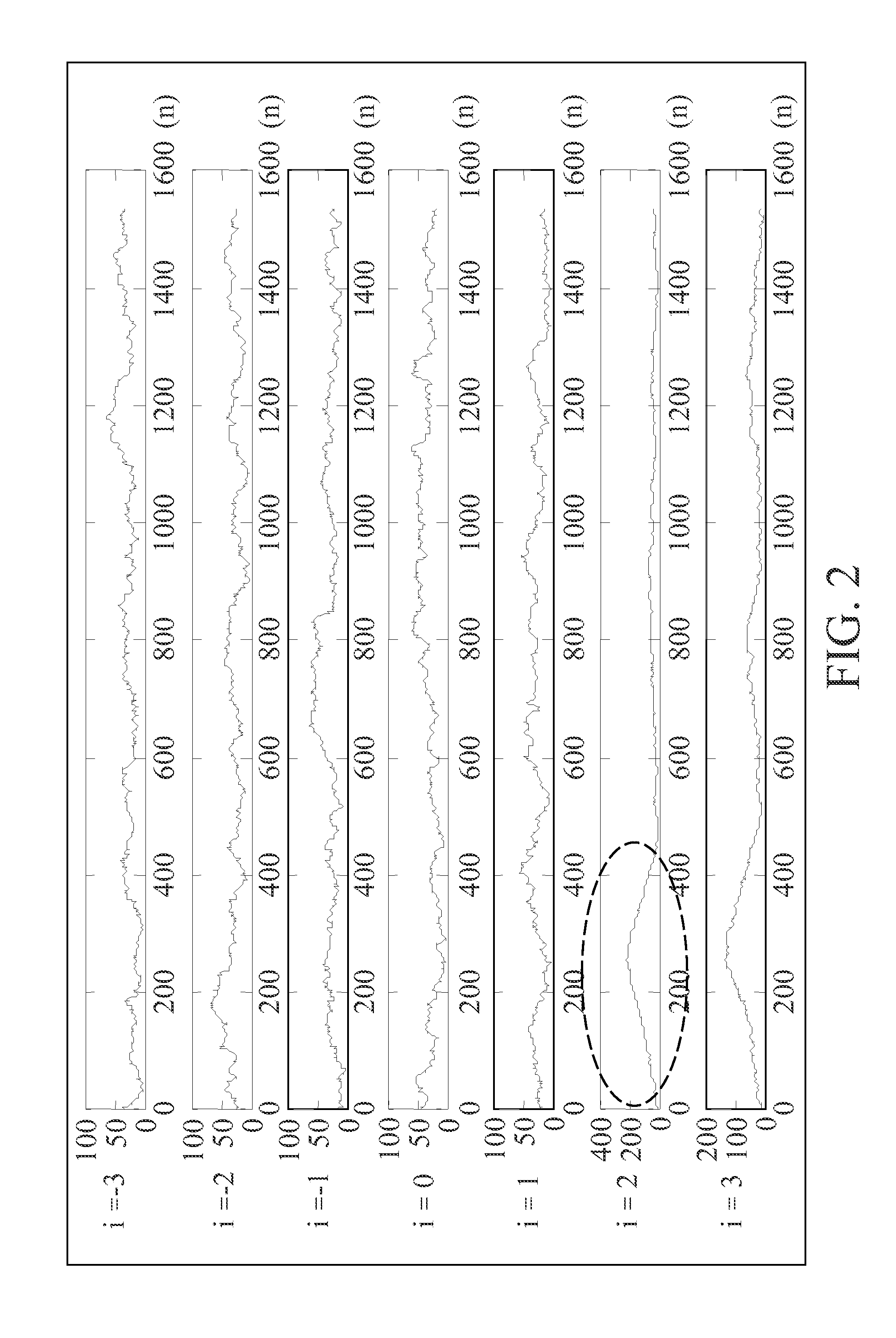

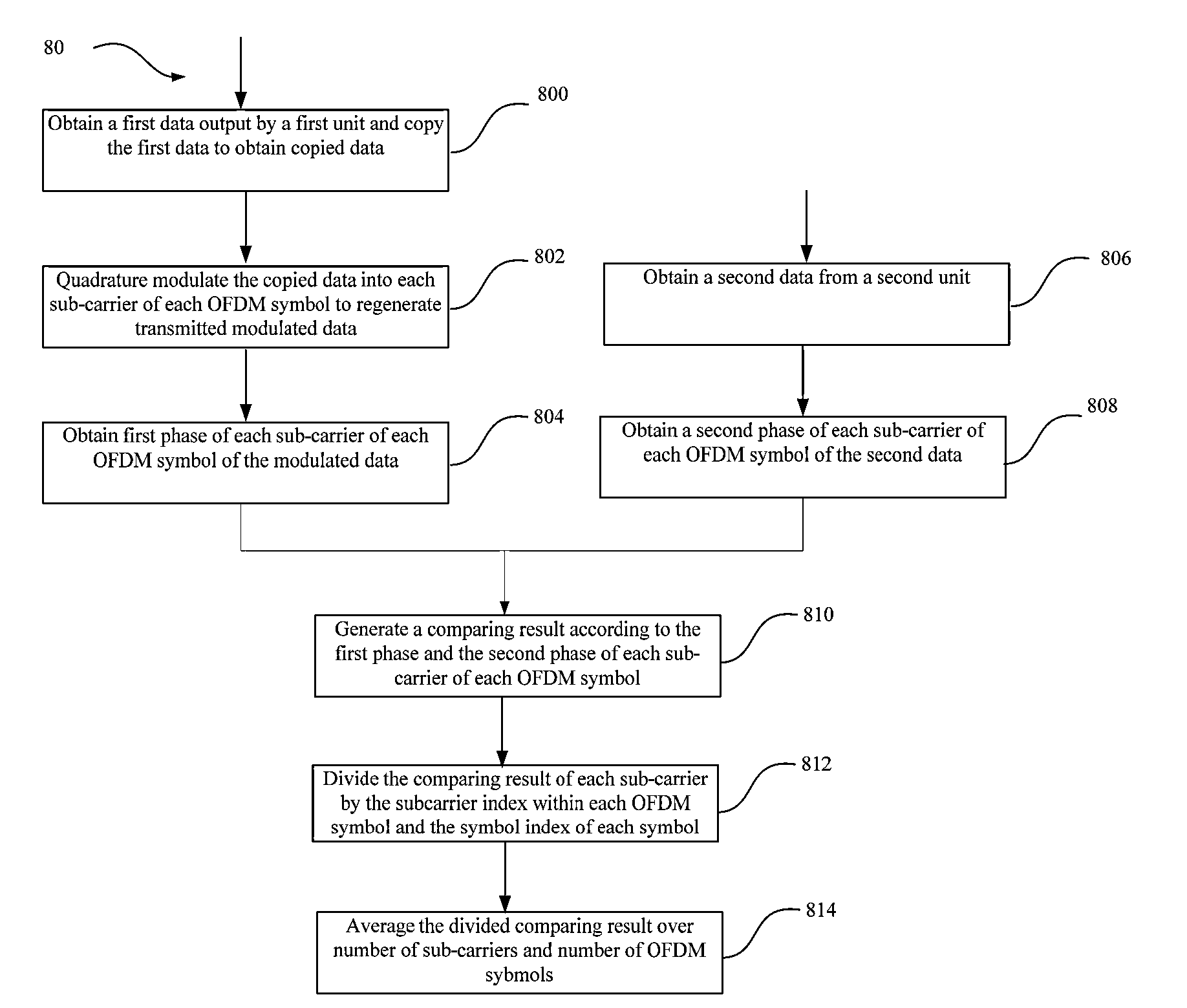

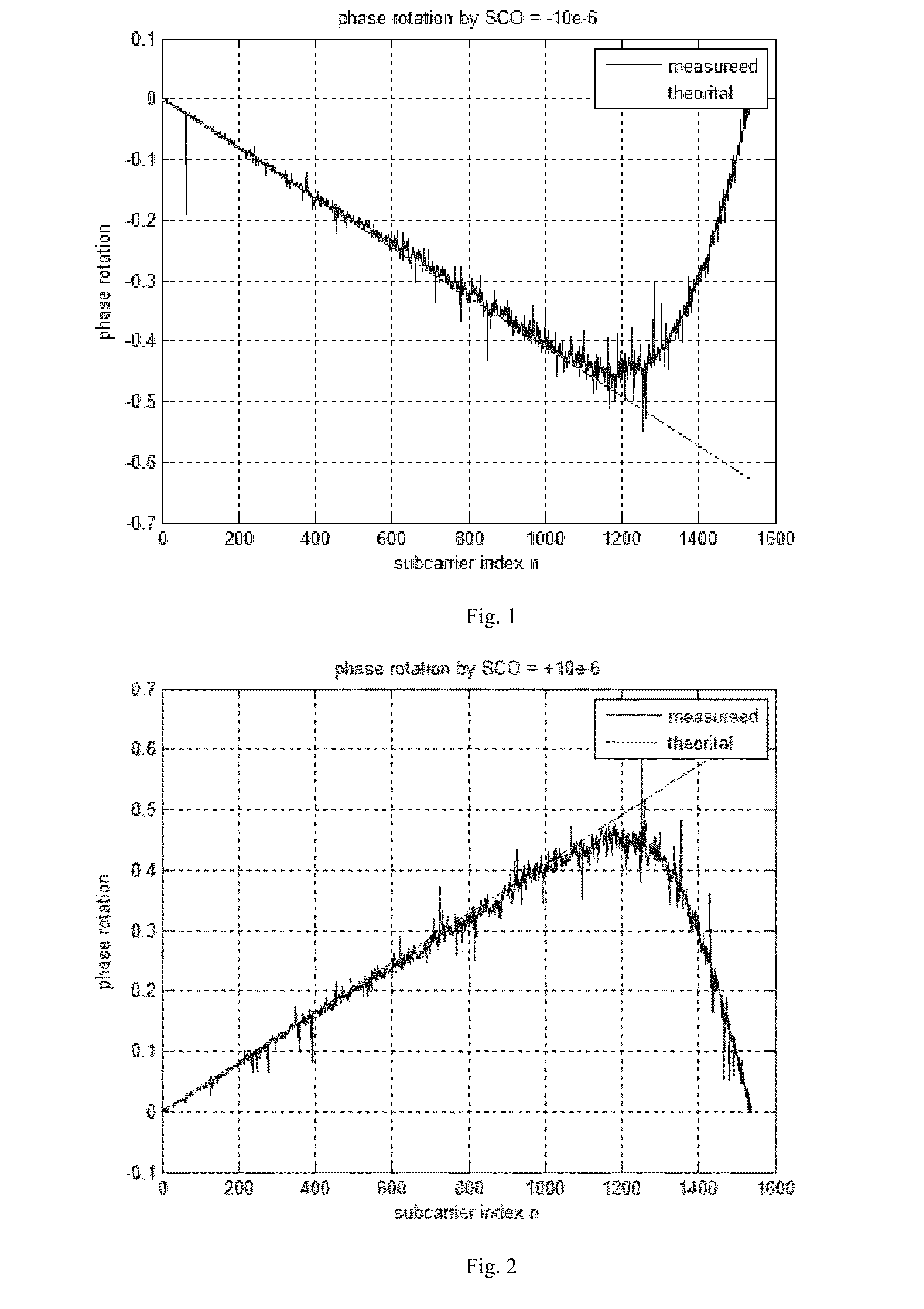

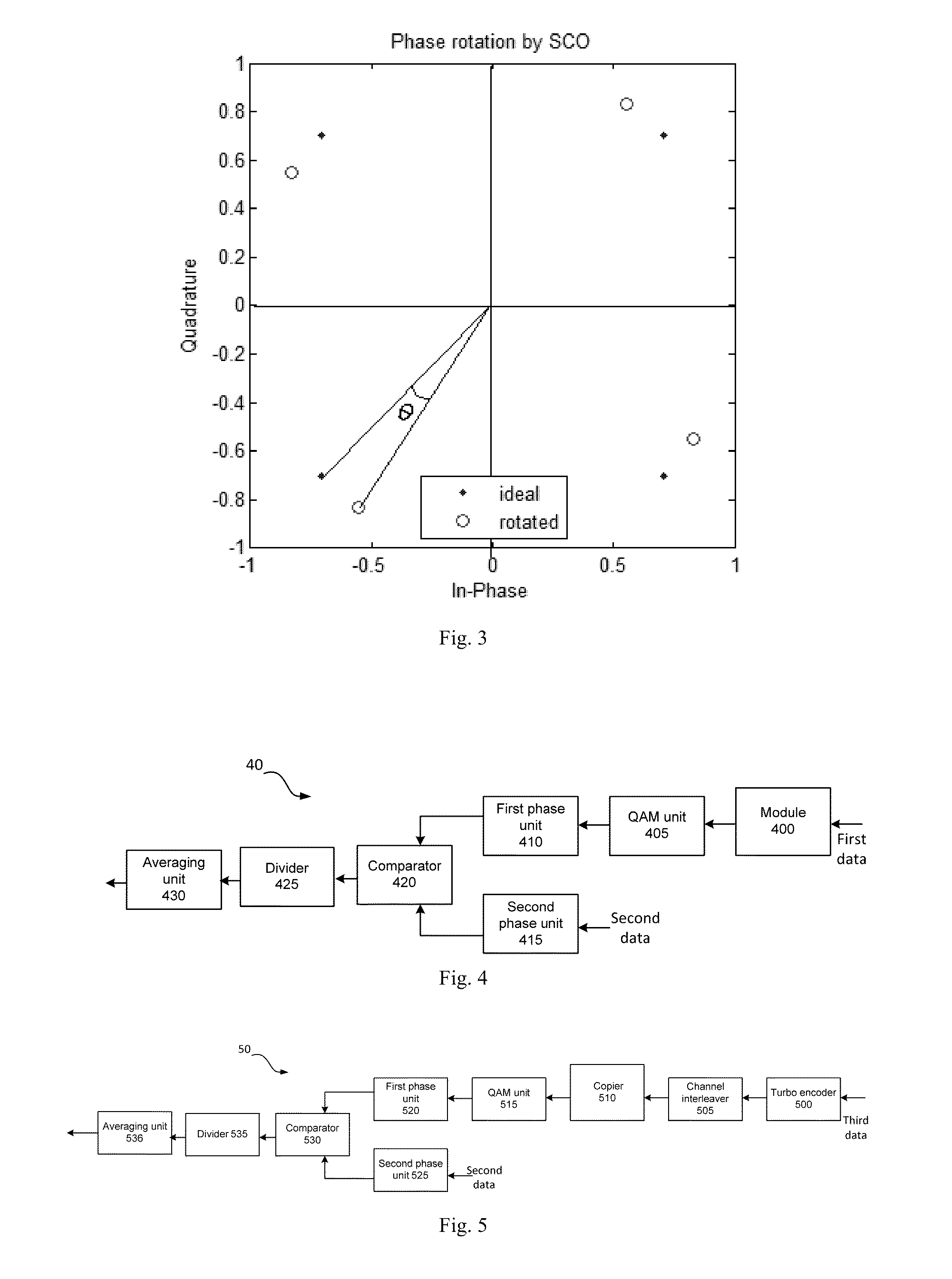

A SCO estimator comprises the following units. A module obtains a first data output by a first unit and copies the first data to obtain copied data. A QAM unit quadrature modulates the copied data into each sub-carrier of each OFDM symbol to regenerate transmitted modulated data. A first phase unit obtains a first phase of each sub-carrier of each OFDM symbol of the modulated data. A second phase unit obtains a second data from a second unit, and obtains a second phase of each sub-carrier of each OFDM symbol of the second data. A comparator generates a comparing result according to the first phase and the second phase of each sub-carrier of each OFDM symbol. A divider divides the comparing result of each sub-carrier by the subcarrier index within each OFDM symbol and the OFDM symbol index of each OFDM symbol. An averaging unit averages the divided comparing result over number of sub-carriers and number of OFDM symbols.

Owner:GREENVITY COMM

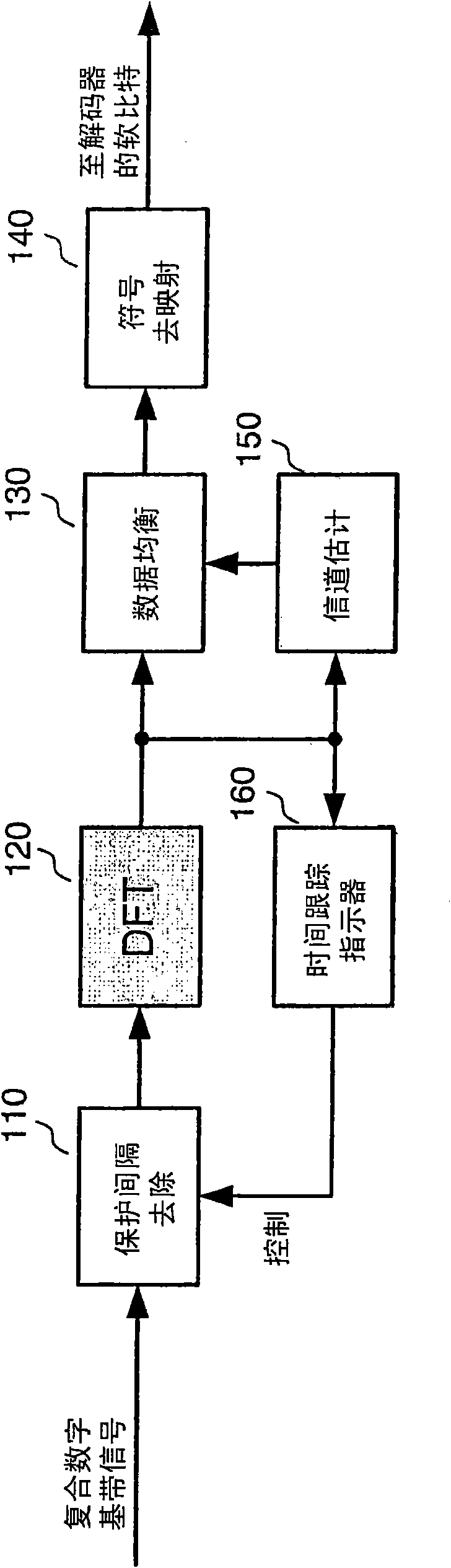

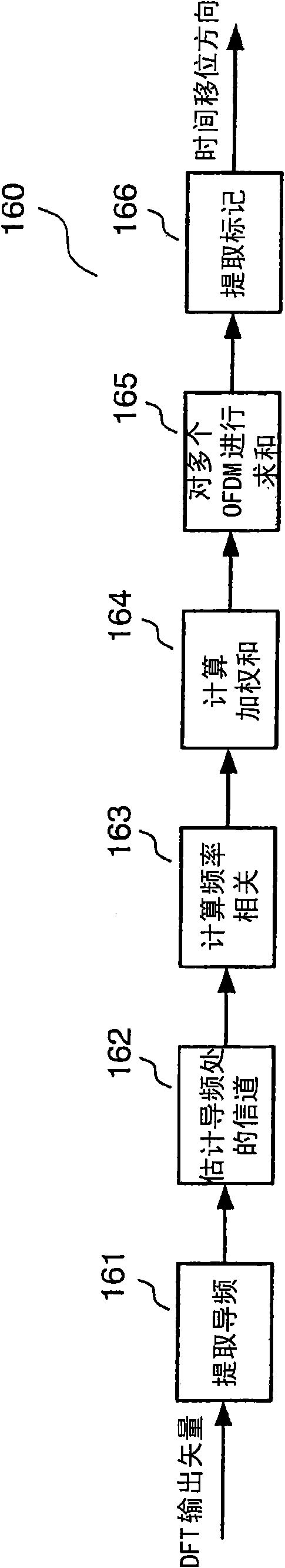

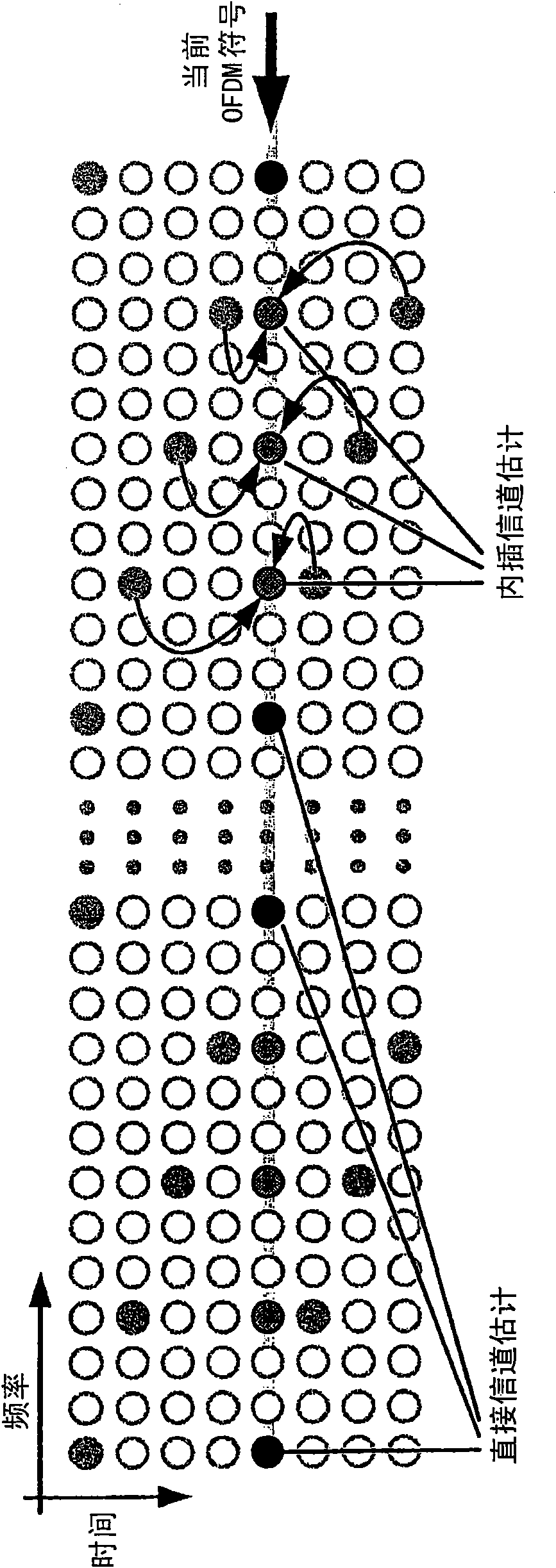

Post-DTF/FFT time tracking algorithm for OFDM receivers

InactiveCN102318304ADo not cause disturbanceLong channel impulse responseChannel estimationMulti-frequency code systemsChannel impulse responseTrack algorithm

A method for time synchronization tracking in an orthogonal frequency division multiplexing (OFDM) receiver is described, the method comprising the steps: obtaining a DFT output vector; determining a sample timing offset indication using reference symbols that are extracted from the DFT output vector; and adapting the OFDM symbol timing using said determined indication. In order to provide an improved post-DFT algorithm for estimating a time tracking error in OFDM receivers such as to allow an effective time tracking even in single frequency networks, and more particular to devise a time tracking algorithm for OFDM receivers that supports longer channel impulse responses without causing inter-symbol interference, said determining step comprises the steps of : (a) estimating (162) the channel transfer function at equidistant frequency positions using said reference symbols, for a first OFDM symbol; (b) determining (163) a plurality of autocorrelations of said channel transfer function at a specific set of small frequency offsets for said OFDM symbol; (c) repeating steps (a) and (b) for a plurality of subsequent OFDM symbols; (d) linearly combining (164,165) said plurality of autocorrelations for said plurality of OFDM symbols obtained in steps (a) through (c), for obtaining said sampling clock offset indication wherein the linear combining uses nonzero weights only. Further described is an orthogonal frequency division multiplexing (OFDM) receiver circuit arrangement performing this method.

Owner:NXP BV

Apparatus and method for tracking sampling clock in multi-carrier communication system

ActiveUS7583740B2Reduce complexityReduce computing loadAmplitude-modulated carrier systemsSecret communicationCommunications systemMulti carrier

Owner:REALTEK SEMICON CORP

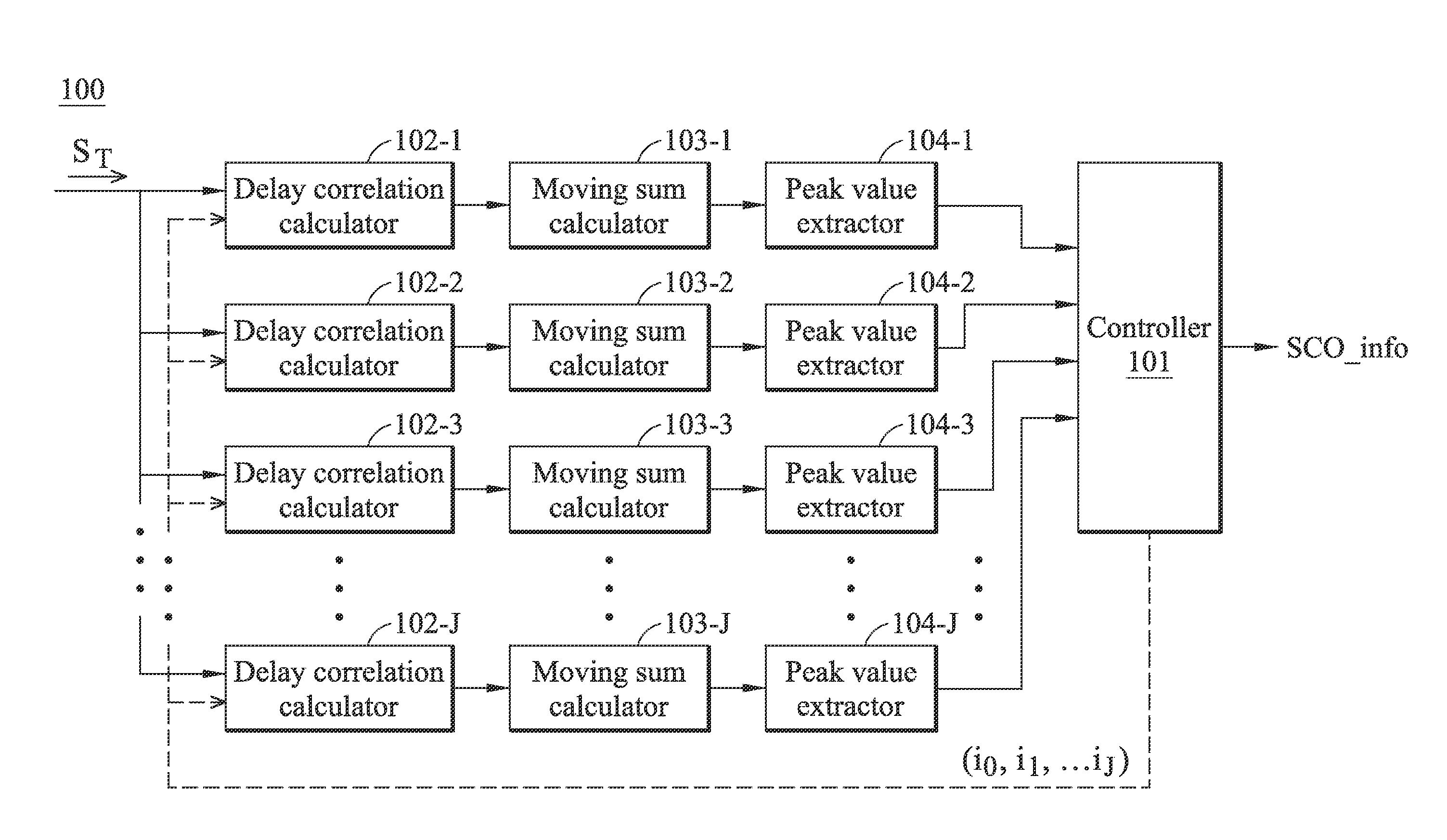

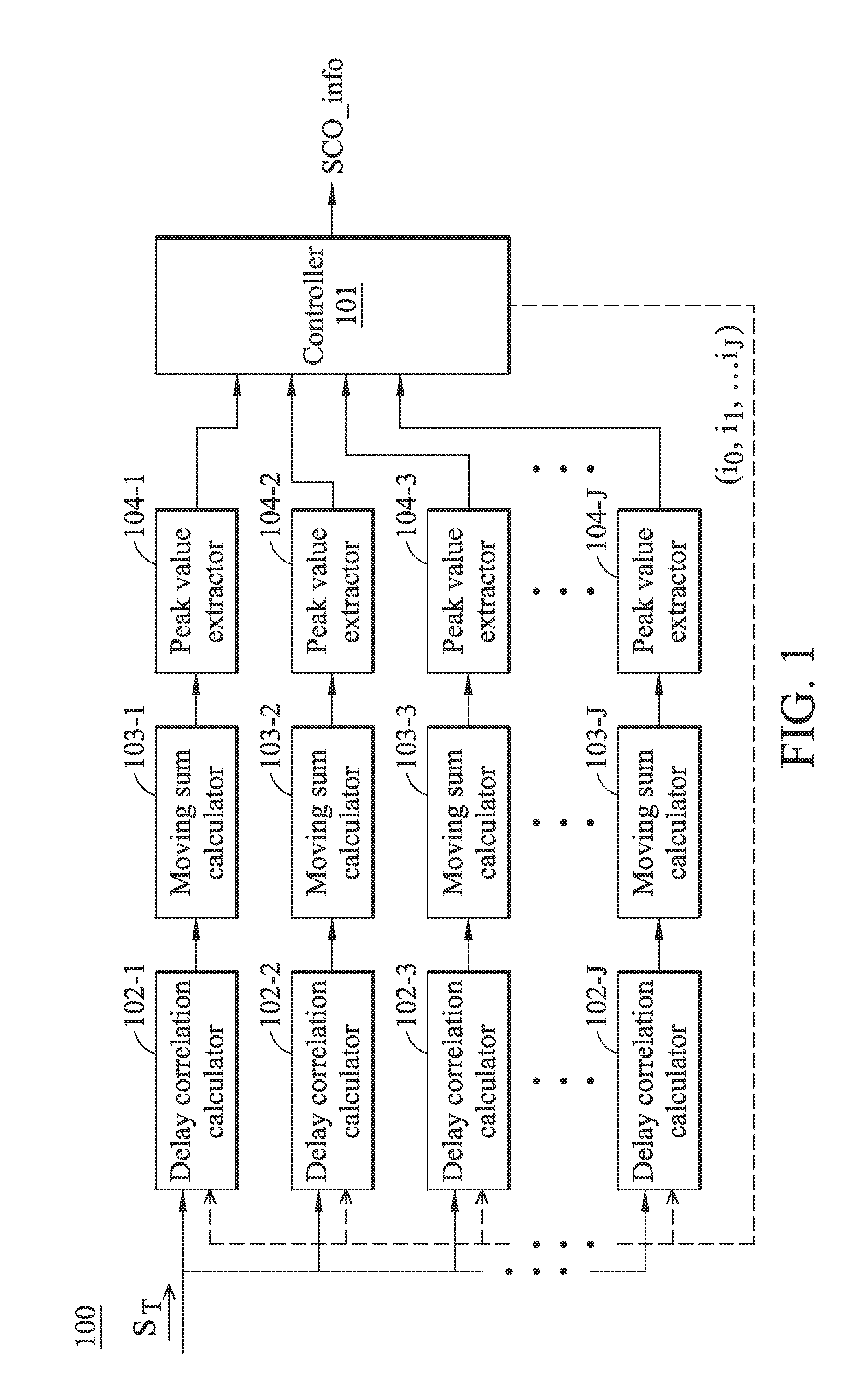

Compensating devices and methods for detecting and compensating for sampling clock offset

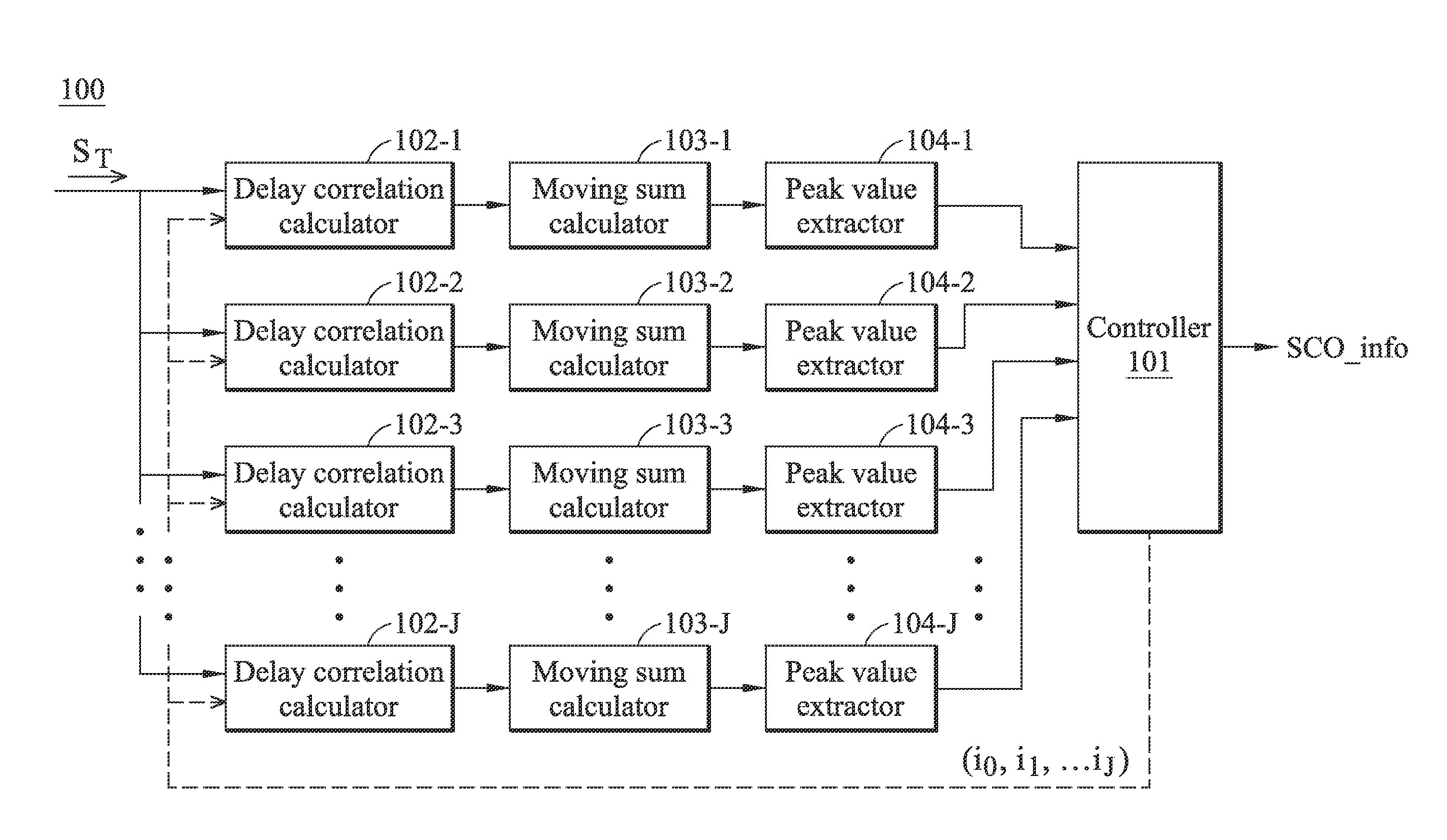

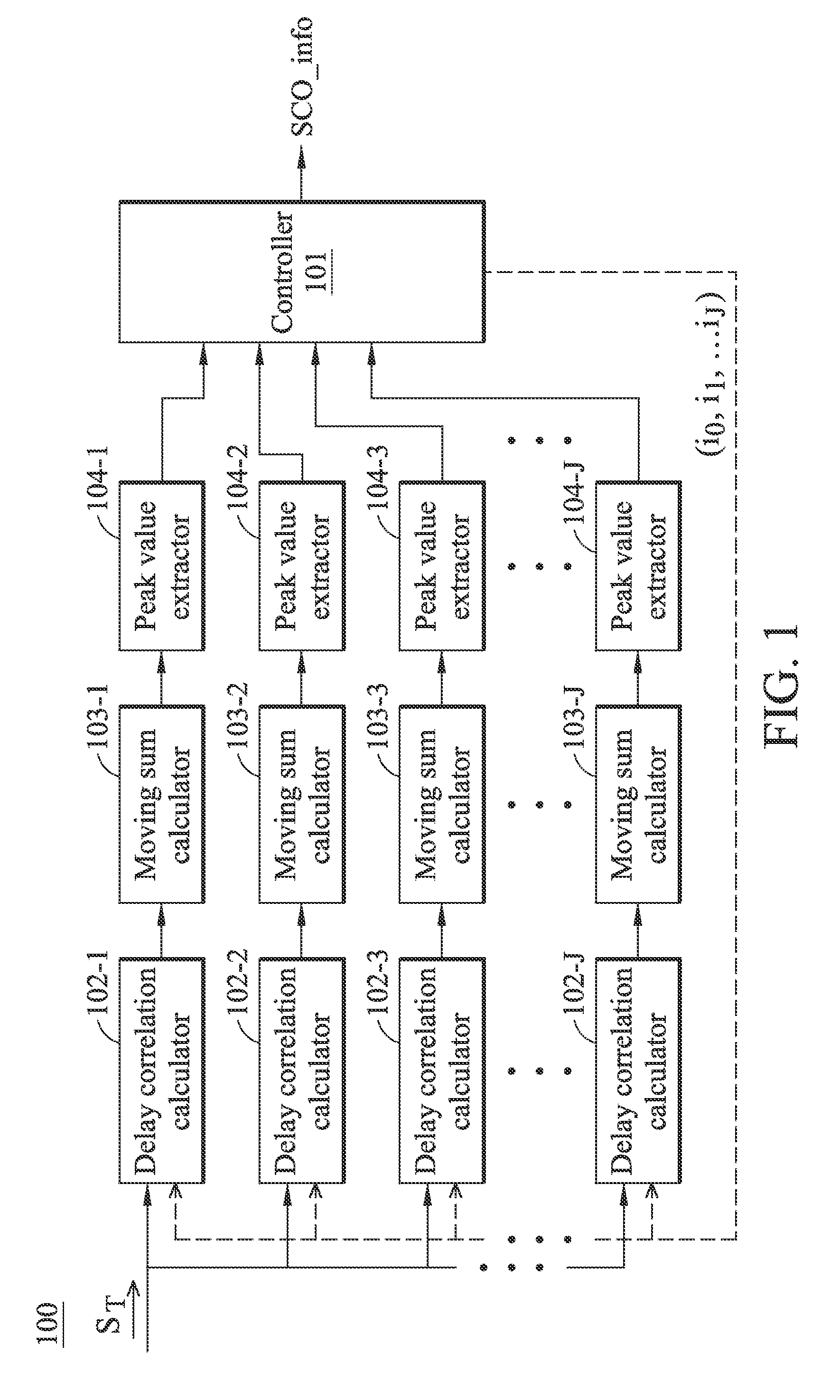

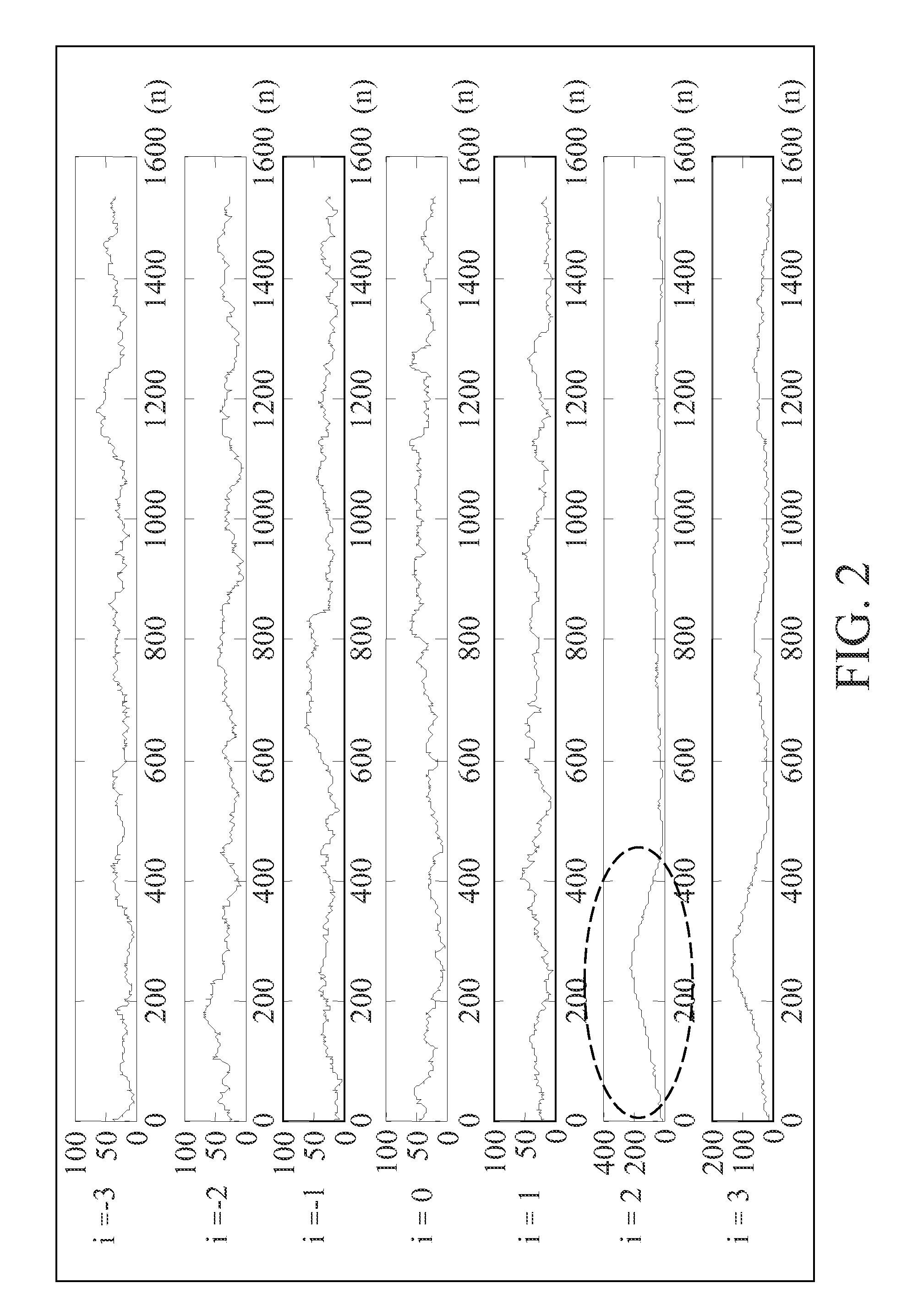

ActiveUS20130051504A1Amplitude-modulated carrier systemsAmplitude demodulationCorrelation coefficientTime domain

A compensating device for detecting and compensating for a sampling clock offset in a receiver. An SCO detector includes multiple calculation paths and a controller. Each calculation path receives a time domain signal and a hypothetic offset, calculates correlation coefficients between the time domain signal and a delayed version of the time domain signal according to a predetermined delay and the hypothetic offset, calculates correlation coefficient sums according to the correlation coefficients, and extracts a maximum correlation coefficient sum for the hypothetic offset from the correlation coefficient sums. The controller is coupled to the calculation paths for providing different hypothetic offsets to each calculation path and detects the SCO according to the maximum correlation coefficient sums obtained from the calculation paths. An SCO compensator receives the SCO and compensating for the SCO on a signal generated in a signal processing path of a receiver.

Owner:MEDIATEK INC

Method of estimating sampling clock offset, a sampling clock offset estimator and a receiver comprising the same

A SCO estimator comprises the following units. A module obtains a first data output by a first unit and copies the first data to obtain copied data. A QAM unit quadrature modulates the copied data into each sub-carrier of each OFDM symbol to regenerate transmitted modulated data. A first phase unit obtains a first phase of each sub-carrier of each OFDM symbol of the modulated data. A second phase unit obtains a second data from a second unit, and obtains a second phase of each sub-carrier of each OFDM symbol of the second data. A comparator generates a comparing result according to the first phase and the second phase of each sub-carrier of each OFDM symbol. A divider divides the comparing result of each sub-carrier by the subcarrier index within each OFDM symbol and the OFDM symbol index of each OFDM symbol. An averaging unit averages the divided comparing result over number of sub-carriers and number of OFDM symbols.

Owner:GREENVITY COMM

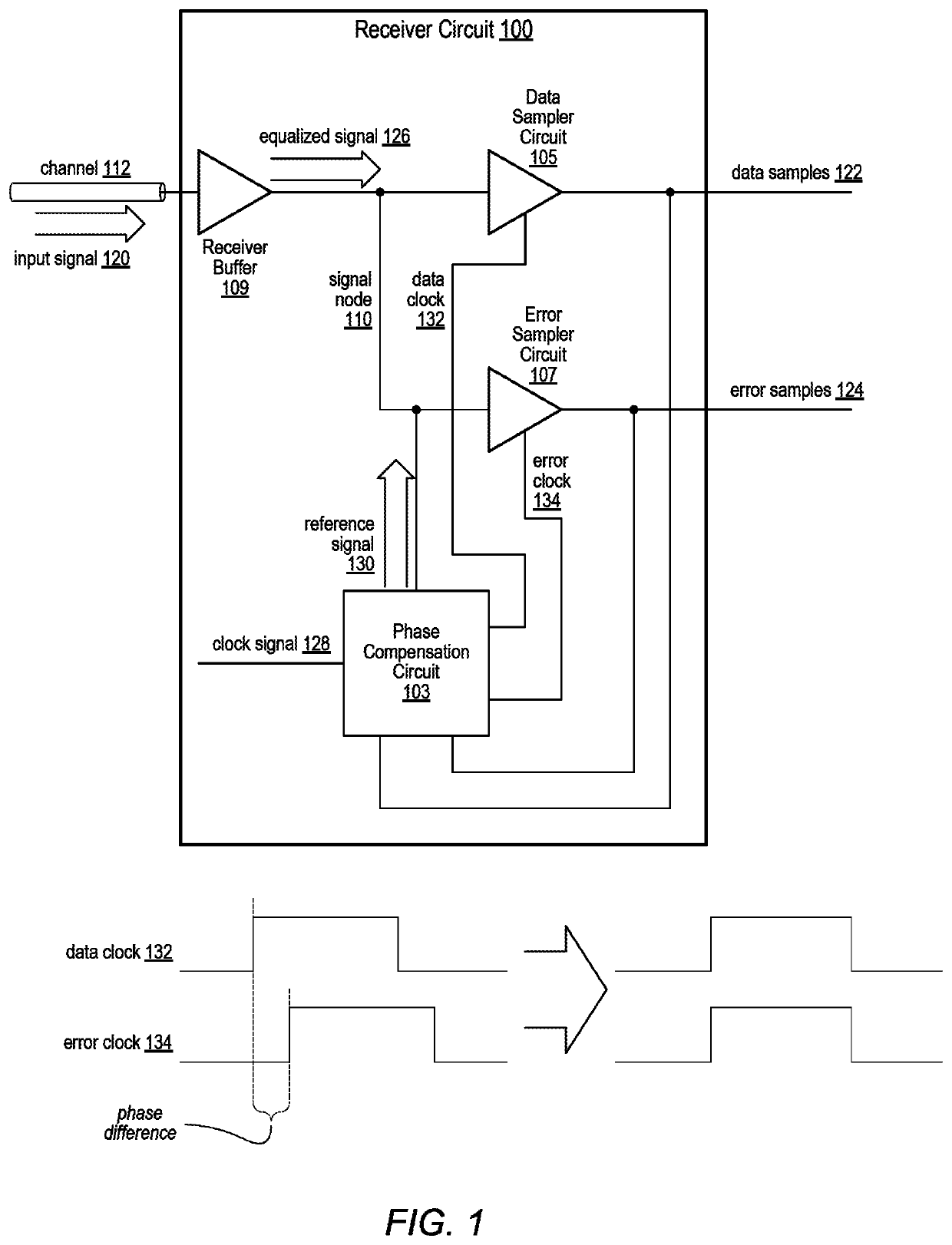

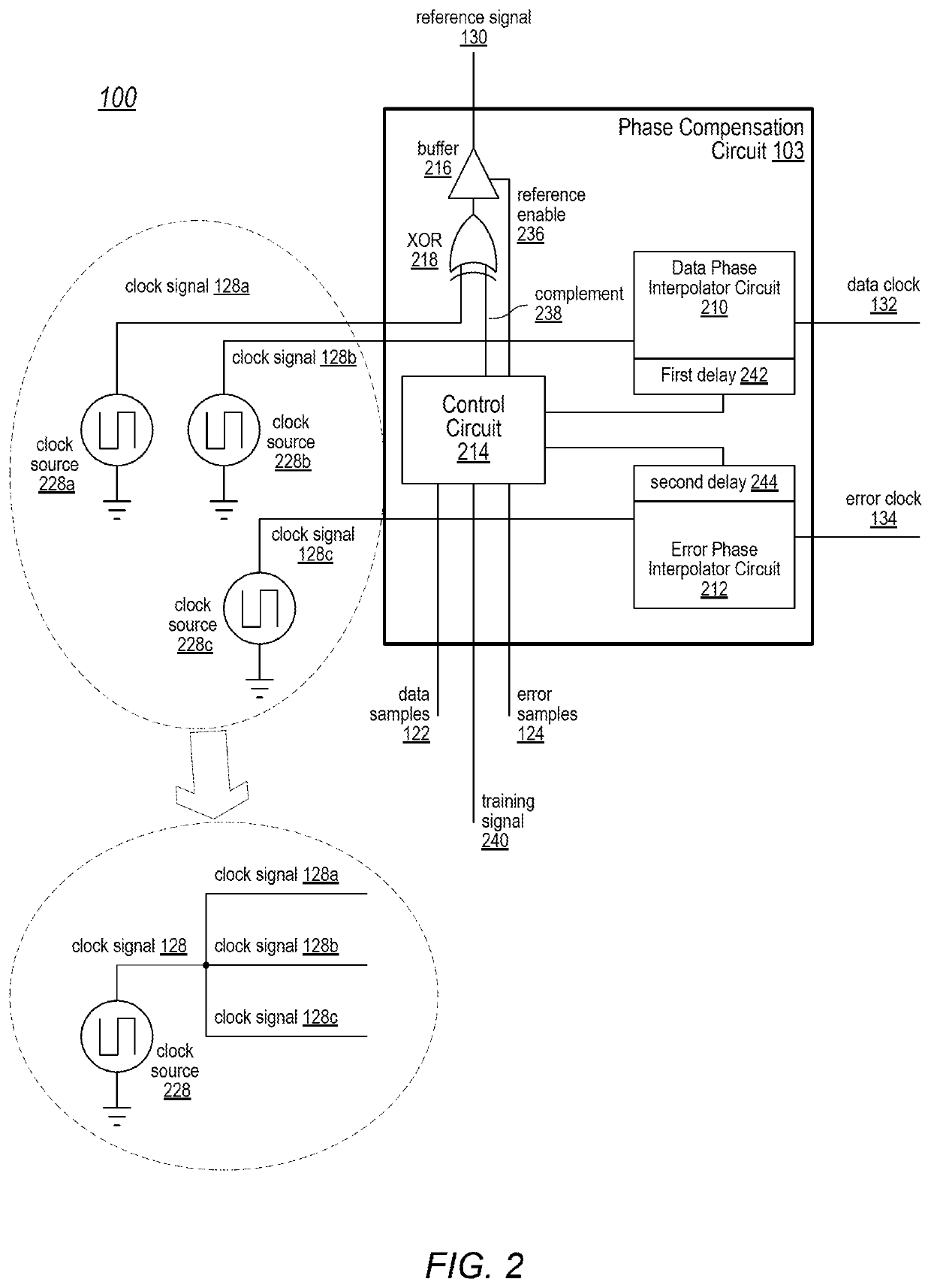

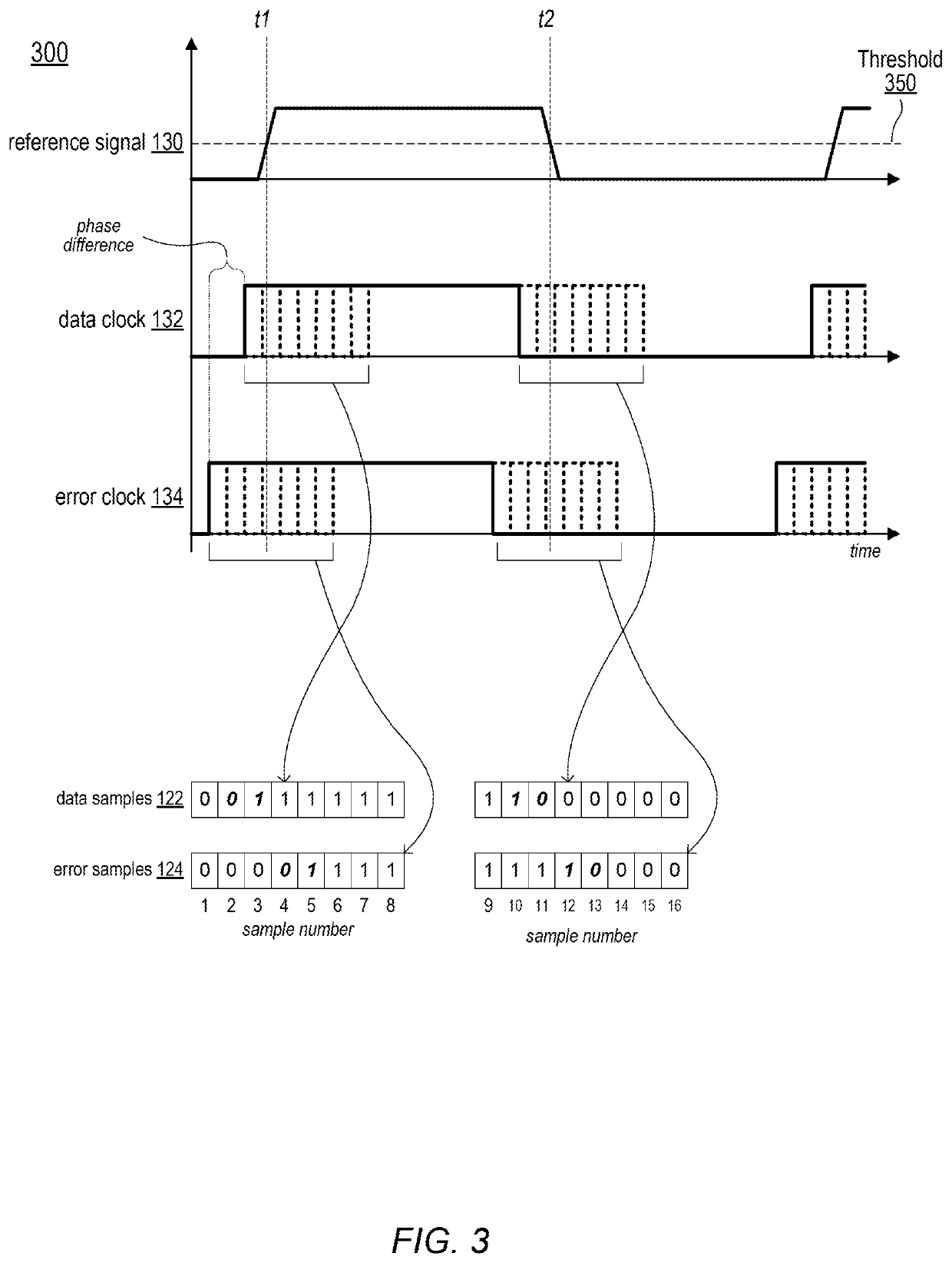

Serial data receiver with sampling clock skew compensation

An apparatus includes a receiver buffer, a phase compensation circuit, a data sampler circuit, and an error sampler circuit. The receiver buffer may generate an equalized signal on a signal node using an input signal received via a channel. The phase compensation circuit may, in response to an initiation of a training mode, replace the equalized signal on the signal node with a reference signal. The data sampler circuit may sample, using a data clock signal, the reference signal to generate a plurality of data samples. The error sampler circuit may sample, using an error clock signal, the reference signal to generate a plurality of errors samples. The phase compensation circuit may also adjust a phase difference between the data clock signal and the error clock signal using at least some of the plurality of data samples and at least some of the plurality of error samples.

Owner:APPLE INC

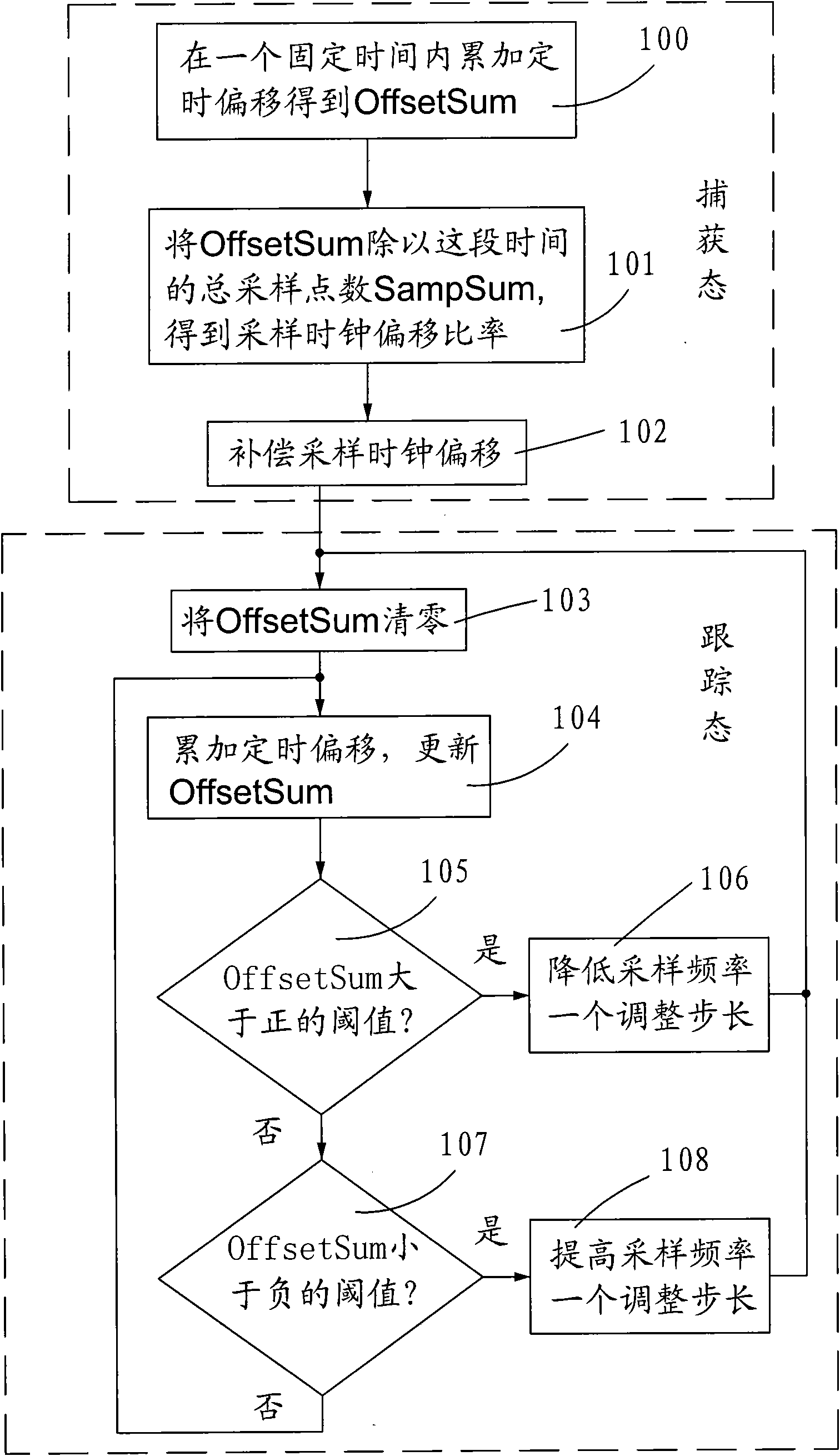

Method for estimating sampling clock skew based on orthogonal frequency division multiplexing system

ActiveCN101640658AImprove estimation accuracyImprove stabilityMulti-frequency code systemsComputer scienceFixed time

The invention relates to a method for estimating sampling clock skew based on an orthogonal frequency division multiplexing (OFDM) system. The method comprises the following steps: firstly analyzing the skew of a timed value in a period of fixed time to capture a skew value of a sampling clock, then tracking the skew of the sampling clock, and fine tuning the skew of the sampling clock after accumulating the skew of the timed value to a threshold value. The method directly uses a sign timing synchronous result for computation, reduces the realization complexity and has high estimated accuracyand stability.

Owner:FUZHOU ROCKCHIP SEMICON

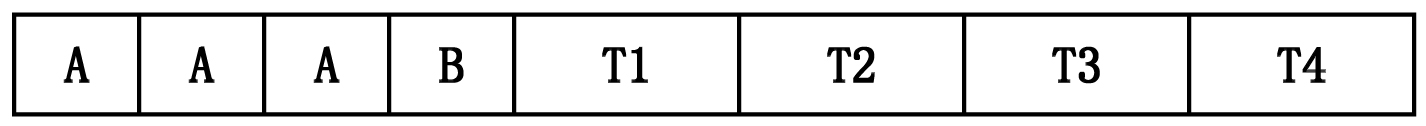

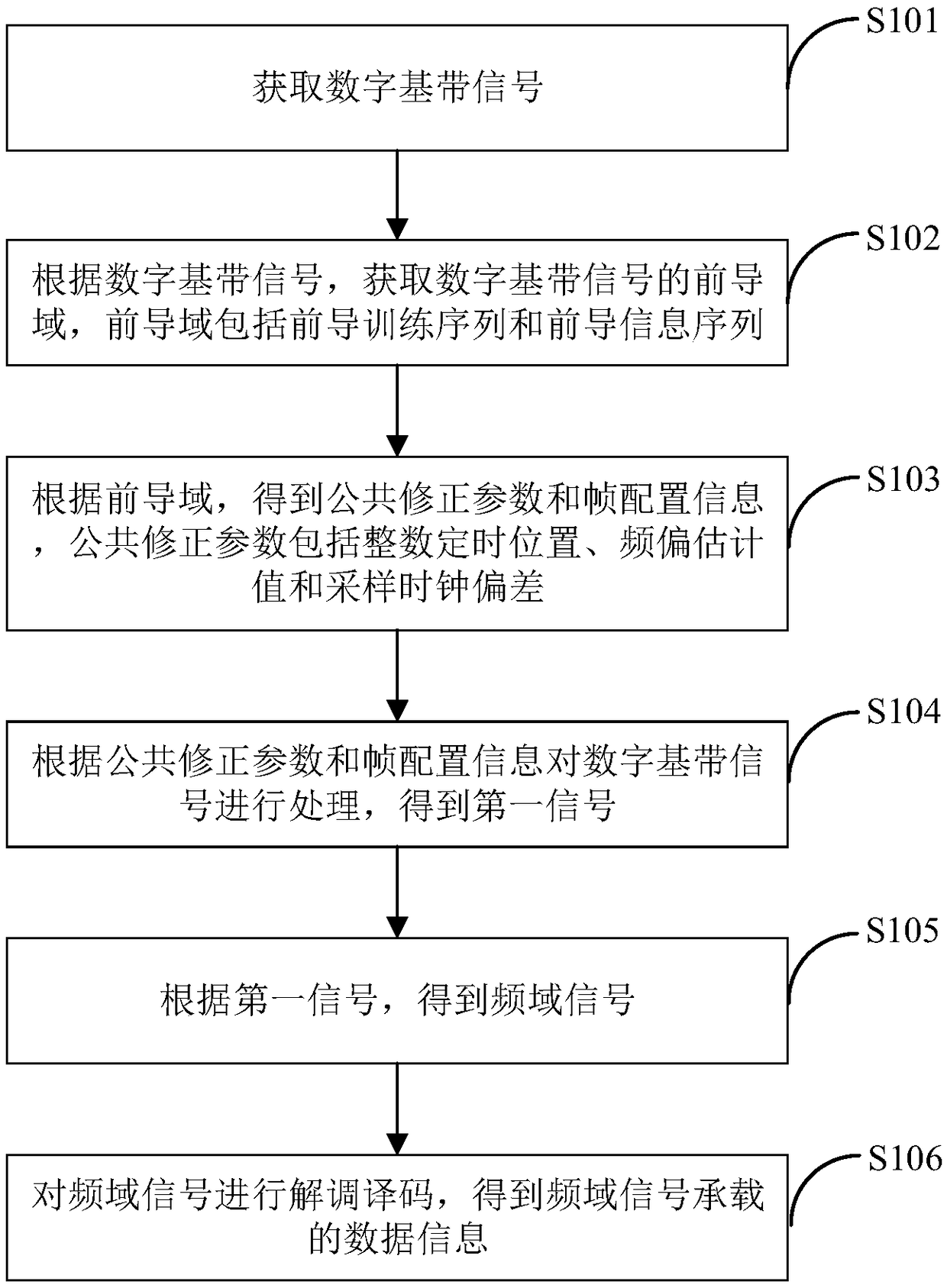

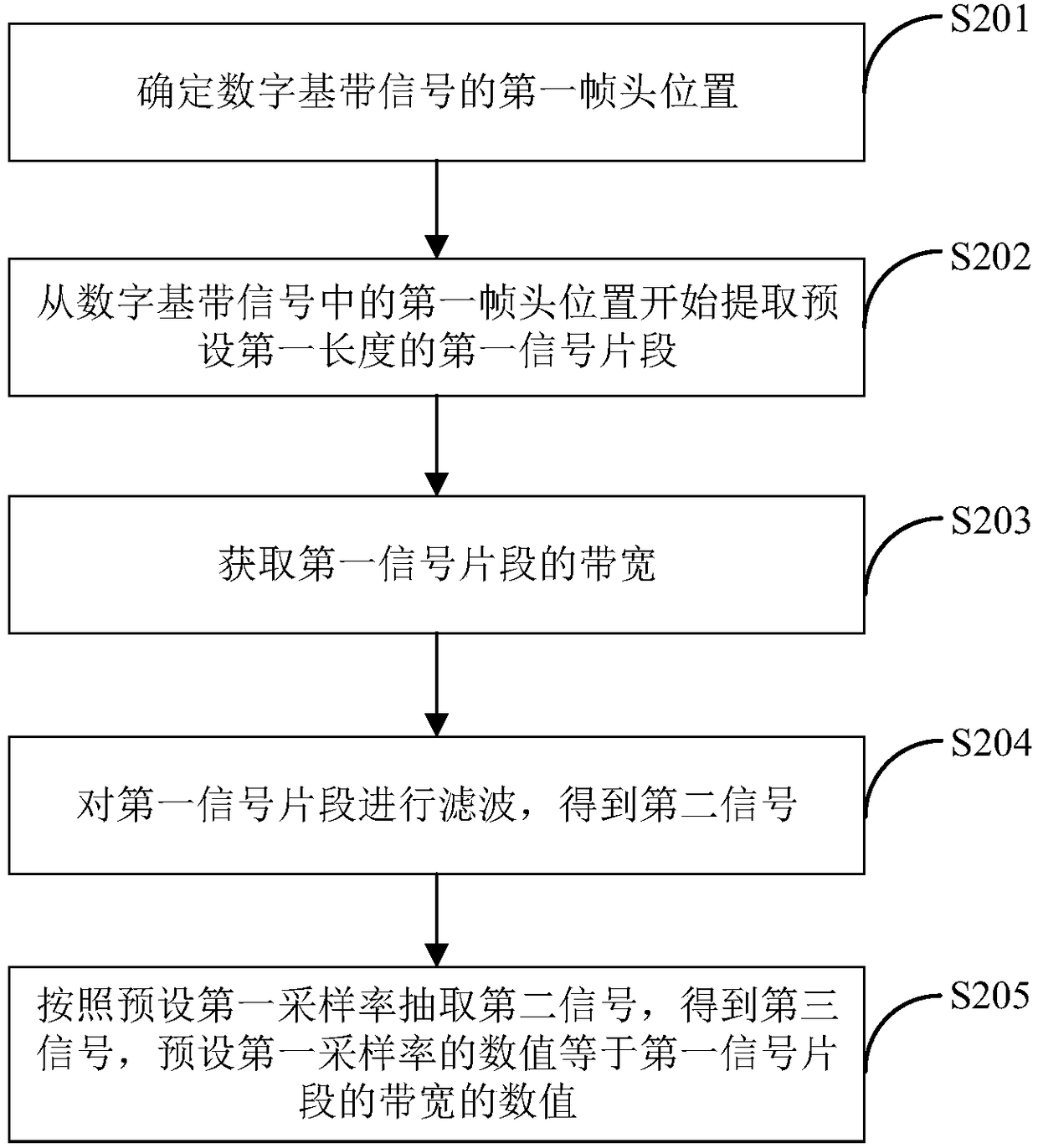

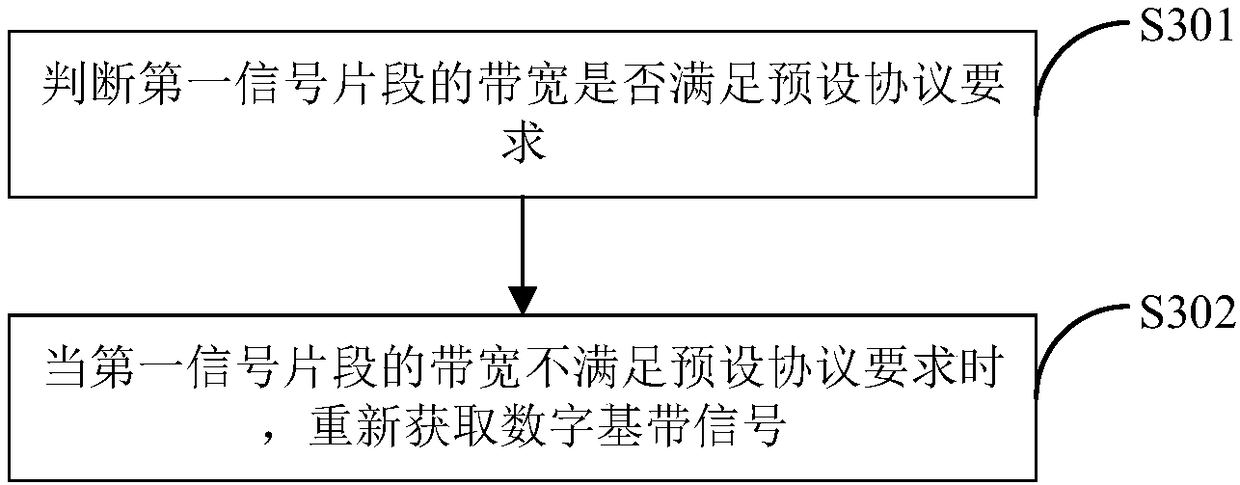

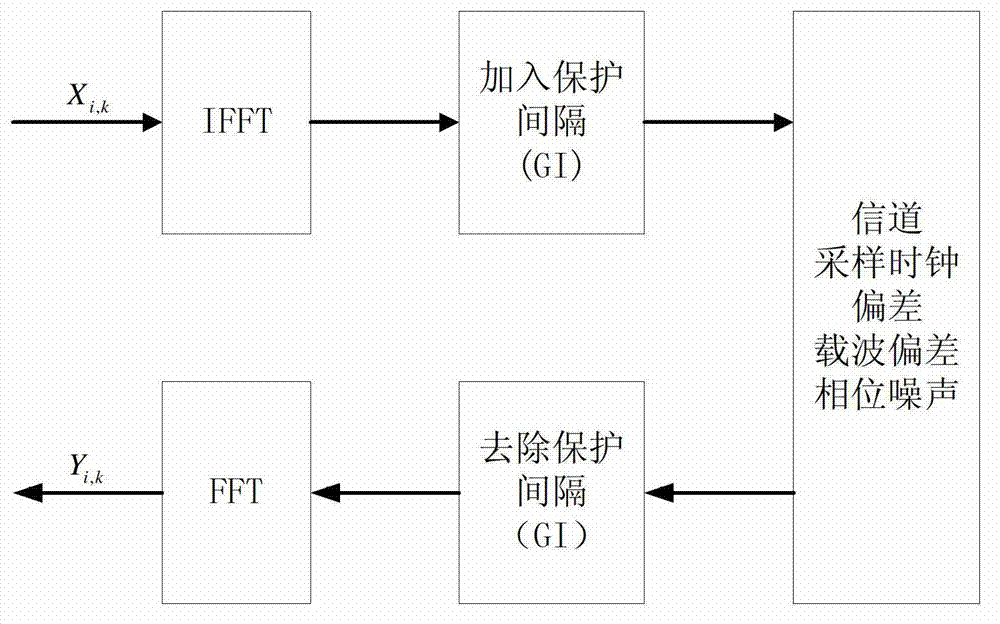

Signal demodulation method and baseband receiver

ActiveCN108200002AImplement Compensation CorrectionImprove signal qualityCarrier regulationMulti-frequency code systemsBaseband receiverSignal quality

The invention is applicable to the technical field of wireless communications, and provides a signal demodulation method and a baseband receiver. The signal demodulation method comprises the followingsteps: acquiring a digital baseband signal; acquiring a leading domain of the digital baseband signal, wherein the leading domain comprises a leading training sequence and a leading information sequence; acquiring a public correction parameter and frame configuration information according to the leading domain, wherein the public correction parameter comprises an integer timing position, a frequency offset estimated value and a sampling clock offset; processing the digital baseband signal according to the public correction parameter and the frame configuration information to acquire a first signal; acquiring a frequency domain signal according to the first signal; and performing demodulation and decoding on the frequency domain signal, thus acquiring data information supported by the frequency domain signal. The signal demodulation method disclosed by the invention realizes compensation and correction of the frequency offset estimated value, a timing position offset and the sampling clock offset, thereby improving the signal quality and the decoding performance.

Owner:TP-LINK

Method and device for computing correlation peak values

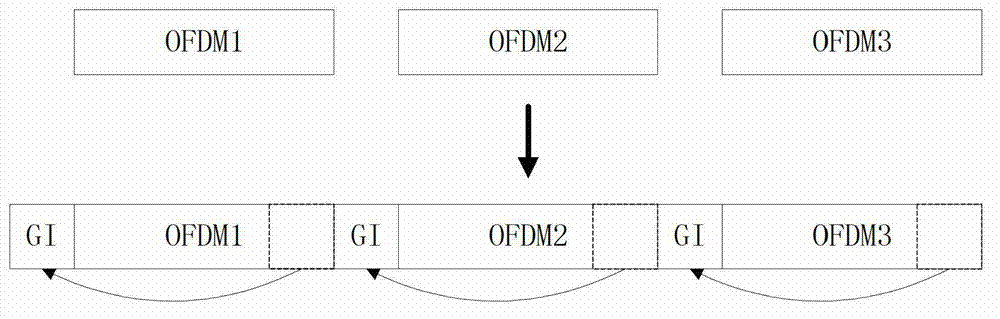

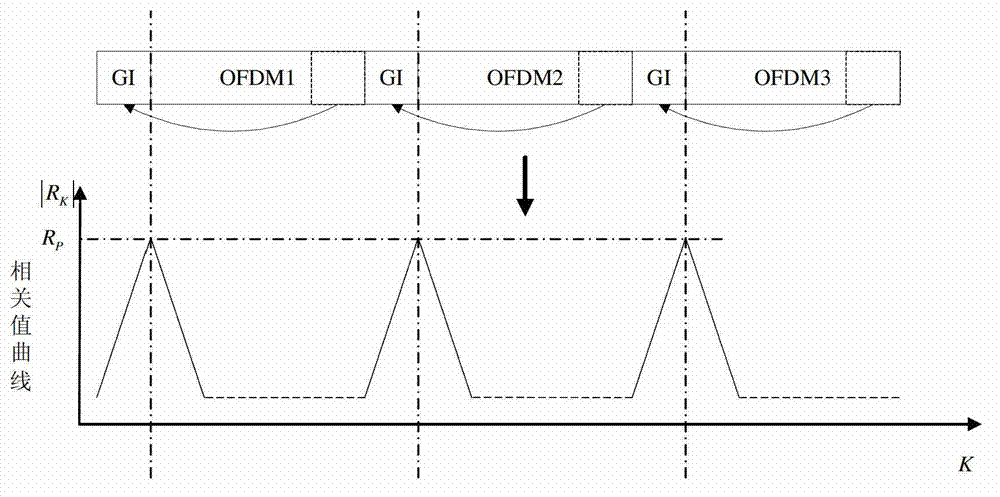

An embodiment of the invention relates to a method and a device for computing correlation peak values. The method includes determining offset according to sampling clock offset and the length of OFDM (orthogonal frequency division multiplexing) characters, computing first correlation values according to the offset and acquired data, and searching out the first correlation peak value from the first correlation values. Accordingly, by the method in the embodiment, the offset is added into a correlation value computing formula when offset exists in sampling clock frequency, and finally the correlation peak value can be computed.

Owner:HAIER BEIJING IC DESIGN

Symbol alignment in high speed optical orthogonal frequency division multiplexing transmission systems

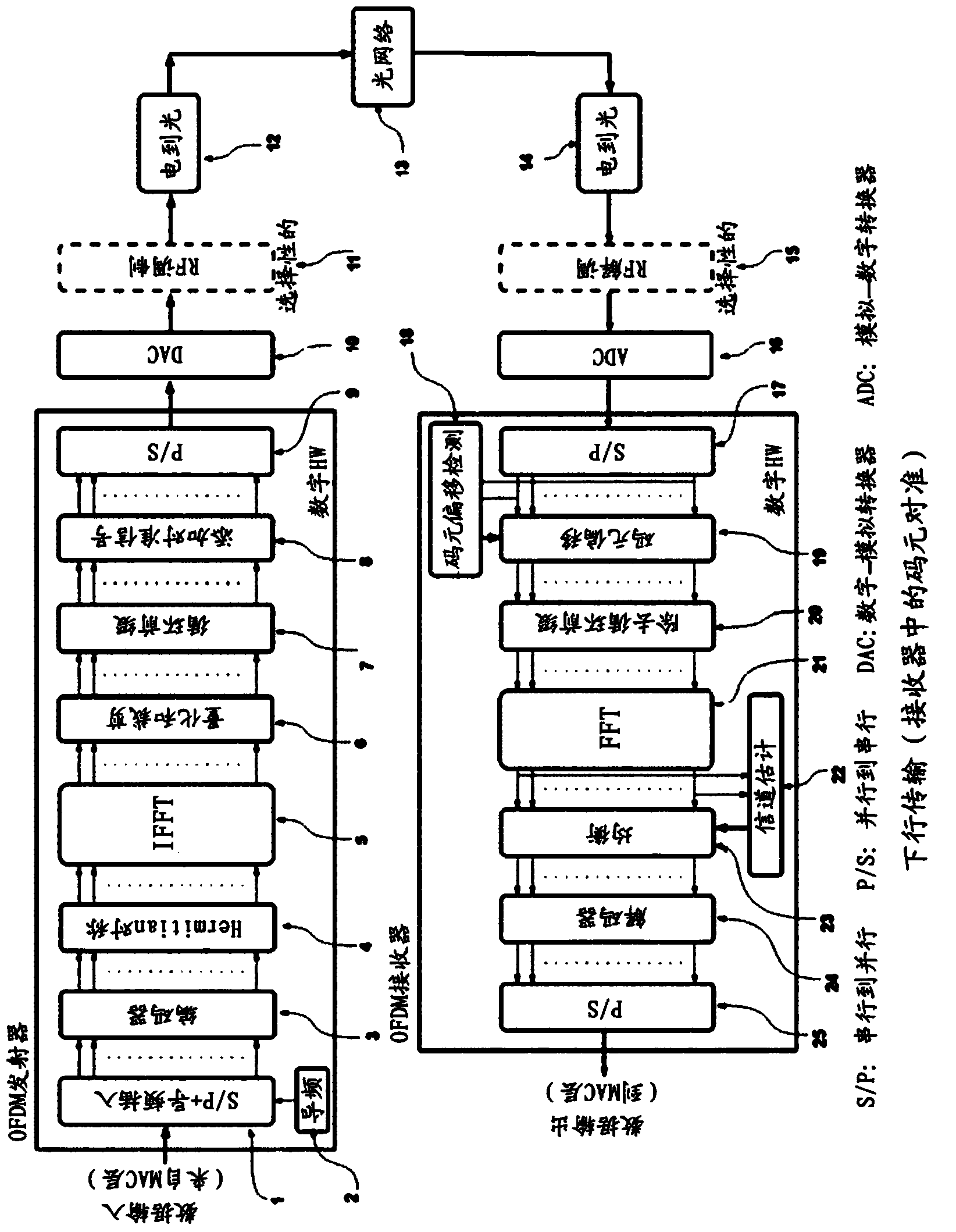

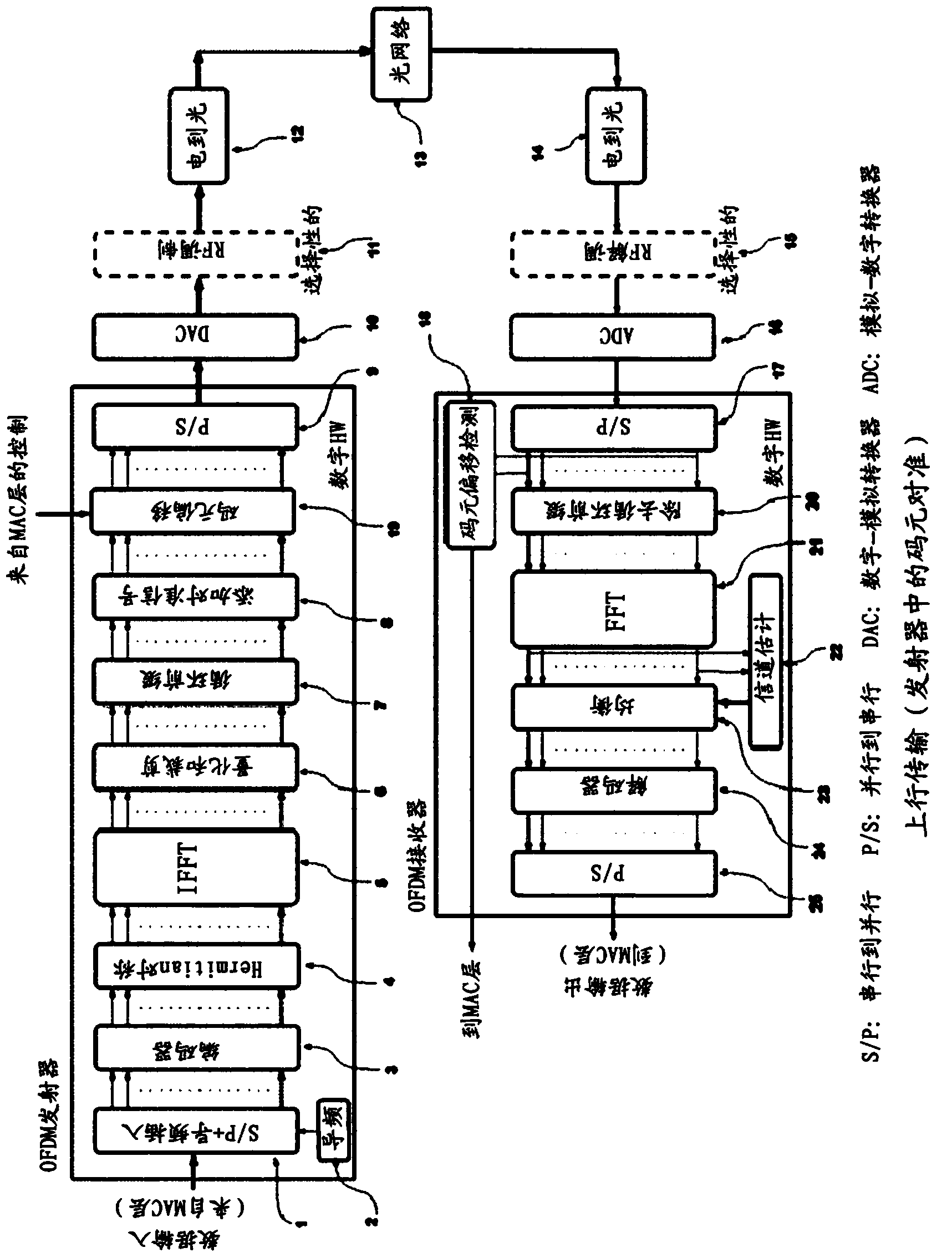

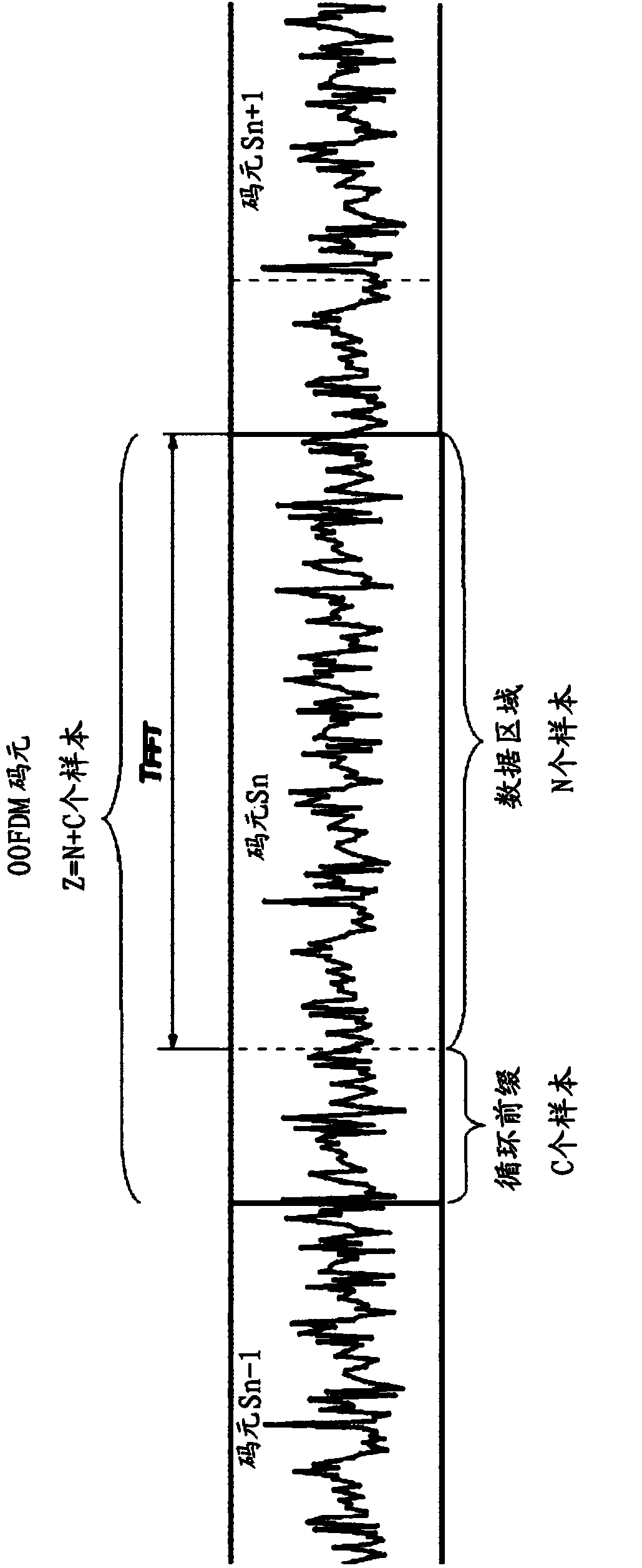

InactiveCN103621031AReduce complexityOptical multiplexMulti-frequency code systemsSoftware engineeringPhysical layer

The present invention discloses a method for symbol synchronisation in high speed optical orthogonal frequency division multiplexing (OOFDM) transmission systems via coding the electrical OFDM symbols by adding an independent low power-level alignment signal, converting the encoded signal into the optical domain for transmission, and in the receiver converting the received optical signal to the electrical domain and digitally processing to detect the symbol alignment offset by utilising the independent low-power level alignment signal. The present invention is suitable for point-to-point and point-to-multipoint OOFDM networks and has the additional features of timeslot and frame alignment, compensation for receiver sampling clock offset and providing physical layer network security.

Owner:UNIV OF WALES BANGOR

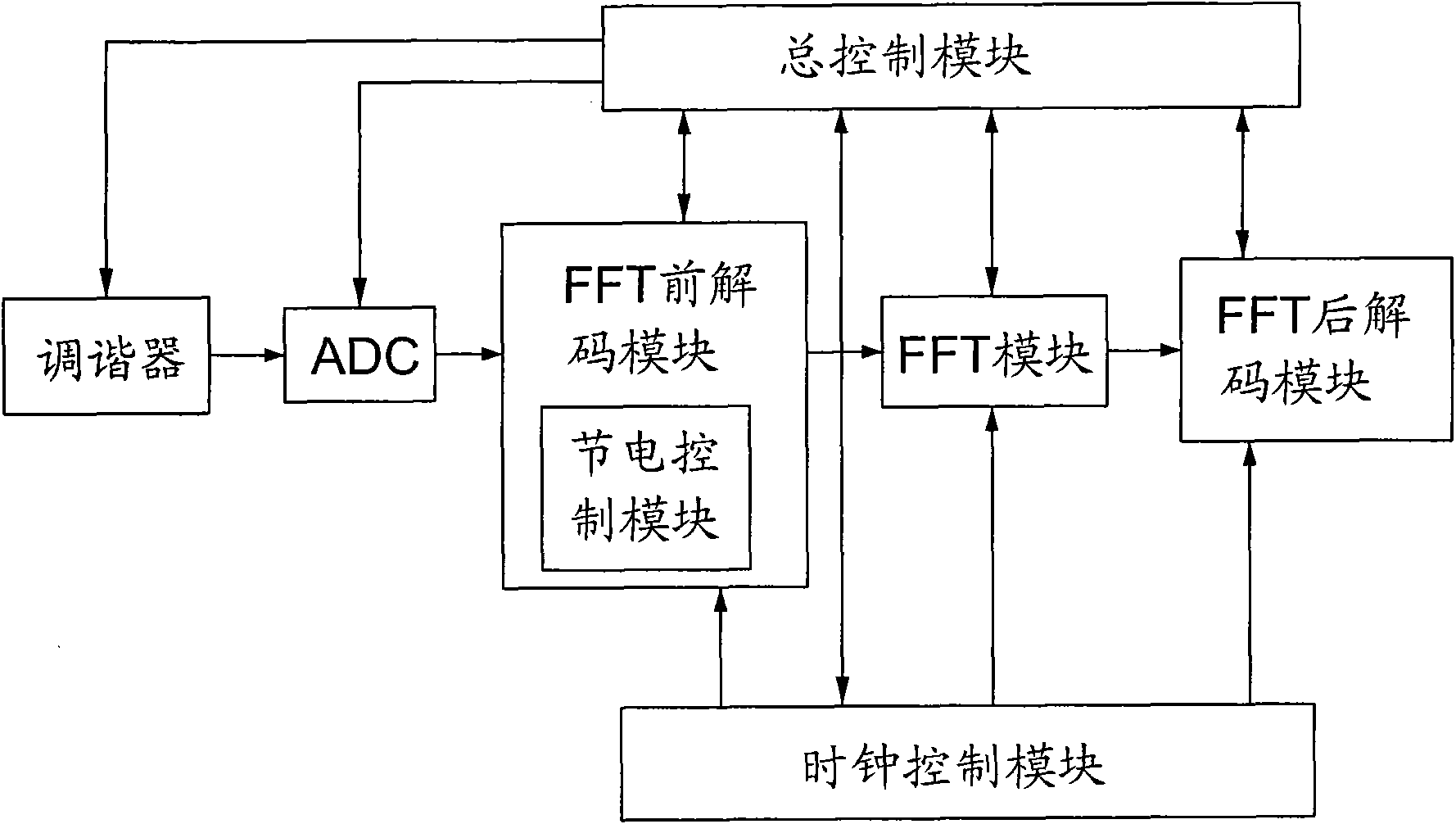

OFDM-based electricity-saving method for mobile digital multimedia broadcasting receiver

ActiveCN101631210AReduce power consumptionTelevision system detailsColor television detailsCode moduleElectricity

The invention relates to an OFDM-based electricity-saving method for a mobile digital multimedia broadcasting receiver. The method comprises the following steps: a channel to be decoded is selected; when an FFT prior-coding module finishes decoding the last OFDM symbol of the channel to be decoded, a master control module starts a counter of an electricity-saving control module, closes clocks of other modules in the FFT prior-coding module and configures a tuner and ADC to be in an electricity-saving mode; and the master control module calculates the number of clock cycles needing stopping according to the next time slot number to be decoded, the next sampling rate, sampling clock offset, and the like and starts gate control clocks of the receiver or switches of the tuner and the ADC only when needing to transmit a channel to be received. The invention separates the gate control clocks of all the modules of the receiver, closes the gate control clocks of all the modules, the tuner and the ADC by stages and uses a simple counter to start the gate control clocks, the tuner and the ADC of the receiver by the stages to further decrease the energy consumption of the receiver.

Owner:FUZHOU ROCKCHIP SEMICON

Apparatus and methods for estimating and compensating sampling clock offset

ActiveUS7843806B2Reduce complexityImprove anti-interference abilitySecret communicationMulti-frequency code systemsPhase shiftedClock recovery

An apparatus for sampling clock recovery (SCO) and methods for estimating and compensating SCO are provided. The apparatus comprises a symbol timing adjustment module for shifting forward or backward symbol timing of the transmitted OFDM symbols; a discrete Fourier transform (DFT) processor for performing DFT to an output from the symbol timing adjustment module; a channel estimator for undertaking a channel frequency response estimation based on a channel estimation sequence; a SCO phase rotator for receiving and performing phase shift on the transmitted OFDM symbols of a frame header and a frame payload; an SCO estimation stage for undertaking an SCO estimation based on a pilot-subcarrier-related output of the SCO phase rotator and the CFR estimation; and an SCO compensation distributor for dividing the SCO estimation into integer and fractional portions and then distributing them into the symbol timing adjustment module and the SCO phase rotator, respectively.

Owner:WIPRO LTD

Apparatus and method for tracking a sampling clock of multi-carrier communication system

ActiveUS20060198481A1Amplitude-modulated carrier systemsSecret communicationCommunications systemPhase shifted

An apparatus and a method for tracking a sampling clock of a multi-carrier communication system are disclosed, the apparatus including a data removal module, a phase estimation module, and a sampling clock offset computation module. The data removal module is for generating a plurality of first and second data removal symbols by removing predetermined transmitted data from a plurality of first and second received symbols, respectively. The phase estimation module for generating a first and a second phase shifts according to correlations of the plurality of first and second data removal symbols. The sampling clock offset computation module for generating a control signal utilized to compensate the sampling clock of a plurality of received symbols according to the first and a second phase shifts.

Owner:REALTEK SEMICON CORP

Compensating devices and methods for detecting and compensating for sampling clock offset

ActiveUS8761326B2Amplitude-modulated carrier systemsAmplitude demodulationTime domainCorrelation coefficient

Owner:MEDIATEK INC

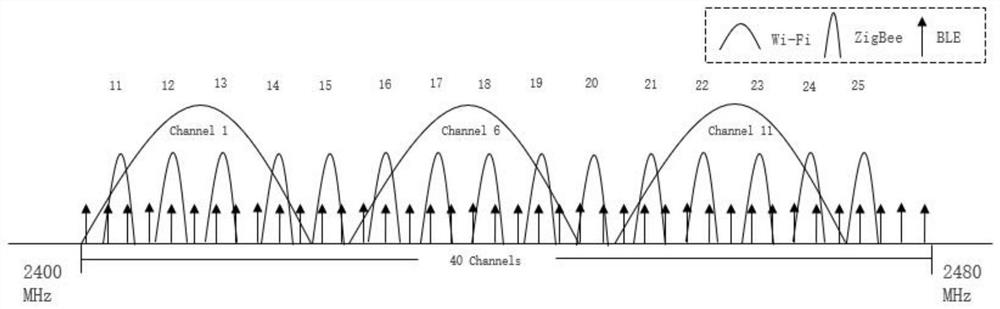

ZigBee-Bluetooth communication implementation method

ActiveCN113765929AImplement a fault-tolerant mechanismLow degree of modificationSynchronisation error correctionWireless communicationTransmission technologyEngineering

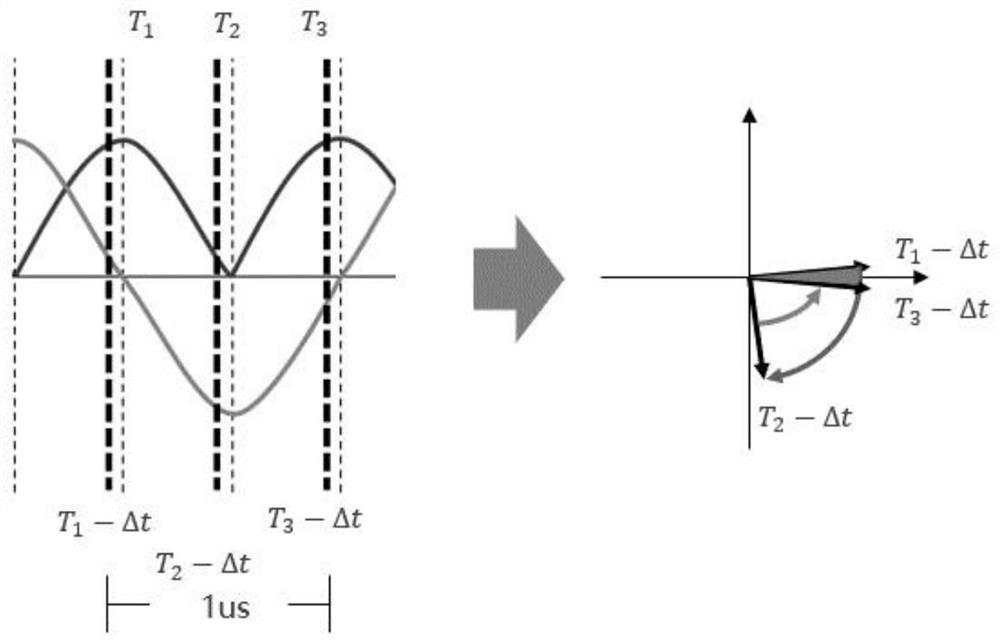

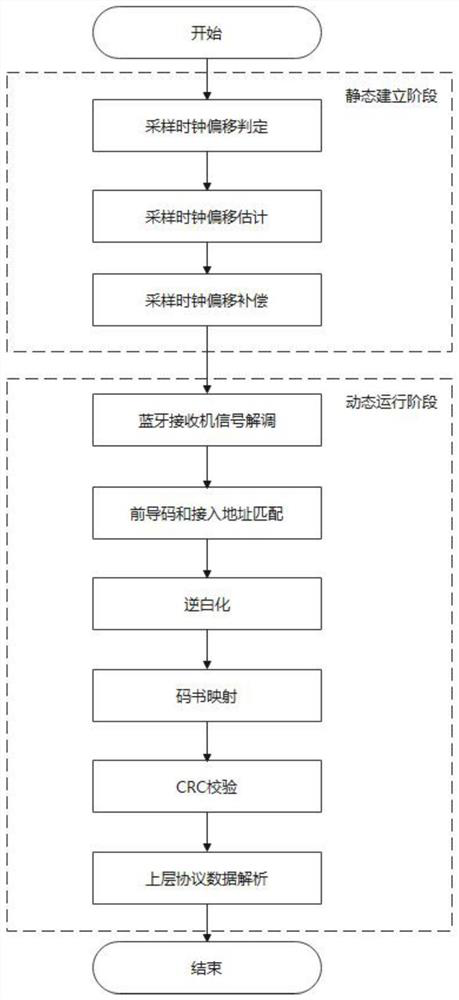

The invention relates to the technical field of digital information transmission, and discloses a ZigBee-Bluetooth communication implementation method, which comprises the following steps of: step 1, judging sampling clock skew and estimating the sampling clock skew; step 2, sampling clock offset compensation; step 3, matching the lead code with the access address; step 4, processing received data; and step 5, processing the effective load information by the Bluetooth upper layer protocol. On the premise that communication between Bluetooth is compatible, cross-protocol communication of the Bluetooth receiver to ZigBee-Bluetooth is achieved, and compatibility of a Bluetooth upper-layer protocol and a fault-tolerant mechanism of cross-protocol communication are achieved through mechanisms such as codebook mapping and the like; reasonable sampling clock skew compensation is carried out according to sampling clock skew judgment and sampling clock skew estimation results, so that the modification degree of hardware of a receiving end is reduced; and due to the certainty of the sampling offset of the receiver, the calculation cost of the codebook mapping mechanism of the Bluetooth receiver is one fourth of that of cross decoding, and the receiving calculation cost and the matching cost of the Bluetooth receiver are greatly reduced.

Owner:NORTHWESTERN POLYTECHNICAL UNIV