Sampling clock synchronization method for orthogonal frequency division multiplexing (OFDM) system

A sampling clock and frequency deviation technology, applied in the field of communication, can solve problems such as subcarrier phase deflection, signal-to-noise ratio loss, slow symbol timing offset, etc., and achieve the effects of improving estimation accuracy, high accuracy, and avoiding delay effects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

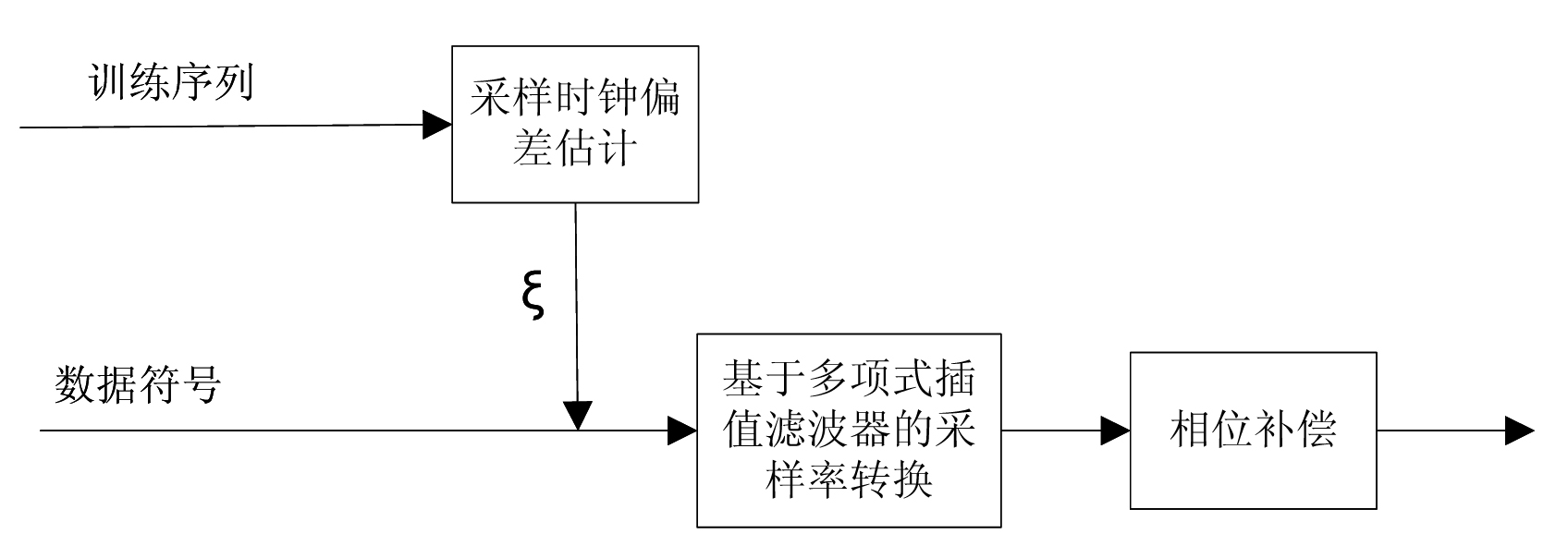

[0026] Embodiment 1, as figure 1 Shown: this embodiment adopts such as figure 1 The functional modules shown are: sampling clock frequency deviation estimation module, sampling rate conversion module based on polynomial interpolation filter, phase compensation module.

[0027] The first step uses two training sequences to estimate the frequency deviation of the sampling clock, and the estimation method is

[0028]

[0029] in is the symbol on each subcarrier after FFT and channel equalization of the received training sequence, is the pilot symbol on each subcarrier corresponding to the training sequence, is the OFDM symbol index, since there are only two training sequences, so Take 1 and 2, is the subcarrier number index, , and The value is

[0030]

[0031]

[0032] in .

[0033] find out after, by , find the sampling clock deviation , to get the final sampling clock deviation ,in , Respectively, the length of the FFT plus the length...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More