Method for monitoring chip groove depth and wafer

A technology for trench depth monitoring and chip monitoring. It is used in mechanical depth measurement, semiconductor/solid-state device components, semiconductor devices, etc., and can solve problems such as poor accuracy and large chip trench depth delay.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0023] Embodiments of the present invention will be described in detail below in conjunction with the accompanying drawings.

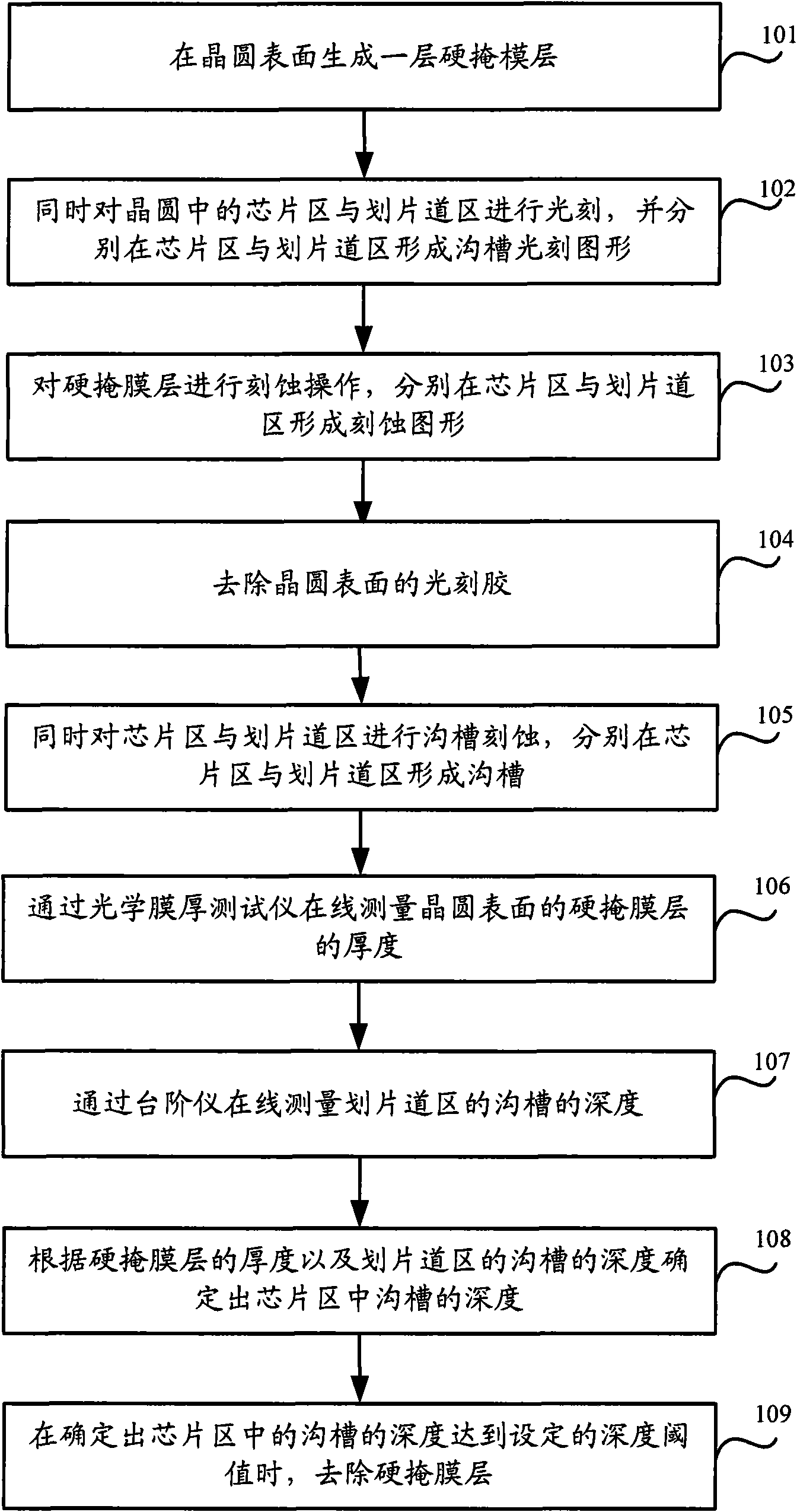

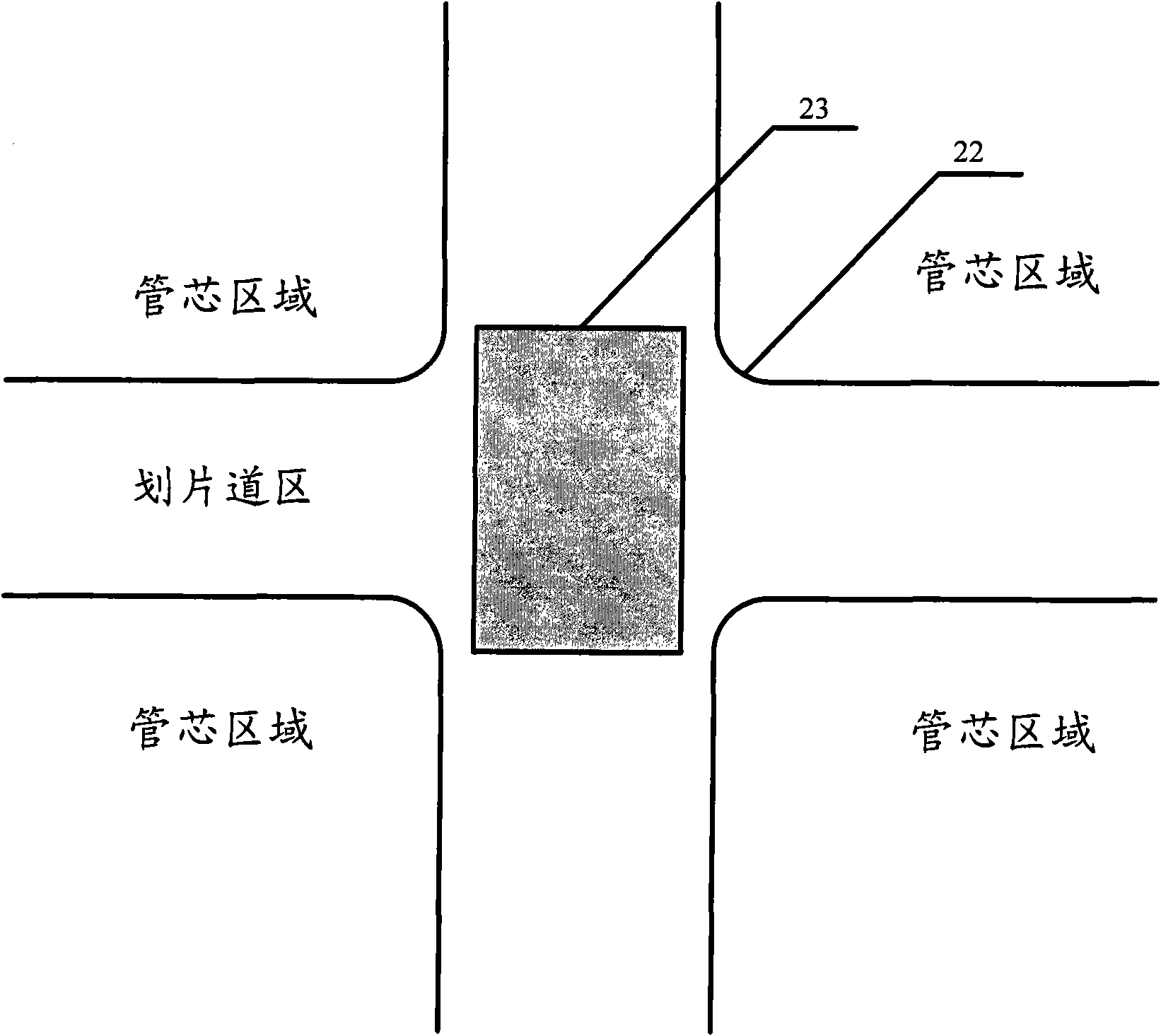

[0024] see figure 1 , is the flow chart of the method for realizing the real-time monitoring of the groove depth in the embodiment of the present invention. The module shaped as a cuboid (that is, the groove depth test module) is filled in the cross-staggered area of the wafer surface in advance. The polarity of the module is consistent with the chip area. The polarity of the trench photoresist layer is the same, and during the photolithography process, the cuboid module is a photolithography open area; the process includes the following steps:

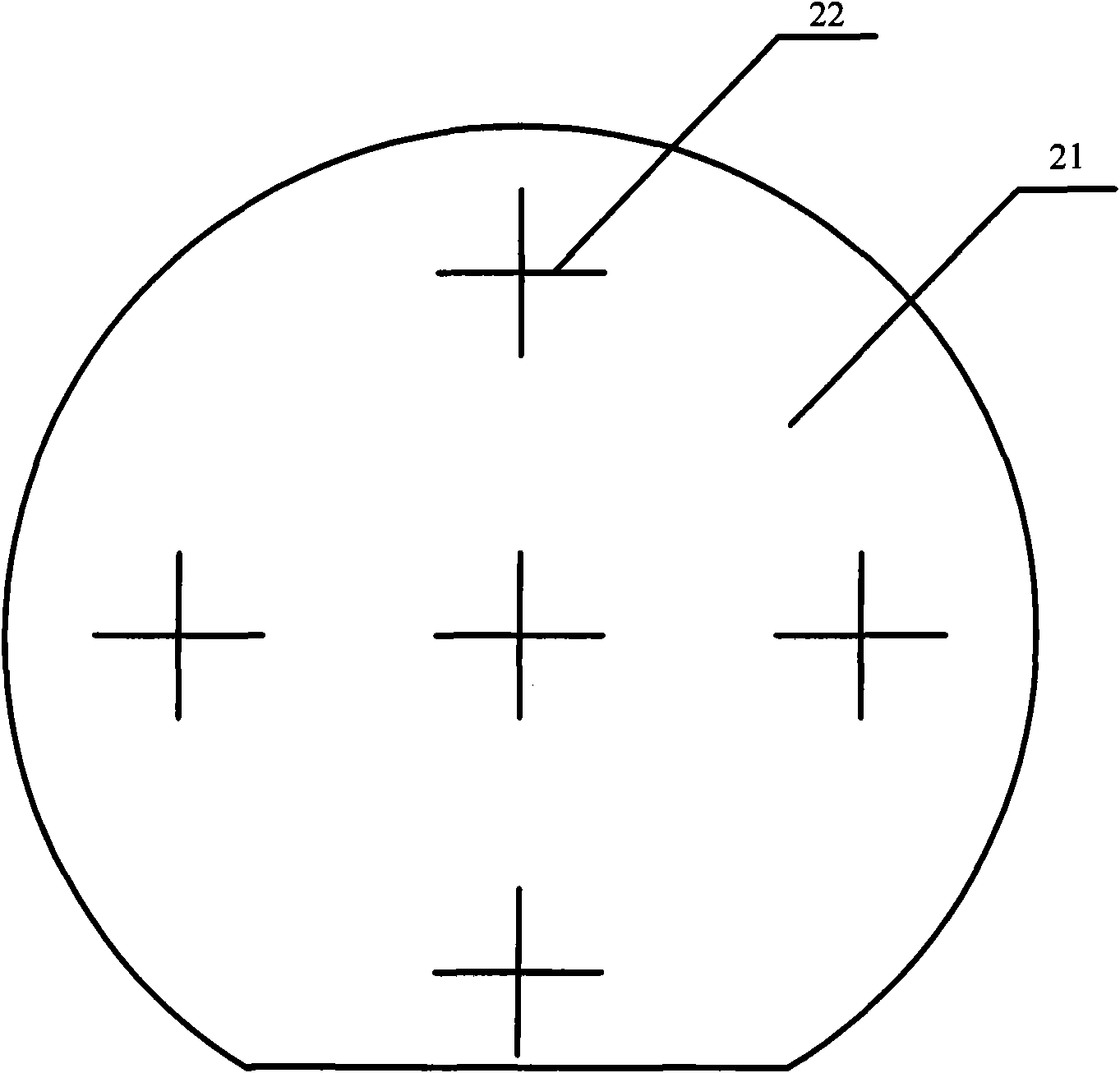

[0025] Step 101 , forming a protective film, such as a hard mask layer 31 , on the surface of the wafer 21 .

[0026] The structure of the wafer in this step is as follows Figure 2B As shown, is in the existing as Figure 2A All or part of the criss-cross region 22 of the wafer 21 shown is filled with t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More