Groove type power MOSFET (Metal-Oxide-Semiconductor Field Effect Transistor) device

A device and power technology, applied in the field of semiconductor power devices and radio frequency power devices, can solve problems such as the inability to completely eliminate capacitance, and achieve the effects of eliminating epitaxial line inductance, reducing gate charge, and increasing carrier concentration

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

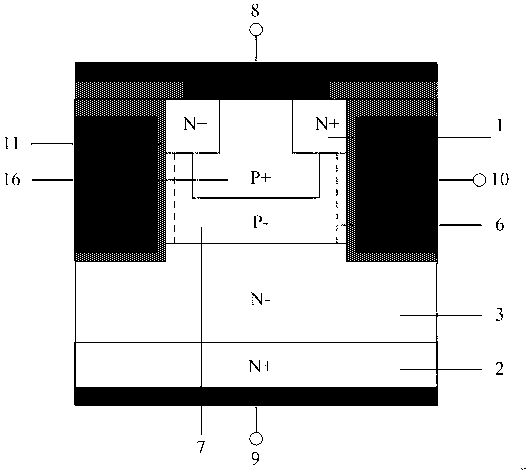

[0044] Taking N-channel devices as an example, the present invention is as Figure 4 shown, including N + Source area 1, N + Drain region 2, lightly doped drain region 3, N + Slot 4, N + Source contact region 5, channel region 6, P well region 7, source electrode 8, drain electrode 9, gate electrode 10, gate oxide 11, field oxide 12, surface source metal field plate 13, isolation oxide 14, P - Substrate 15.

[0045] Preferably, the thickness of the field oxide 12 should be controlled between 100nm~500nm. The thicker the field oxide, the weaker the effect of the source metal field plate, and the less obvious the effect of assisting the depletion of the lightly doped drain region. The field oxide should not be too thin to prevent parasitic channels on the silicon surface.

[0046] The slot-type power MOSFET devices mentioned above can also not be made of N + source region 1, its N + Groove area 4 is directly used as groove type N + Source region 4, forming a power MOSF...

Embodiment 2

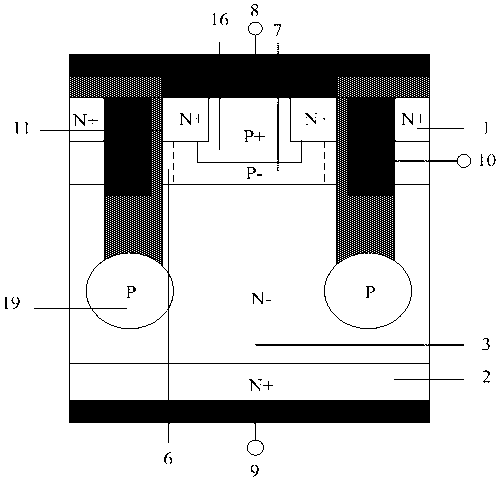

[0071] Figure 4~Figure 7 as well as Figure 12 , Figure 13 The grooved power MOSFET device, its N channel can also be made into a P channel, forming a P channel grooved power MOSFET device, and the device structure is as follows Figure 14 shown. The conductivity type of all semiconductor regions of a P-channel trench power MOSFET device should be opposite to that of an N-channel trench power MOSFET device.

Embodiment 3

[0073] The manufacturing process of the present invention is similar to the conventional LDMOS manufacturing process, and the following points need to be noted:

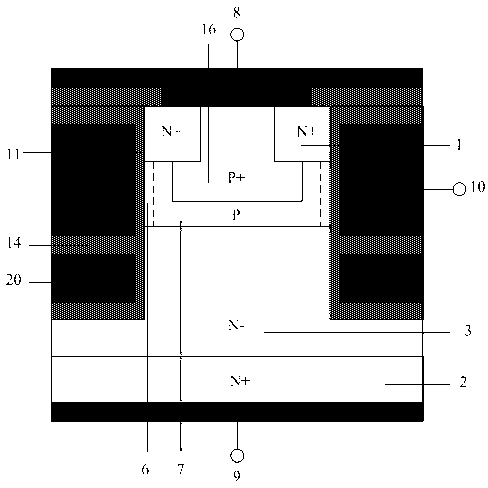

[0074] 1.P + The approach in the contact area: doing a good job in P - well contact area P + 1 Finally, a gap must be left for the next step of high-concentration P + injection to form P + 2 area, the surface metal covering will be P + 2 area and N + The source region is connected thus ensuring that the P - well area and N + The source region is equipotential. The device cross-section of this embodiment is shown in Figure 10(a), and the device layout is shown in Figure 10(c), where no surface metal coverage is shown. If P + 2 If the region adopts the scheme shown in Figure 10(b), it needs to be formed by ion implantation on the back side, and a gap needs to be left when making the source contact area on the back side, and the position of the gap is still the same as that shown in Figure 10(c).

[0075] ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More