Digital pll circuit and communication apparatus

A circuit and digital technology, applied in the field of communication devices, can solve the problems of higher design difficulty, higher power consumption, and difficulty in reducing the area, and achieve the effect of good phase noise characteristics and low power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment approach 1

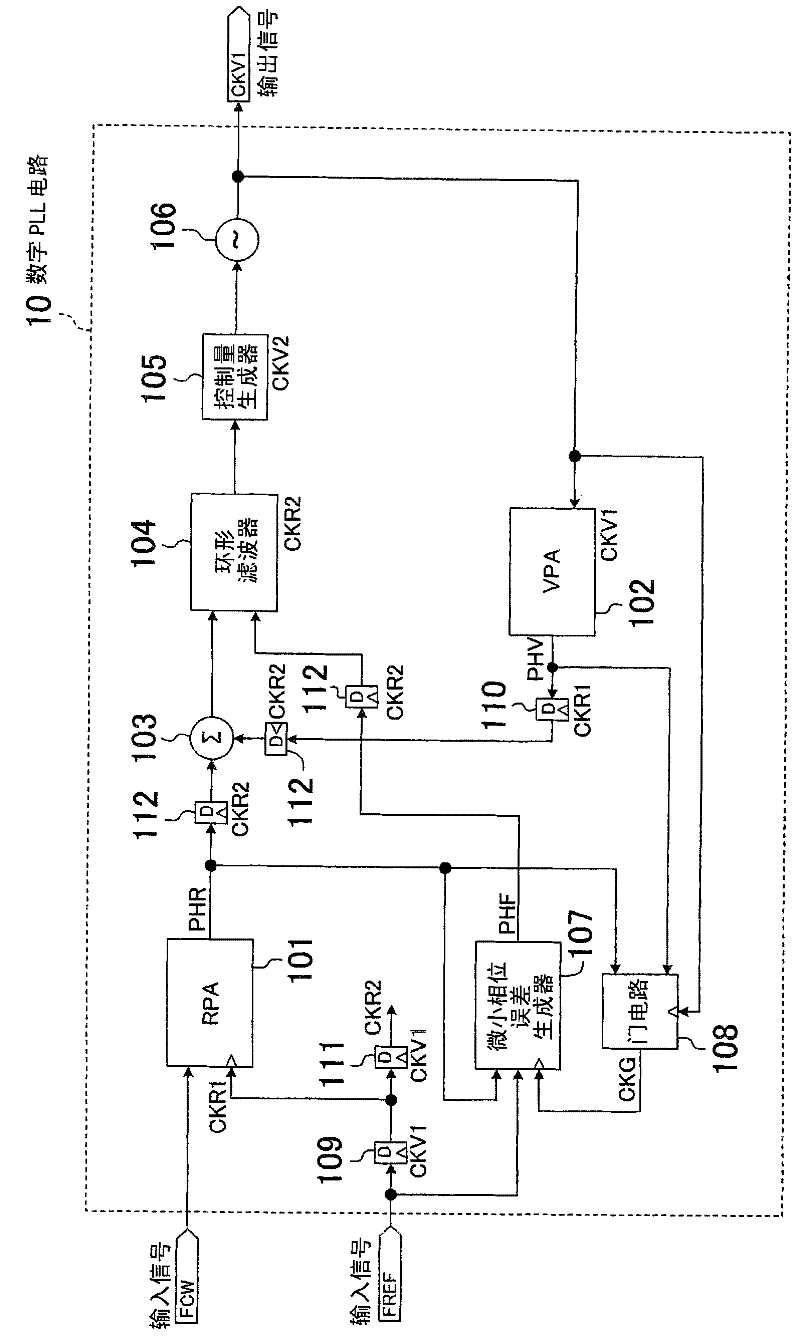

[0061] figure 1 The configuration of the digital PLL circuit according to the first embodiment of the present invention is shown.

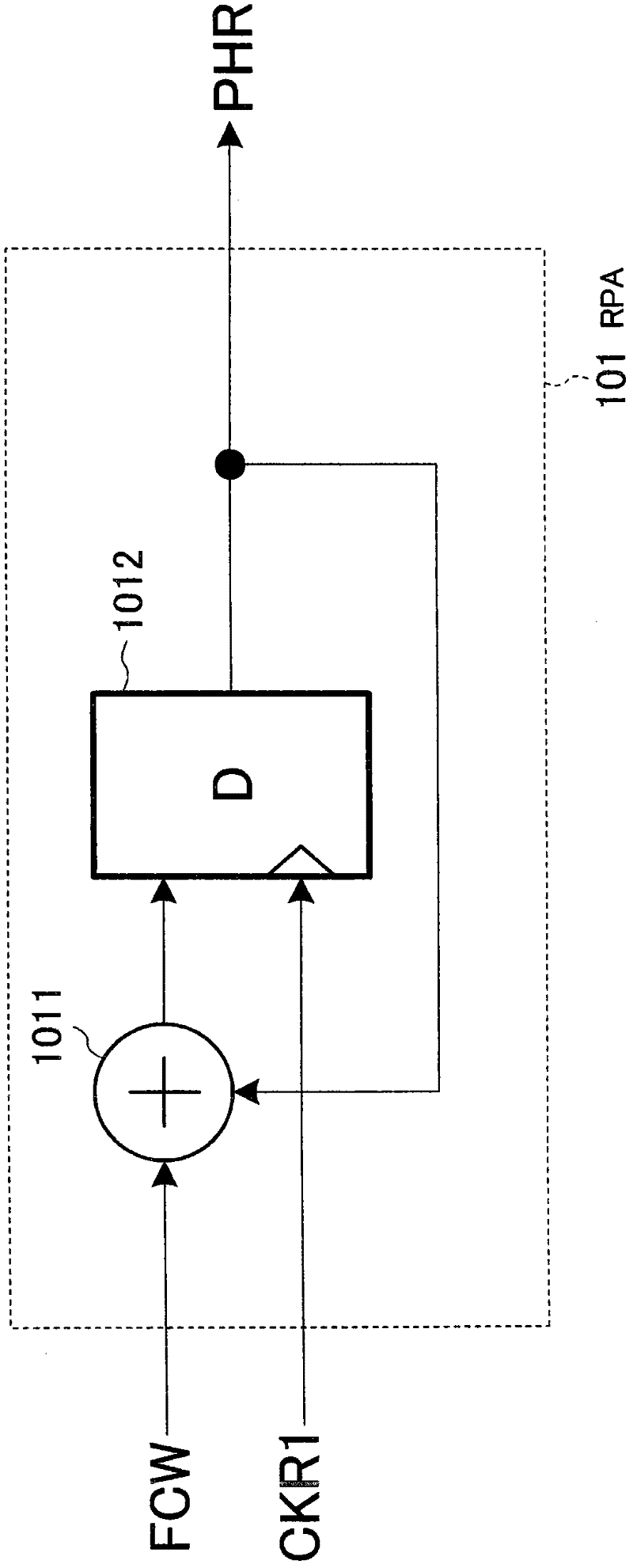

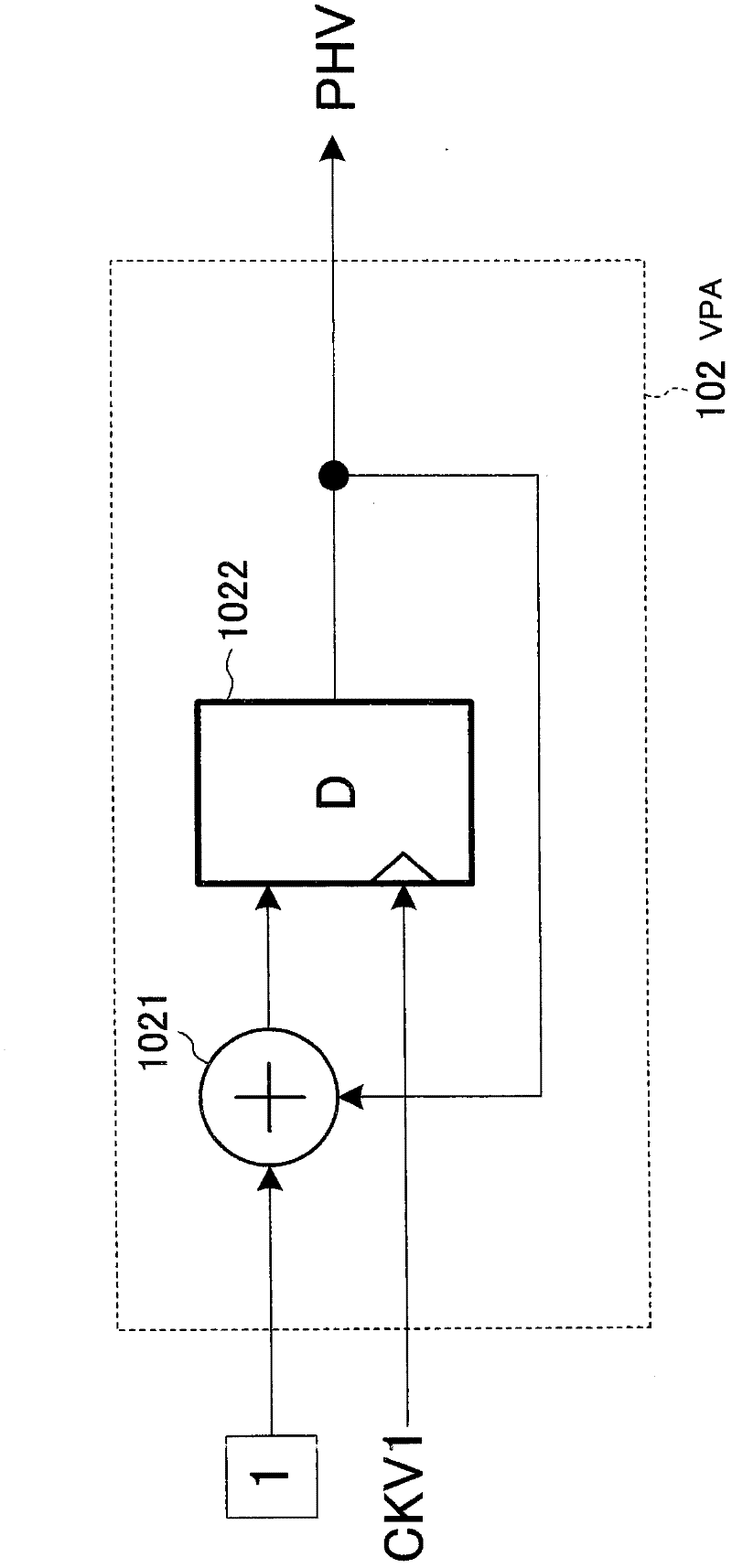

[0062] exist figure 1 Among them, 101 is the RPA circuit (Reference Phase Accumulator: reference phase calculator), 102 is the VPA circuit (Variable Phase Accumulator: variable phase calculator), 103 is the phase comparator (comparator), 104 is the phase error of the input 106 is a control oscillator, 105 is a control quantity generator that controls the control oscillator 106, 107 is a small phase error generator, and 108 is a small phase error generator. 109 is a gate circuit that generates a signal CKR1 that retimes the reference signal FREF in synchronization with the output clock CKV1, and 110 is a register circuit that operates in synchronization with the retiming signal CKR1. 111 is a register circuit that generates a signal CKR2 delayed by one clock from the retiming signal CKR1 , and 112 is a register circuit that operates in synchron...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More