Patents

Literature

41results about How to "Limited number" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

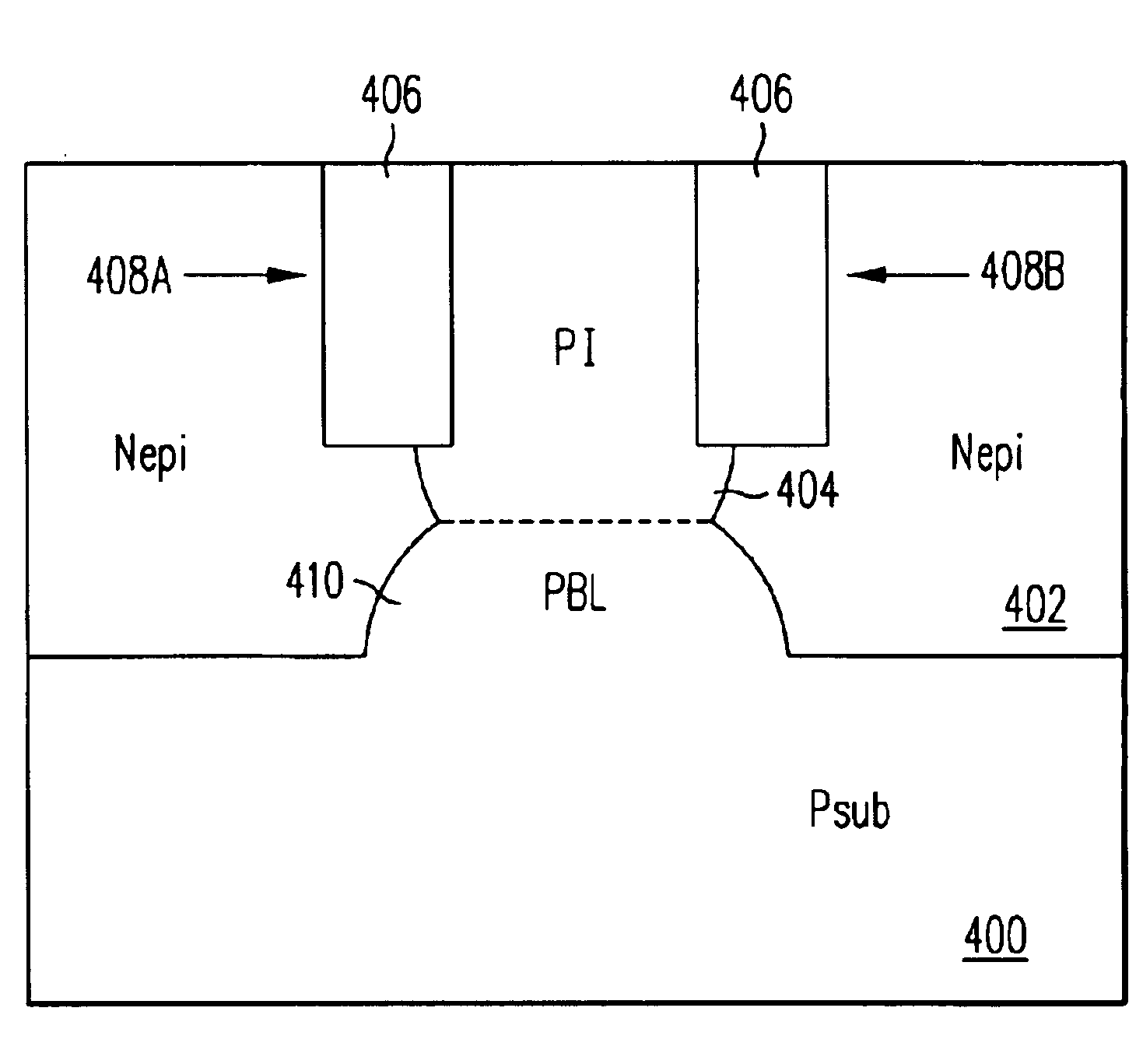

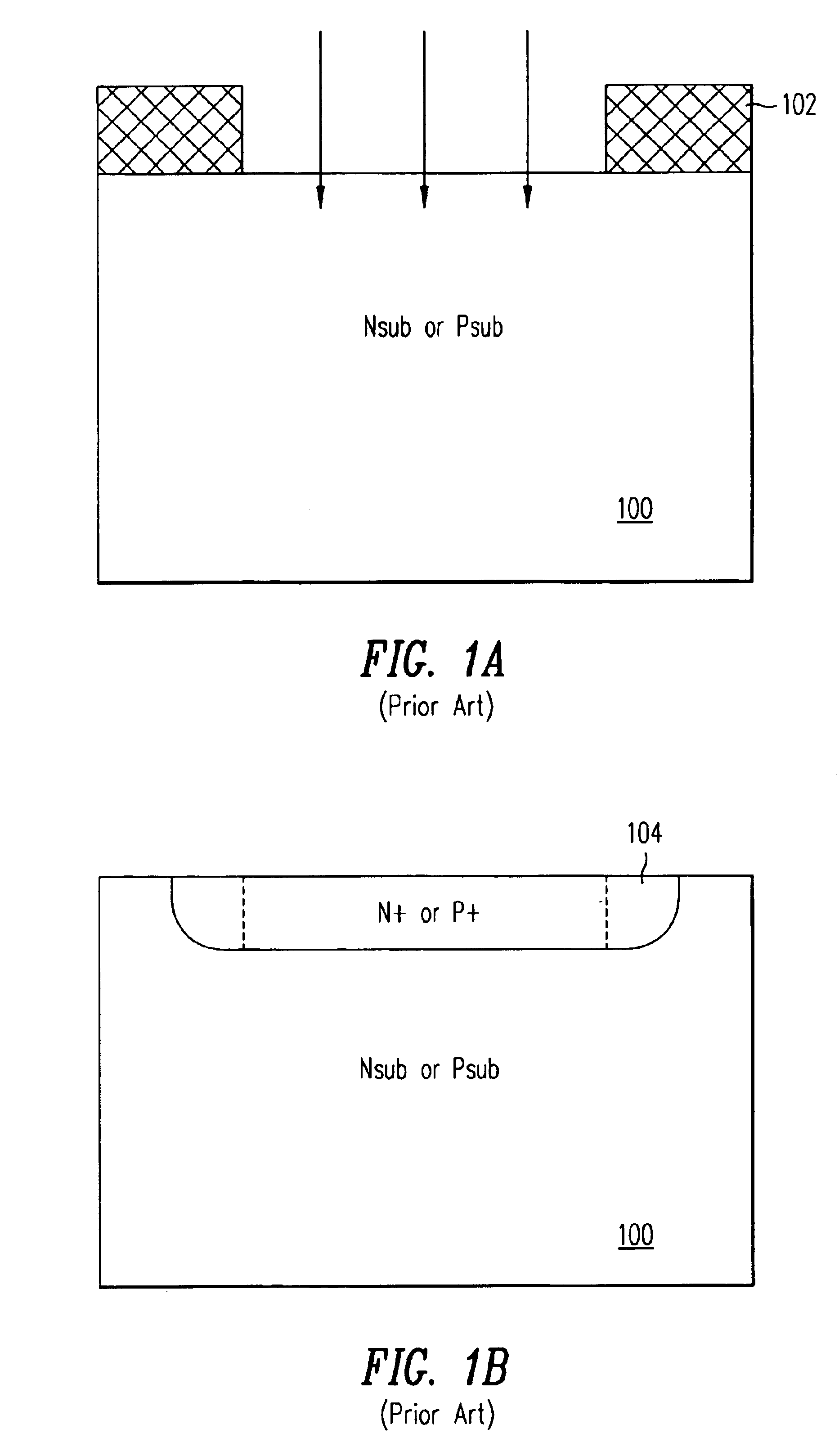

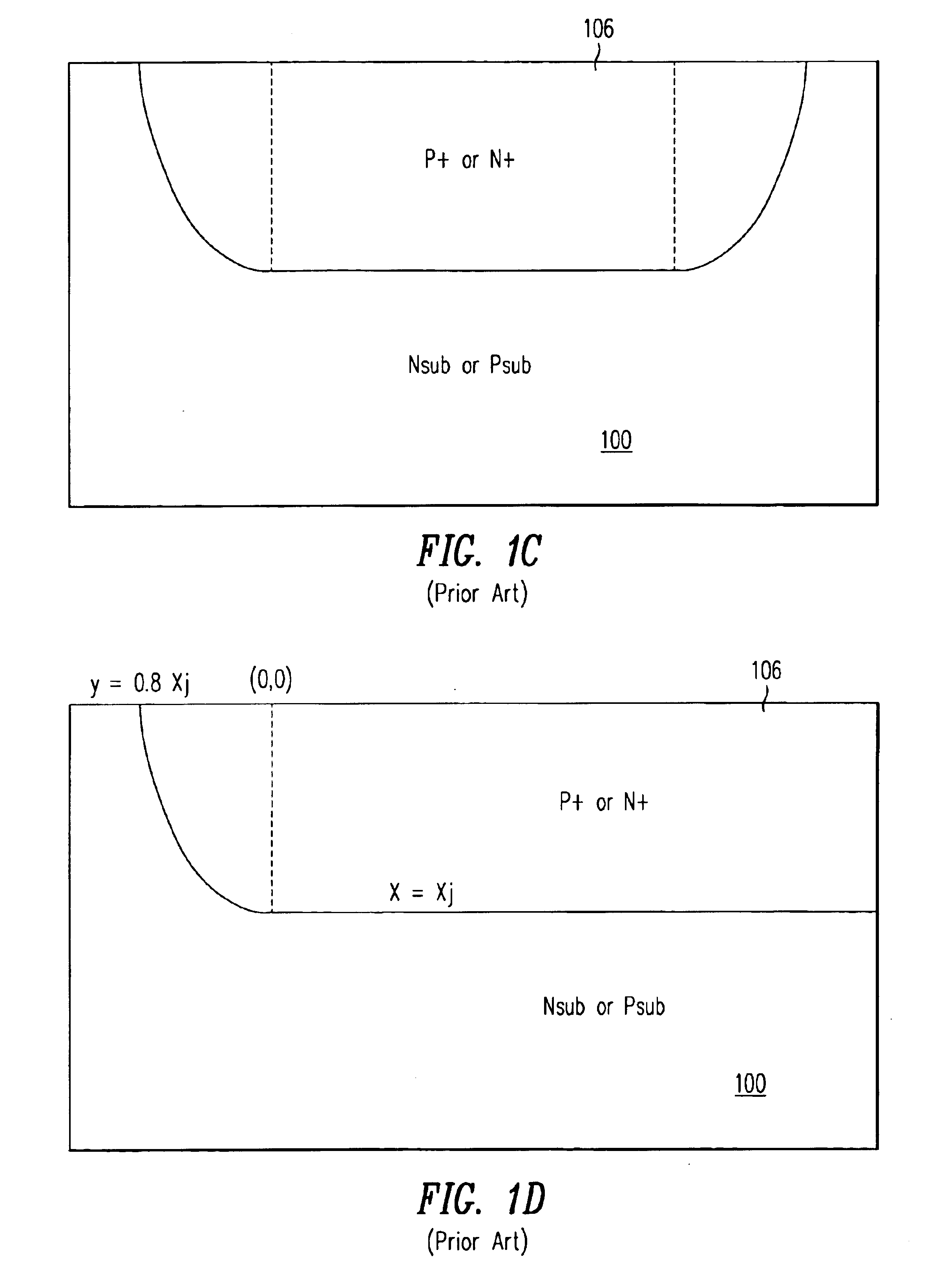

Complementary analog bipolar transistors with trench-constrained isolation diffusion

InactiveUS6943426B2Substantial thermal budgetLimited numberTransistorSemiconductor/solid-state device detailsHigh energyEngineering

A semiconductor substrate includes a pair of trenches filled with a dielectric material. Dopant introduced into the mesa between the trenches is limited from diffusing laterally when the substrate is subjected to thermal processing. Therefore, semiconductor devices can be spaced more closely together on the substrate, and the packing density of the devices can be increased. Also trench constrained doped region diffuse faster and deeper than unconstrained diffusions, thereby reducing the time and temperature needed to complete a desired depth diffusion. The technique may be used for semiconductor devices such as bipolar transistors as well as isolation regions that electrically isolate the devices from each other. In one group of embodiments, a buried layer is formed at an interface between an epitaxial layer and a substrate, at a location generally below the dopant in the mesa. When the substrate is subjected to thermal processing, the buried layer diffuses upward, the dopant in the mesa diffuses downward until the two dopants merge to form an isolation region or a sinker extending downward from the surface of the epitaxial layer to the buried layer. In another embodiment, dopant is implanted between dielectrically filled trenches at a high energy up to several MeV, then diffused, combining the benefits of deep implantation and trenched constrained diffusion to achive deep diffusions with a minimal thermal budget.

Owner:ADVANCED ANALOGIC TECHNOLOGIES INCORPORATED

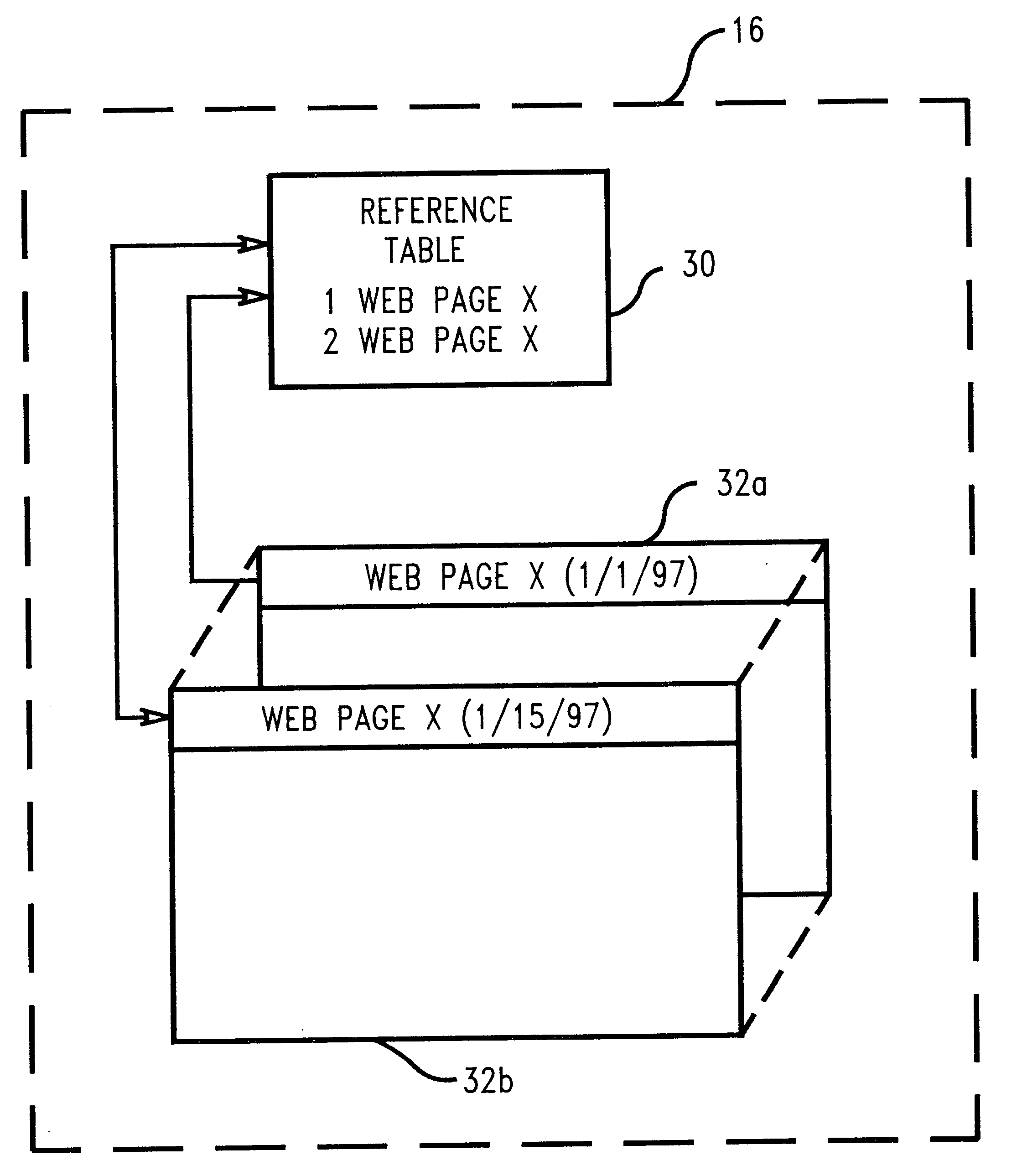

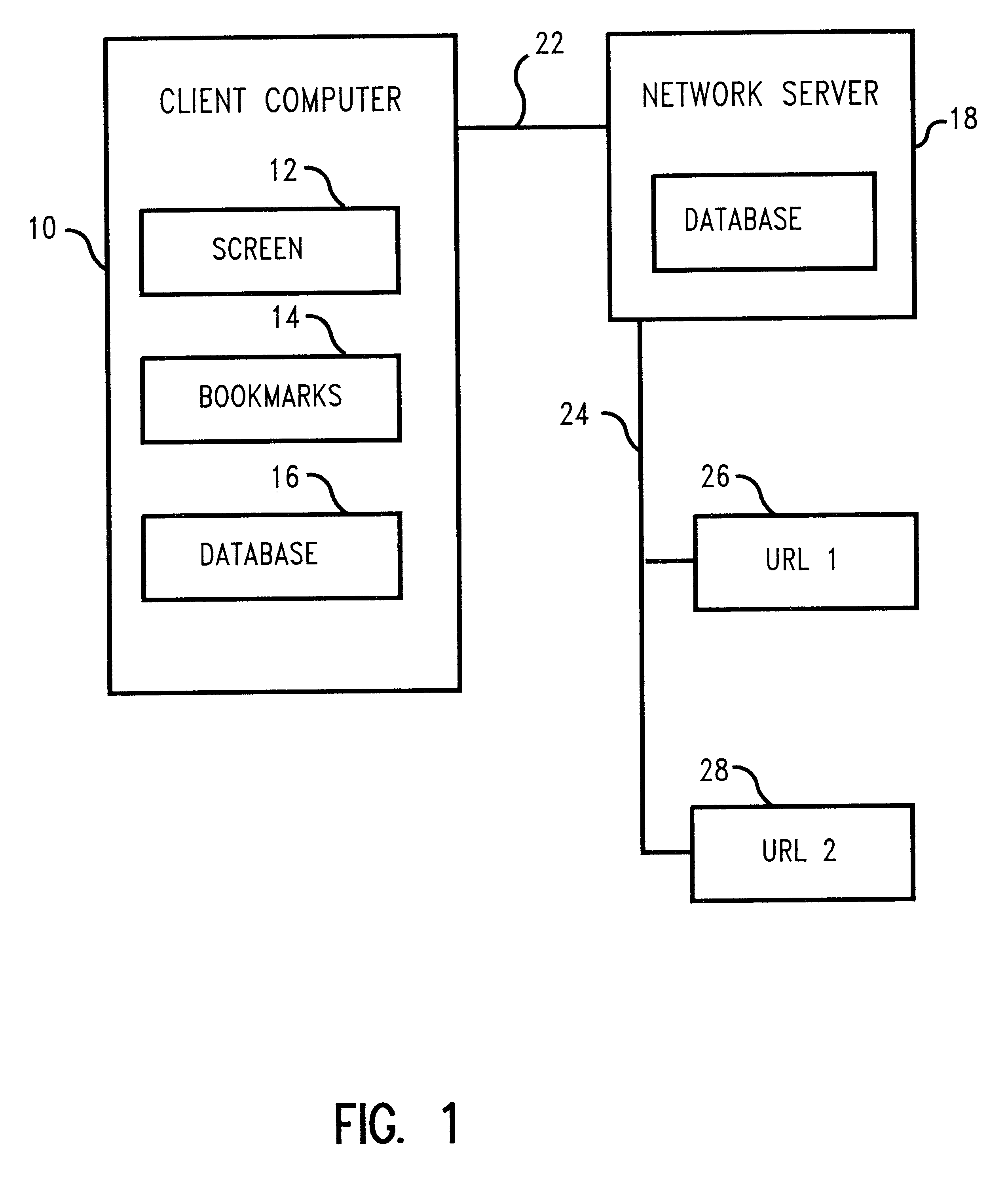

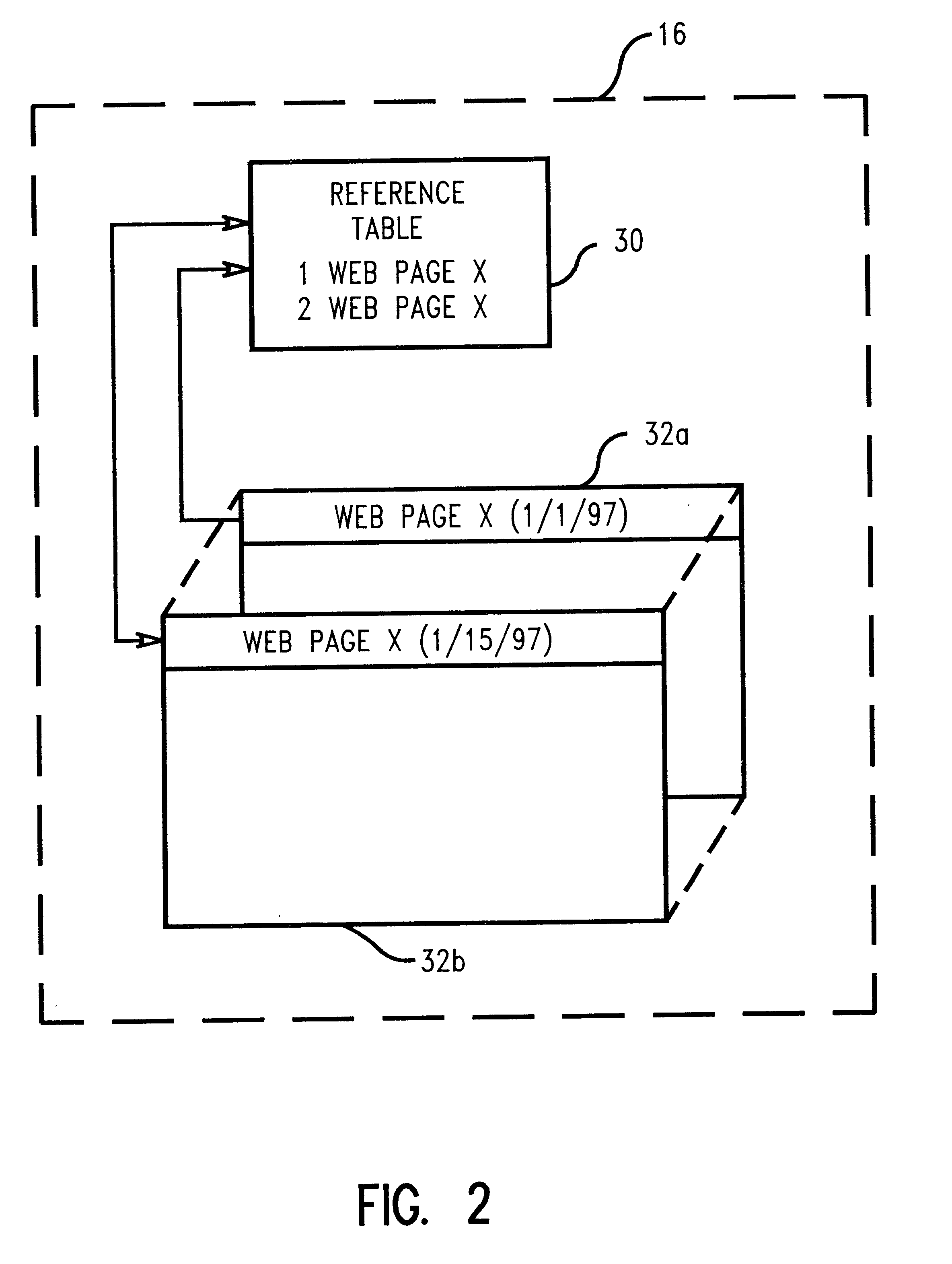

System for personal storage of different web source versions

InactiveUS6405223B1Limited numberReduce in quantityData processing applicationsWebsite content managementClient-sideJava code

A system for storing web pages accessed from an inter- or intra-net source. The system comprises a client computer program storage device having stored thereon a first version of a desired web page from an inter- or intra-net source having assigned thereto a first version number and a second version of the desired web page from an inter- or intra-net source having assigned thereto a second version number. The storage device also includes a reference table which includes the first and second version numbers, such that the desired web page version may be accessed and viewed by the client computer by reference to the version numbers. The version numbers include designators of different files within the web page and designators of the version of the web page. Each of the stored web pages may include information such as a HTML source file for the web page, graphics imbedded in the HTML source file, javascript code, Java code and any other code referenced by the HTML source file. The client computer storage device may include a web browser having a bookmark file for storage of URL addresses of a plurality of web pages including the desired web page. The bookmark file is operable in conjunction with the reference table by the web browser to identify and access a selected version of the web pages.

Owner:IBM CORP

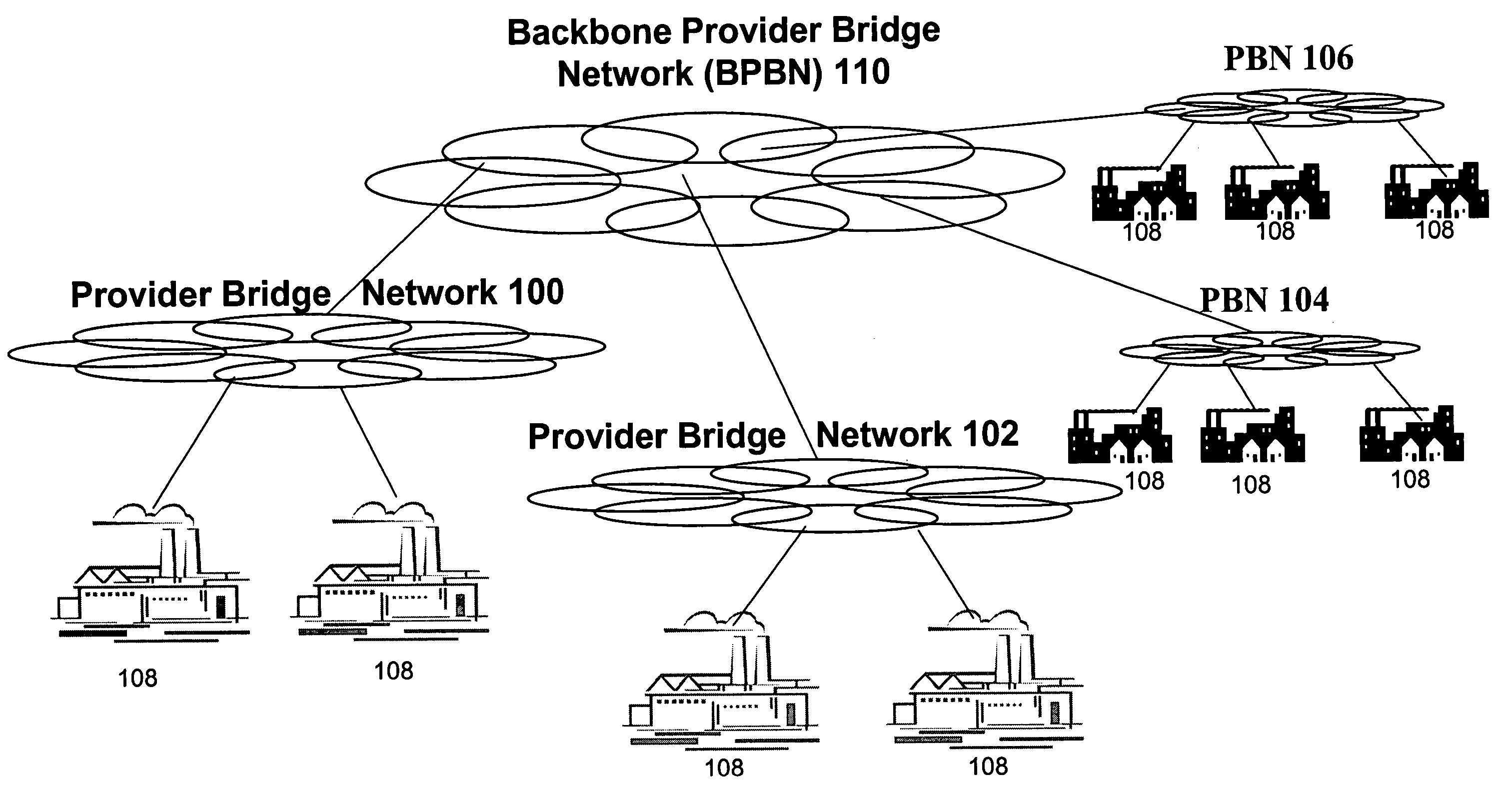

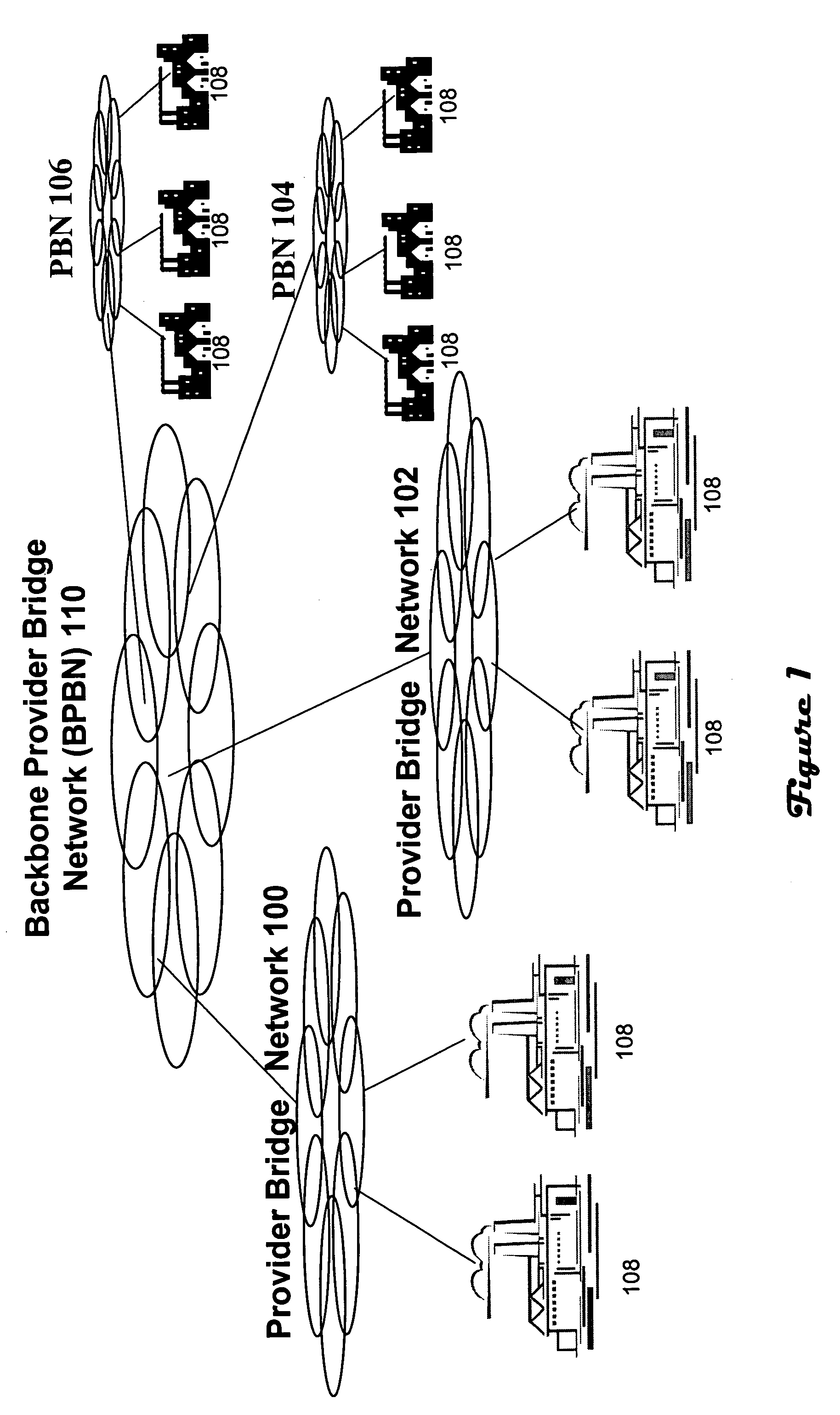

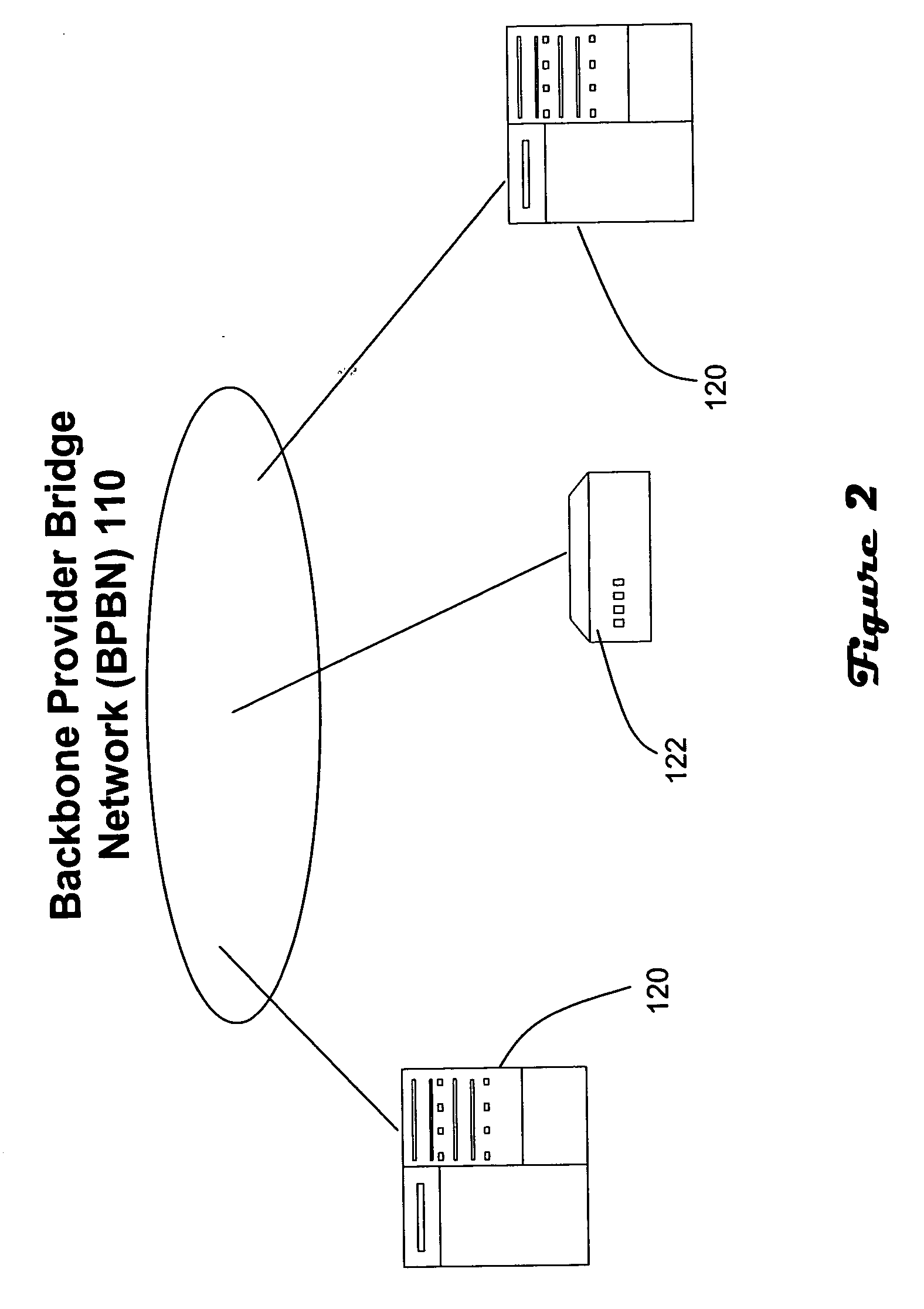

Backbone provider bridging networks

InactiveUS20050286541A1Limited numberImprove scalingTime-division multiplexNetworks interconnectionReal-time computingEncapsulated data

An edge device is used to support a backbone provider bridging network to facilitate interconnection of a plurality of networks. The edge device is coupled between the backbone and a first one of the networks, and is operable to encapsulate data units received from the first network with a header, and to forward the encapsulated data unit to the backbone. The header is indicative of a tunnel that is used to support traffic from the first network to a second network over the backbone. The edge device also de-encapsulates data units received from the backbone that are destined for the first network.

Owner:RPX CLEARINGHOUSE

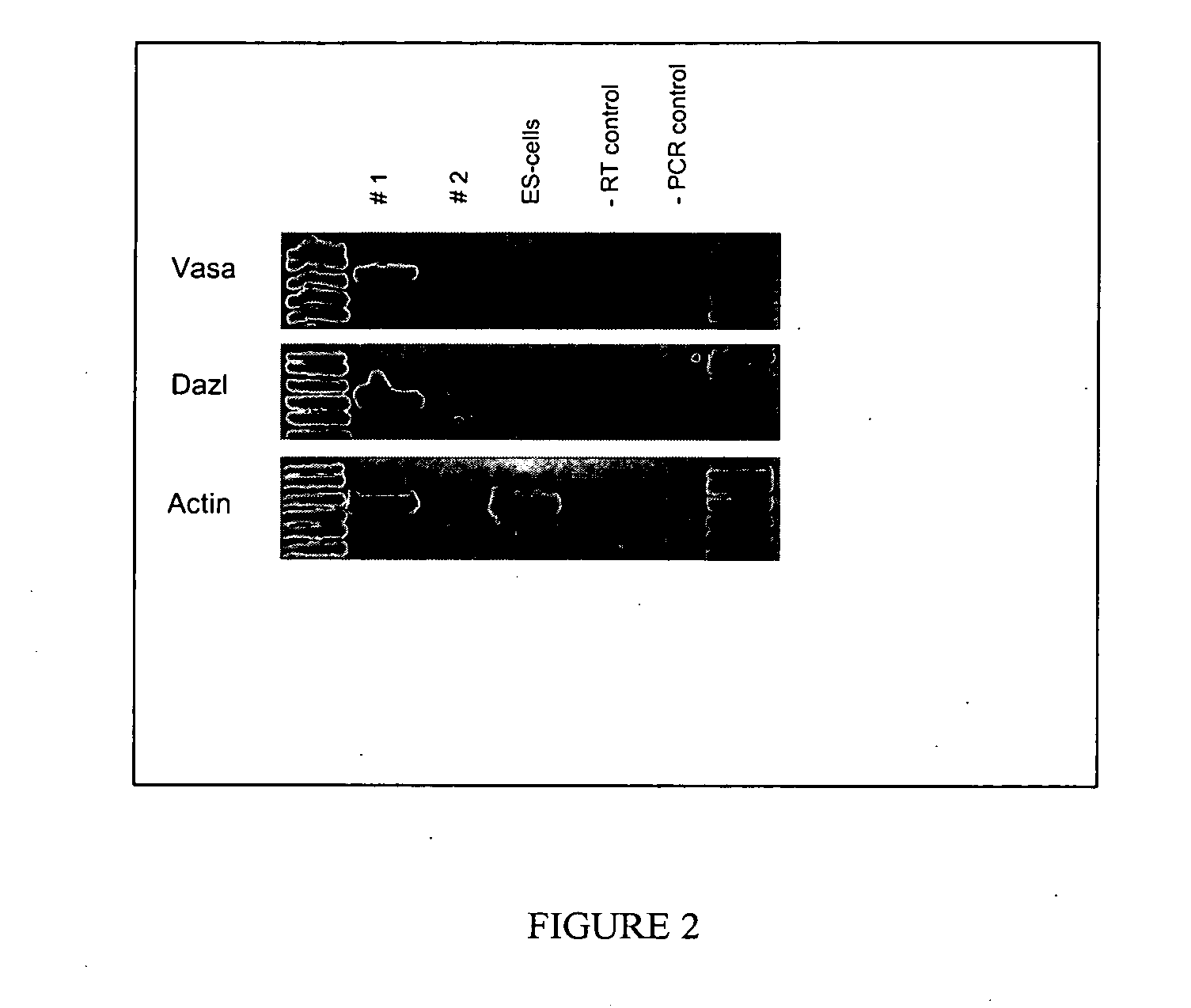

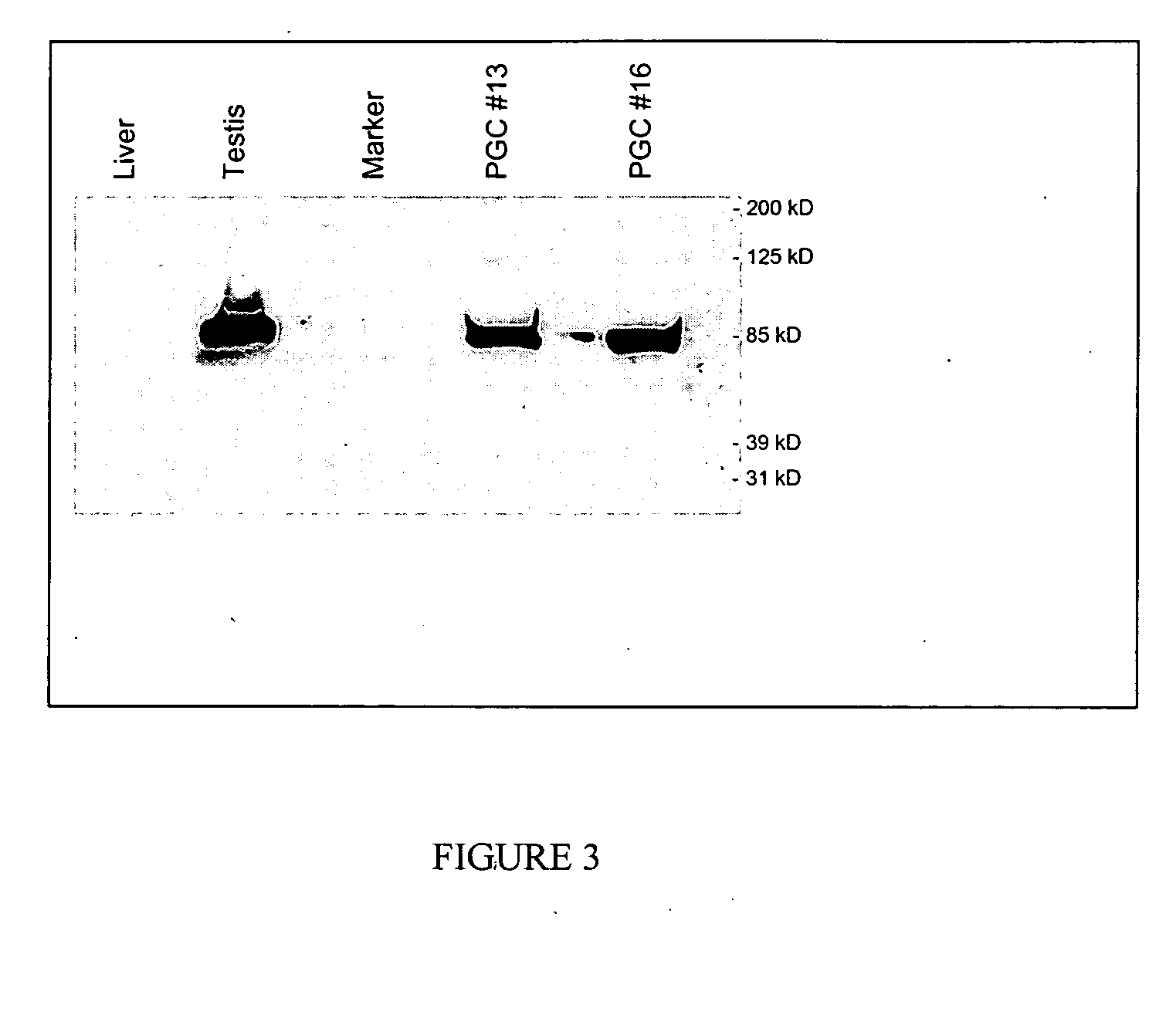

Transgenic chickens

The present invention is transgenic chickens obtained from long-term cultures of avian PGCs and techniques to produce and transgenic birds derived from prolonged PGC cultures. In some embodiments, these PGCs can be transfected with genetic constructs to modify the DNA of the PGC, specifically to introduce a transgene encoding an exogenous protein. When combined with a host avian embryo by known procedures, those modified PGCs are transmitted through the germline to yield transgenic offspring. This invention includes compositions comprising long-term cultures of PGCs that can be genetically modified by gene targeting, that can accept large amounts of foreign DNA and that contribute to the germline of recipient embryos.

Owner:ALEXION PHARM INC

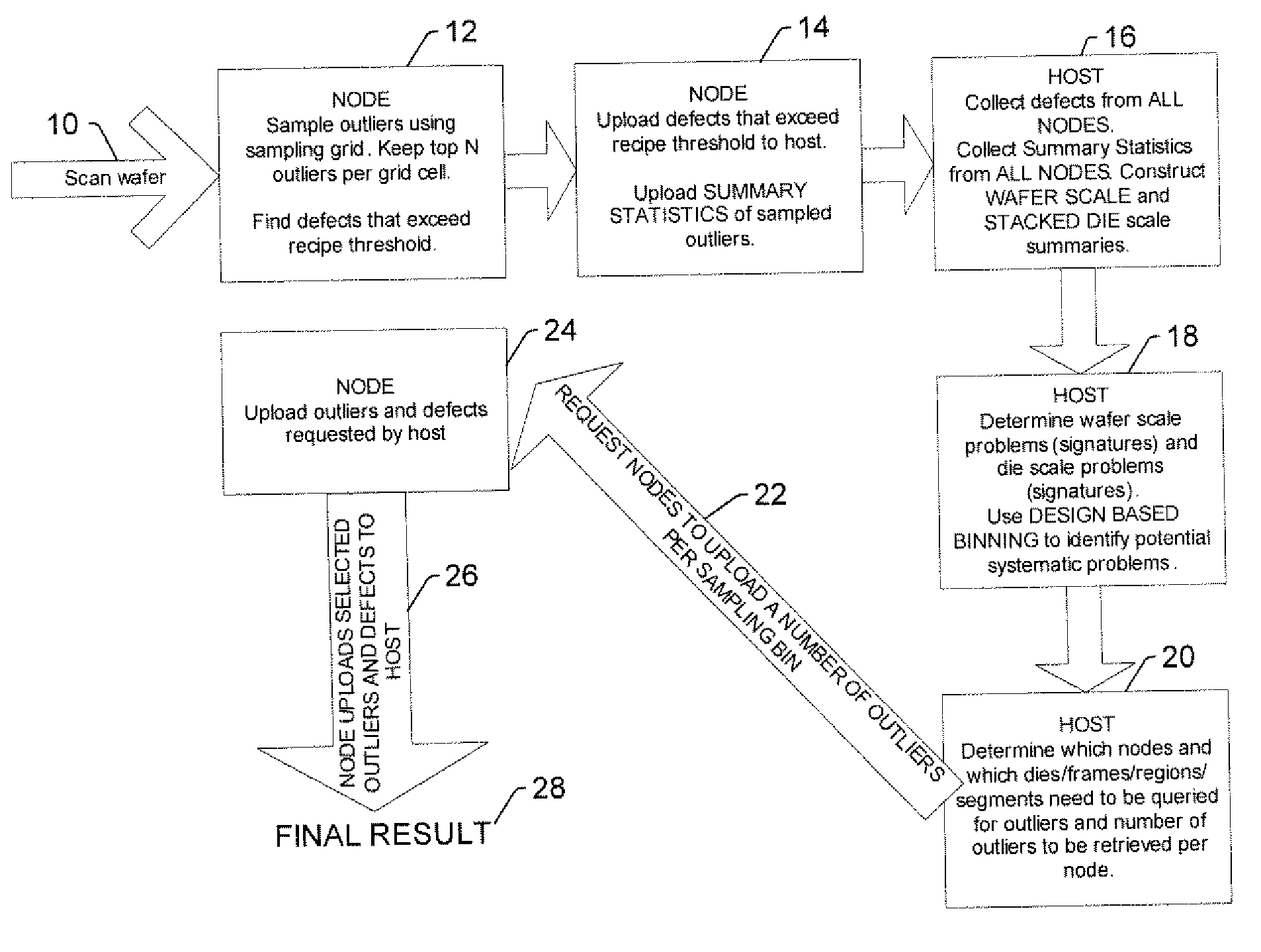

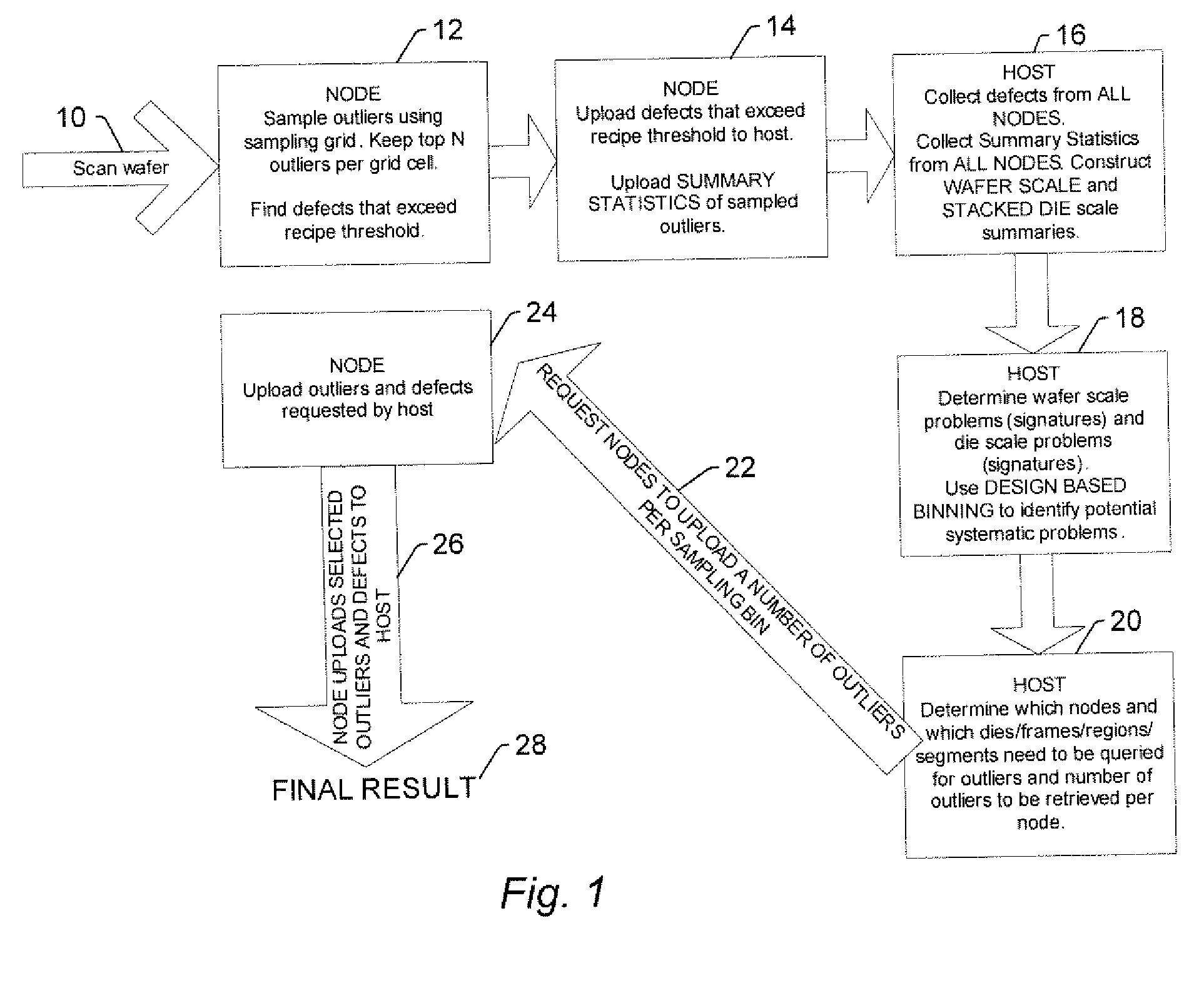

Systems and methods for detecting defects on a wafer and generating inspection results for the wafer

ActiveUS20090287440A1Limited numberProgramme controlSemiconductor/solid-state device testing/measurementOutlierElectrical and Electronics engineering

Systems and methods for detecting defects on a wafer and generating inspection results for the wafer are provided. One method includes detecting defects on a wafer by comparing output generated by scanning of the wafer performed by an inspection system to one or more defect detection thresholds. The method also includes sampling outliers in the output by selecting the output having the highest values from bins defined based on one or more predetermined criteria. In addition, the method includes selecting a portion of the sampled outliers based on wafer-level analysis of the sampled outliers. The method further includes generating inspection results for the wafer by combining information about the selected portion of the sampled outliers with information about the defects detected using the one or more defect detection thresholds.

Owner:KLA TENCOR CORP

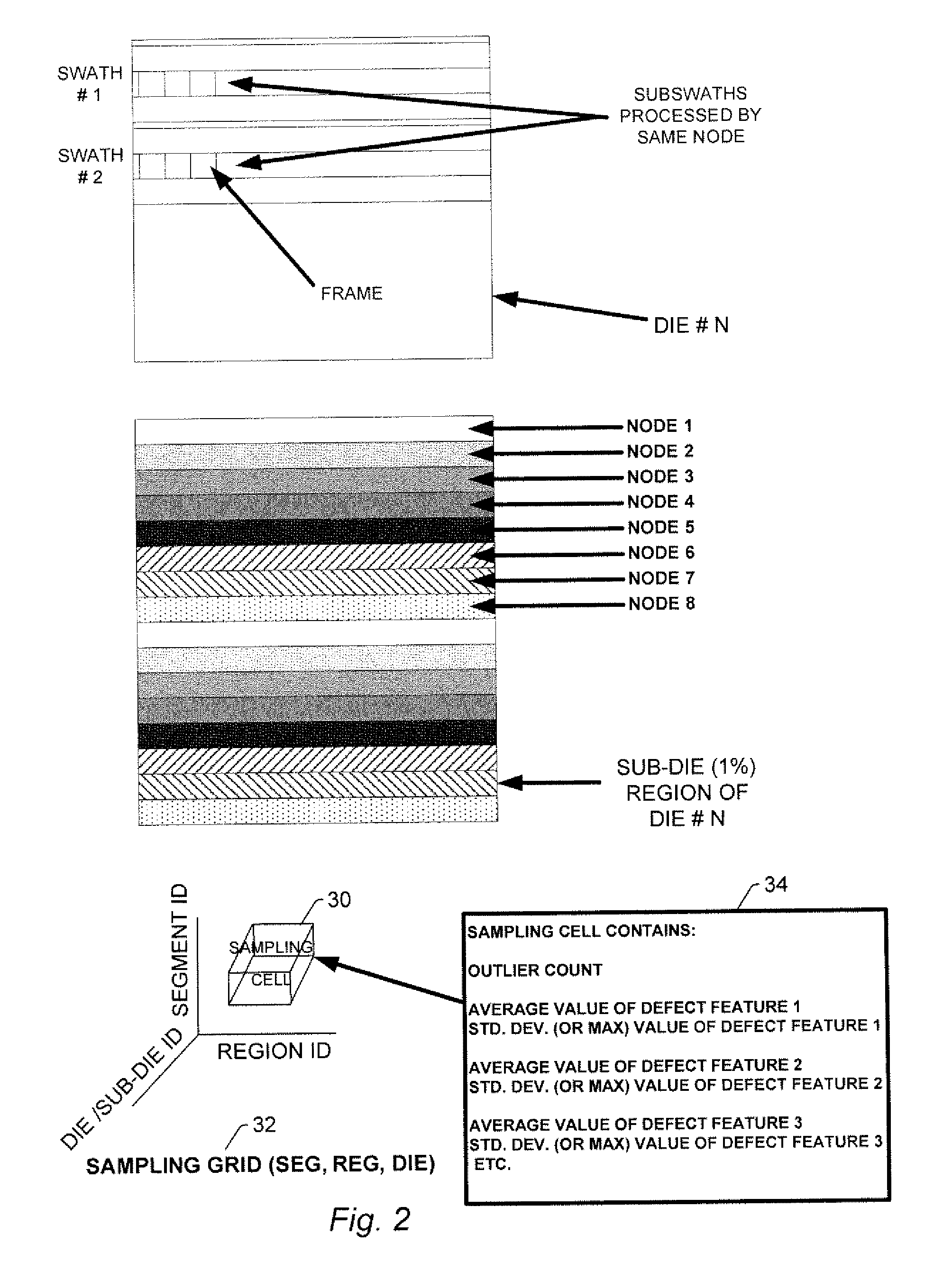

Arbitrary shaping of temporal noise envelope without side-information

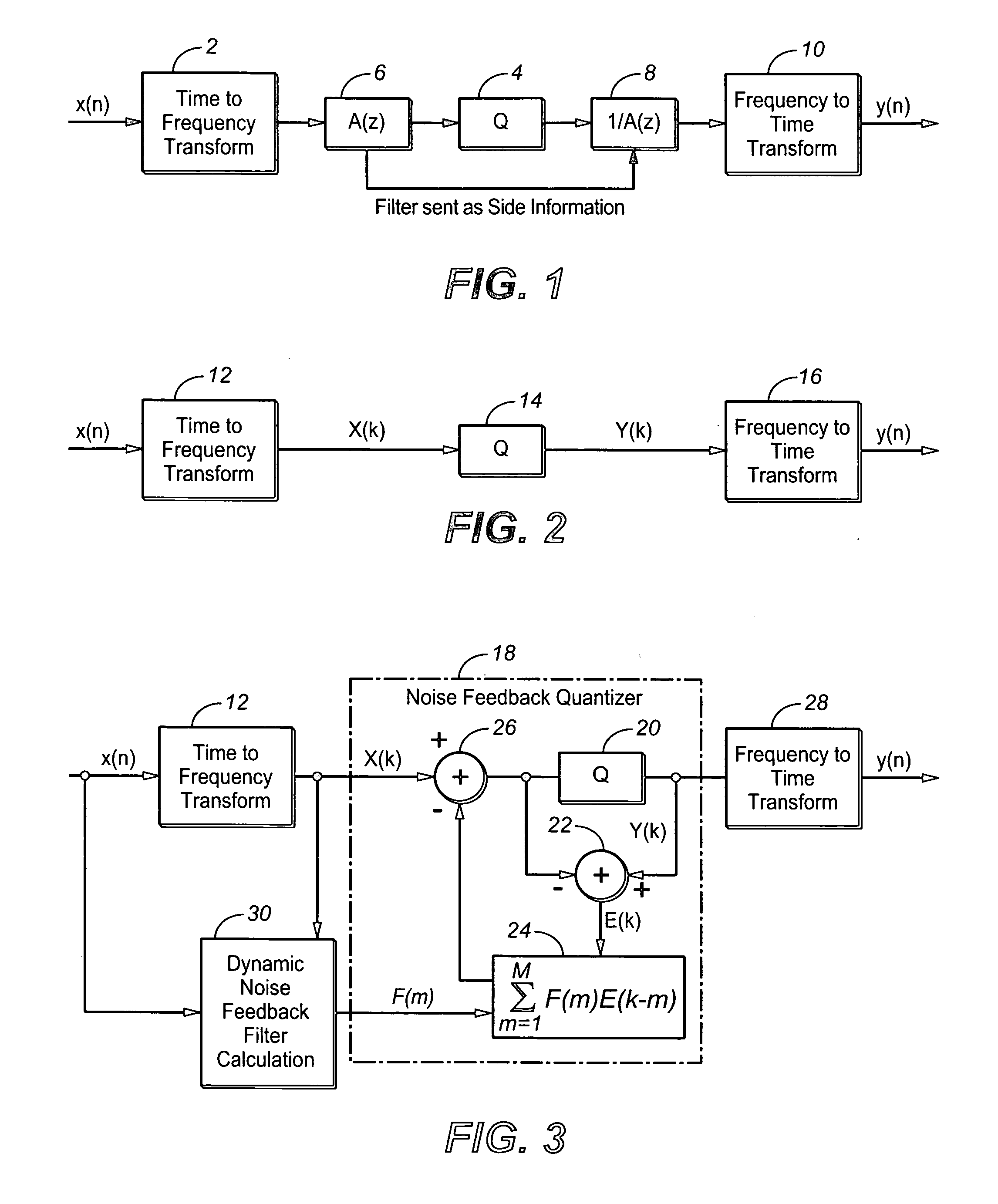

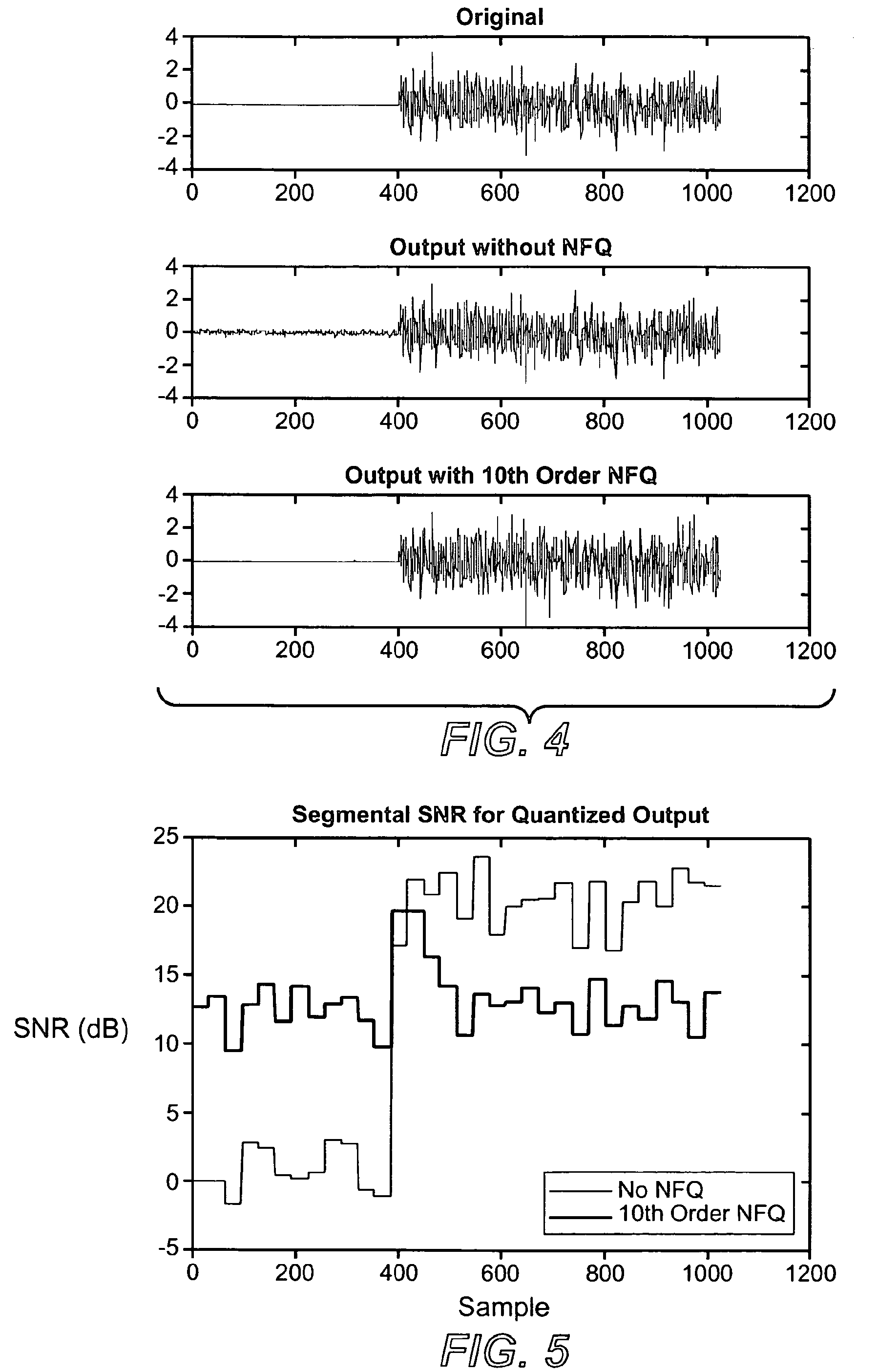

ActiveUS20100094637A1Limited numberPromote progressSpeech analysisTransmissionSpectral domainTemporal noise

In a first aspect, arbitrary shaping of the temporal envelope of noise is provided in spectral domain coding systems without the need of side-information. In the encoding, a filtered measure of quantization error is applied as a feedback signal to the frequency-domain representation of a discrete time-domain signal prior to quantization, so that the filtering parameters of said filtering affect the shaping of quantization noise in the time domain of the quantized frequency-domain representation of the discrete time-domain signal when it is inversely transformed from the frequency domain back to the time domain in decoding. This may be accomplished with respect to each of a plurality of frequency bins or groups of bins. In another aspect, frequency-domain noise-feedback quantizing in digital audio encoding is provided.

Owner:DOLBY LAB LICENSING CORP

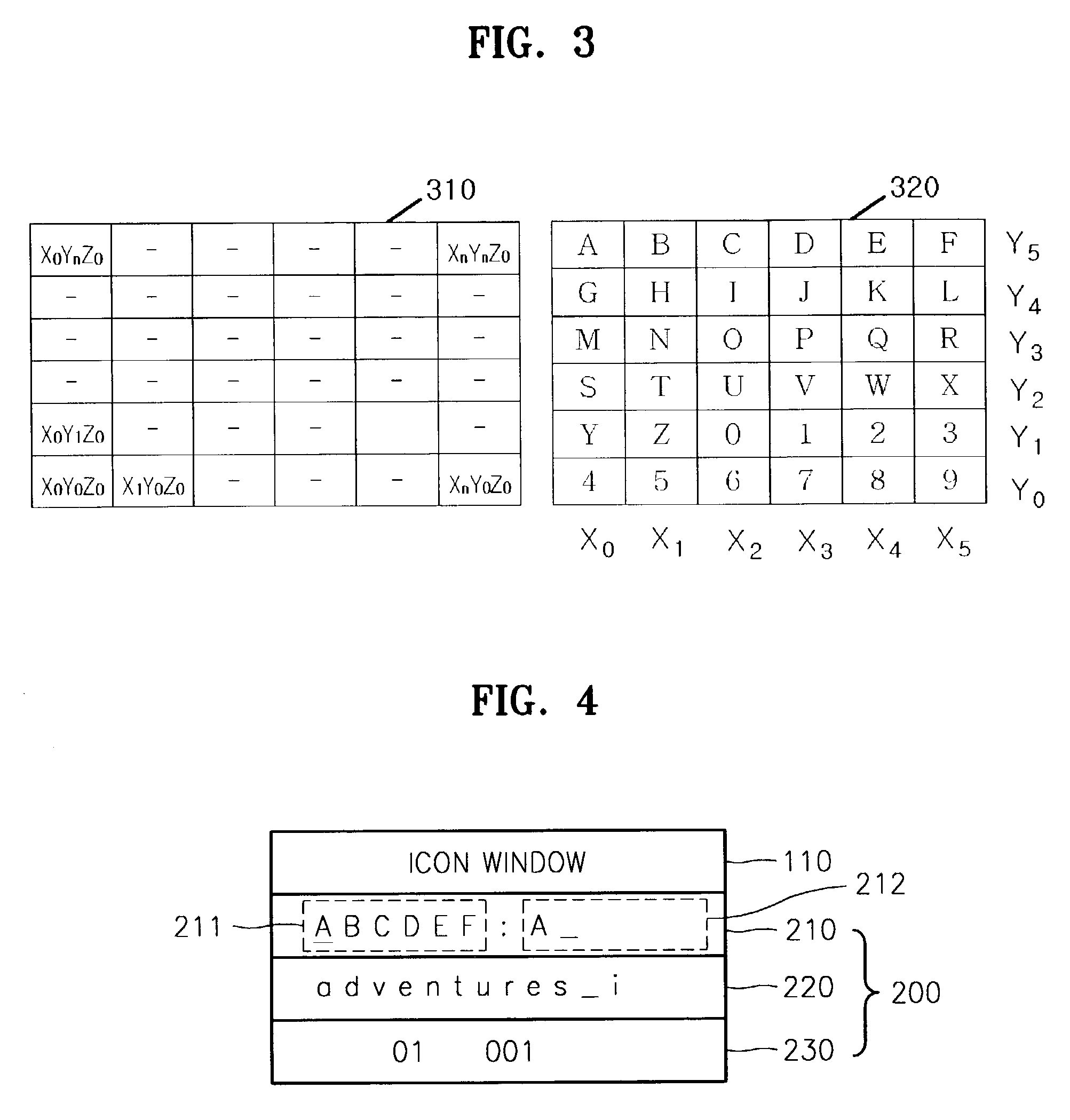

Method for inputting characters in portable device having limited display size and number of keys, and portable device using the same

ActiveUS7015899B2Easy and fast inputLimited numberInput/output for user-computer interactionDigital computer detailsComputer graphics (images)Virtual coordinates

A portable device includes a display unit, a memory, input keys, and a microprocessor. The display unit has a character window, which includes a selecting character window and a selected character window, for displaying characters. One character line including the character which has virtual coordinates indicated by a cursor is displayed in the selecting character window, and the character selected from the characters in the selecting character window is displayed in the selected character window by input keys. The memory stores the characters having intrinsic virtual coordinates, and several input keys serve for navigating across the characters by using the virtual coordinates of the characters to select the characters. The microprocessor controls the display of the characters on the display unit in correspondence to the input of the input keys.

Owner:SAMSUNG ELECTRONICS CO LTD

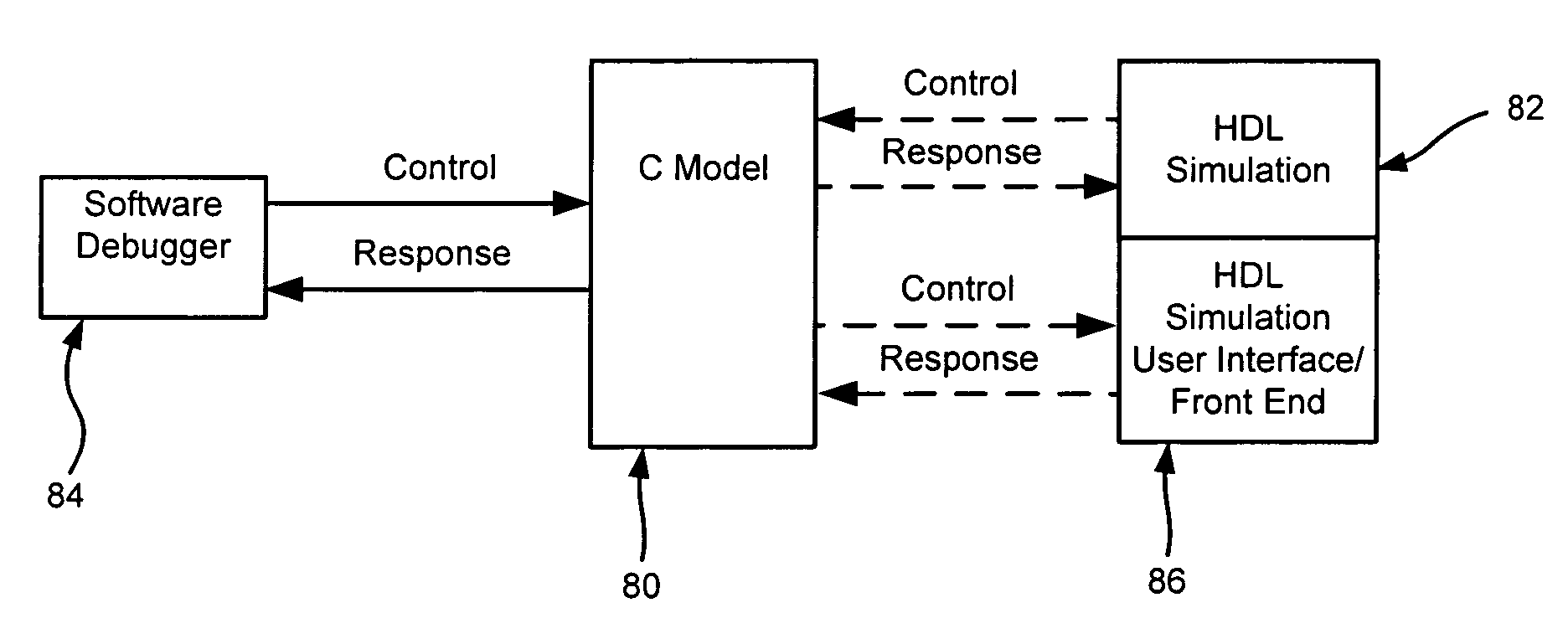

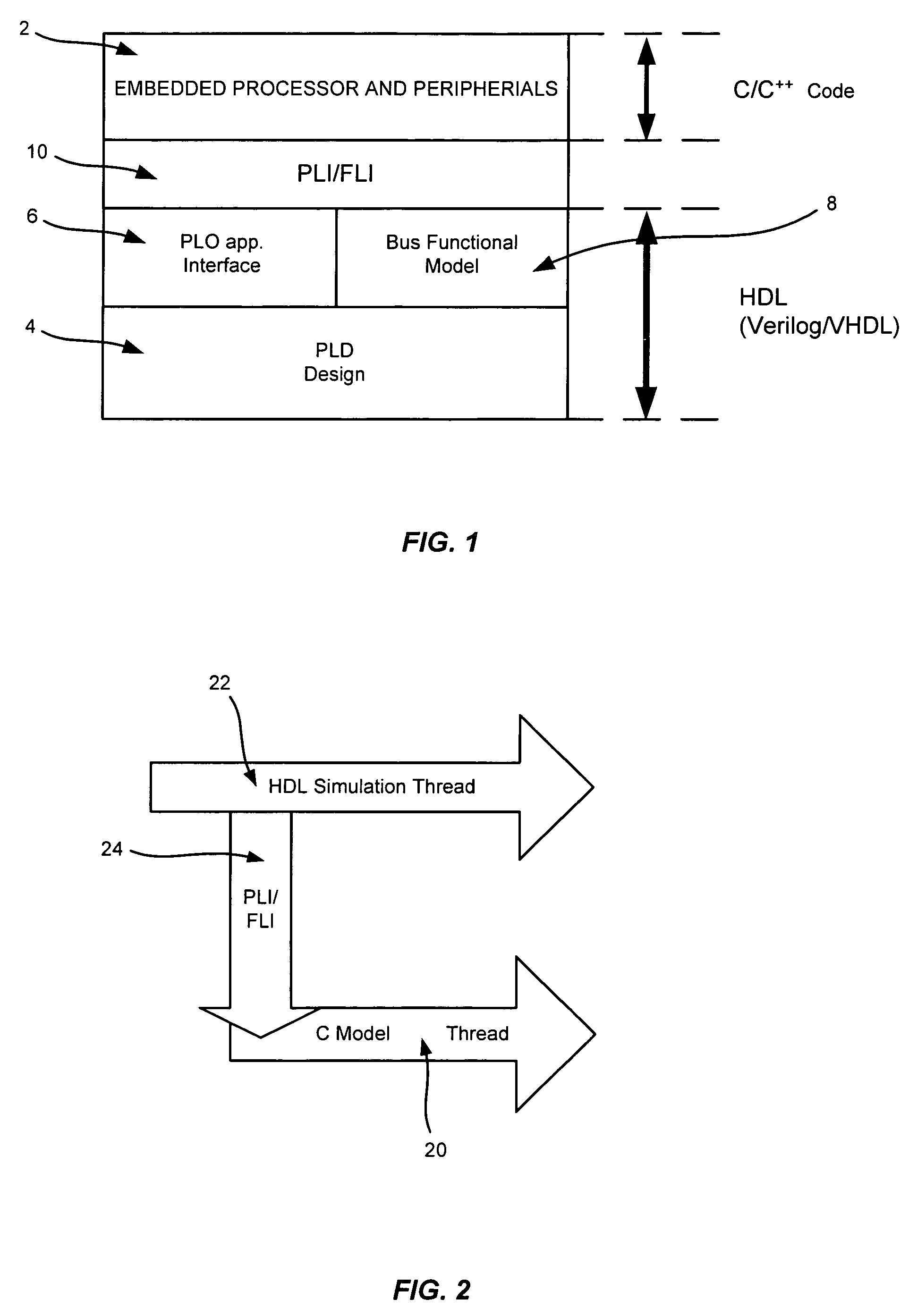

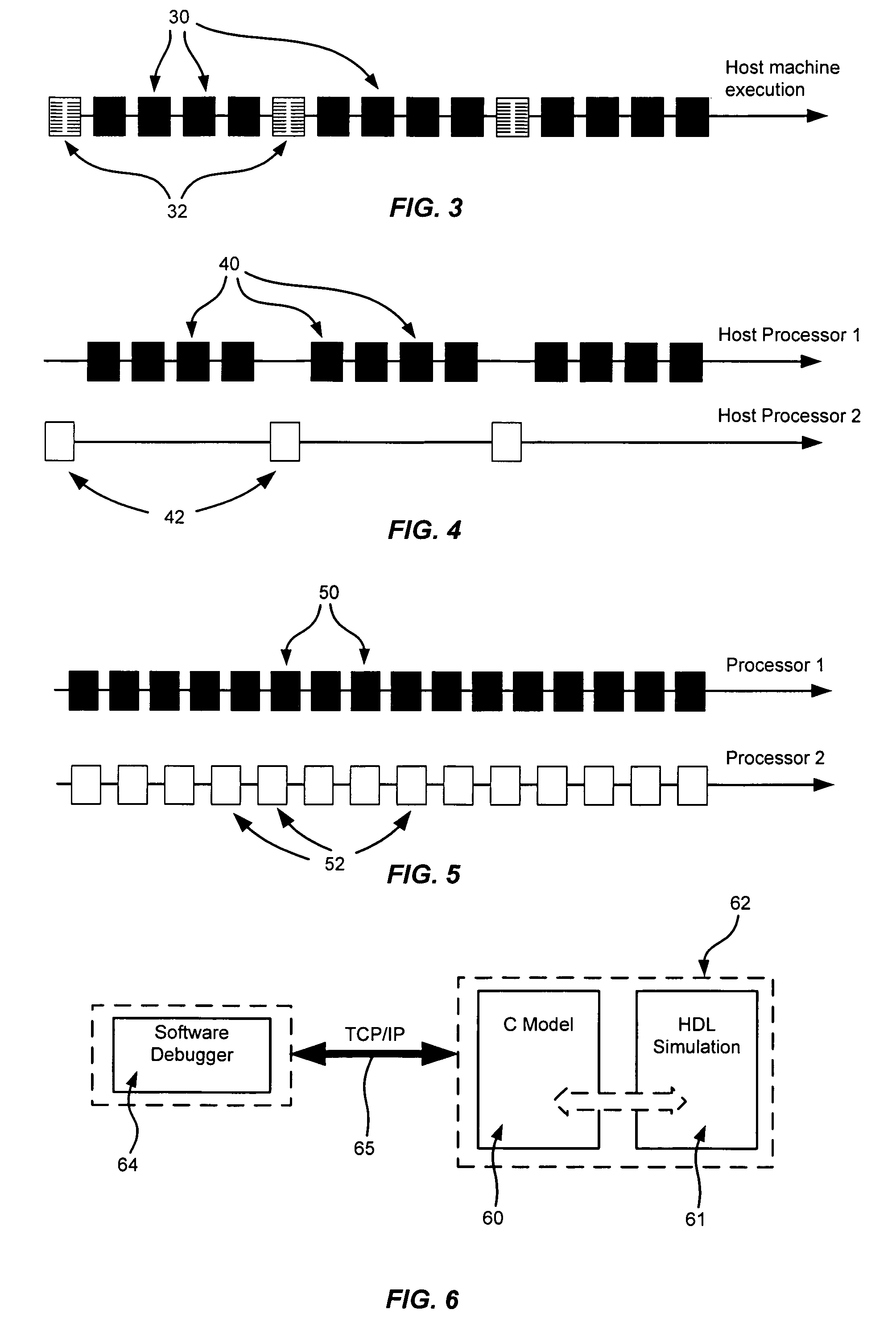

Simulation of hardware and software

InactiveUS7711535B1Fast simulationLimited numberCAD circuit designSpecial data processing applicationsProgrammable logic deviceSoftware

A method and apparatus are provided to allow co-verification of hardware and software elements asynchronously from a programmable logic device (PLD).

Owner:ALTERA CORP

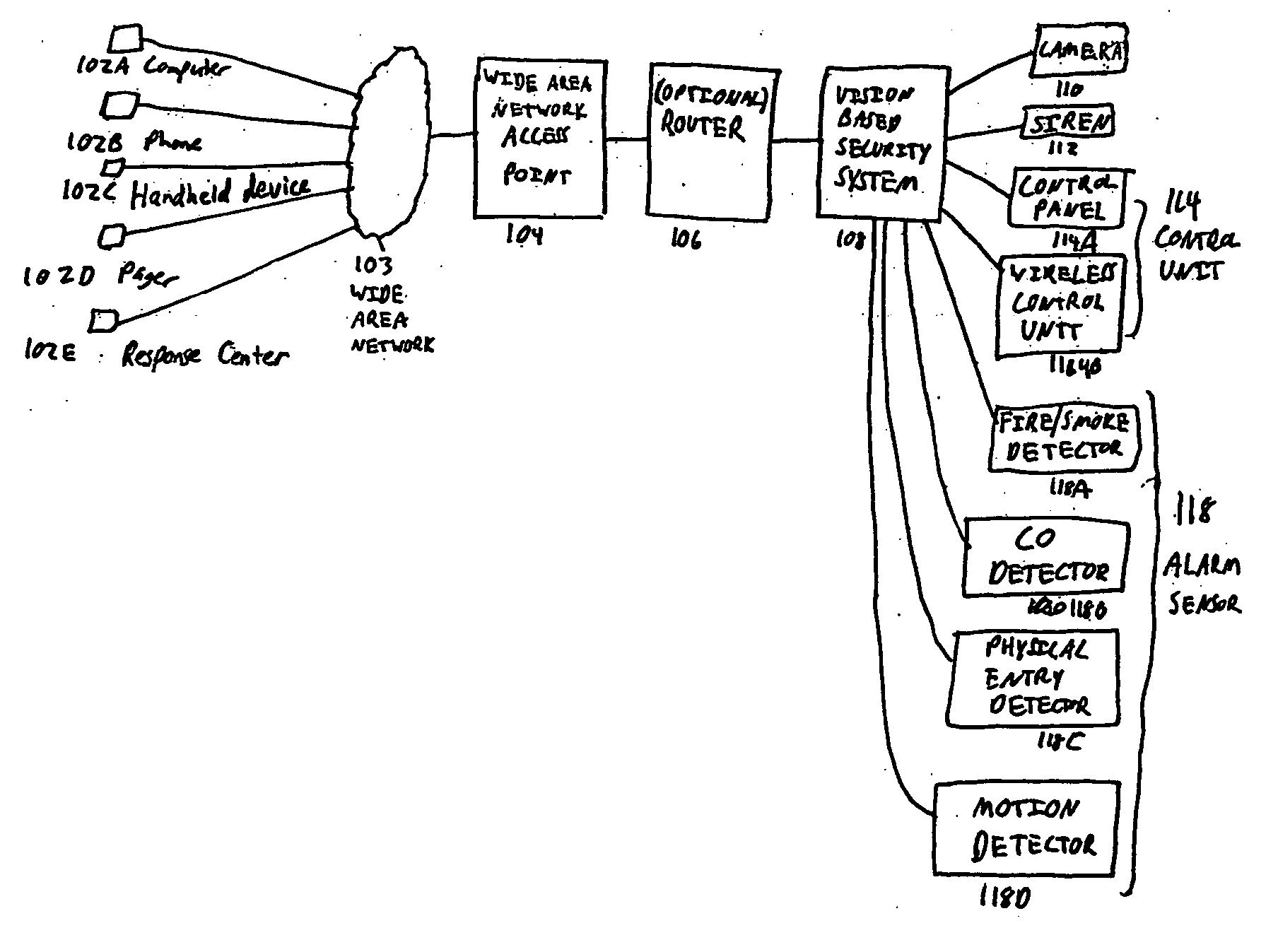

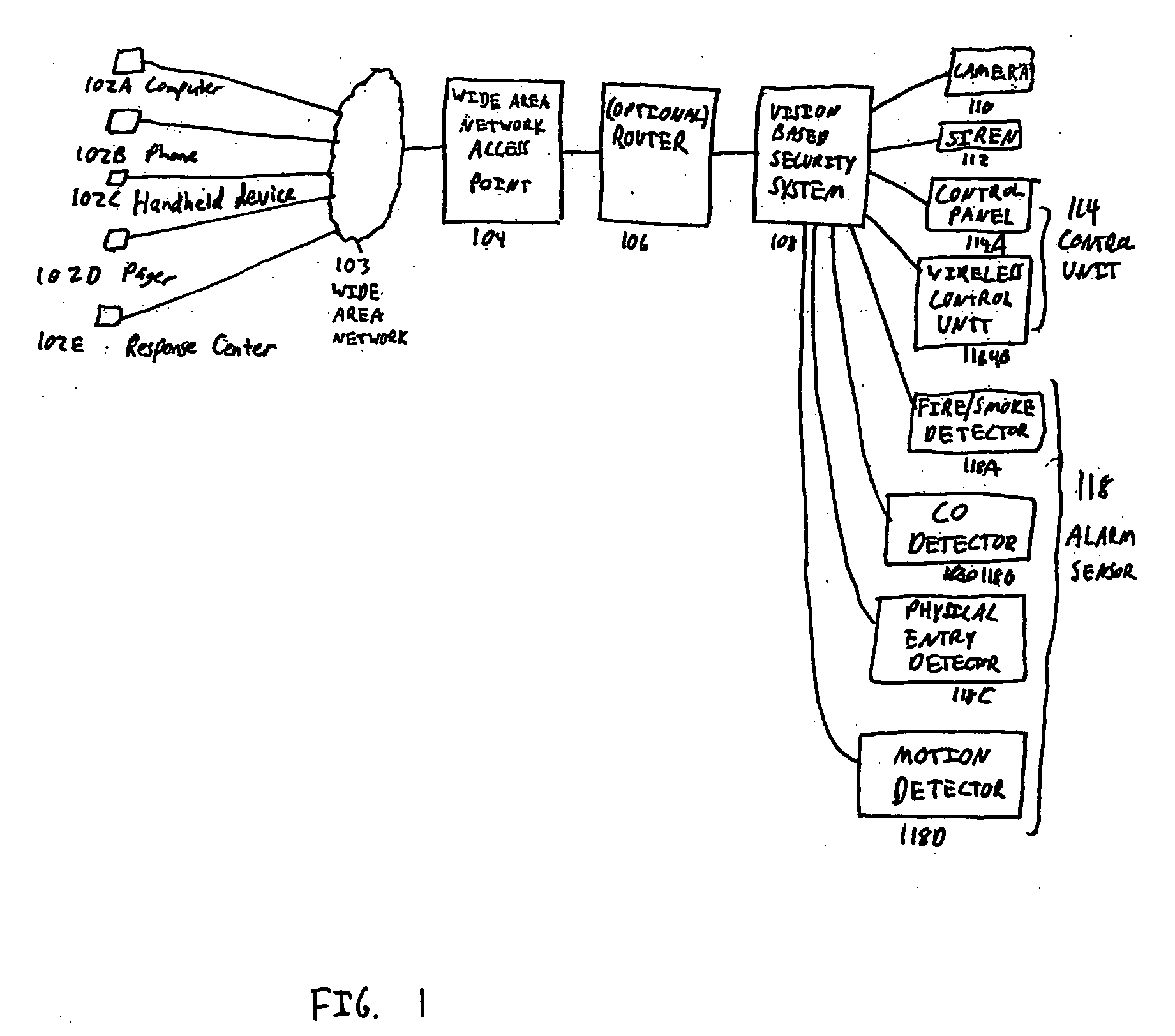

System and method for vision-based security

InactiveUS20060085831A1Limited numberReduce in quantityClosed circuit television systemsTwo-way working systemsVision basedNetwork camera

A system and method for arming and disarming a network camera, limiting the number of e-mails sent by the network camera to a user, enabling the network camera to initiate phone calls, transmitting and / or recording video and audio, connecting the network camera to other detection devices, activating a siren, and allowing users to identify themselves within a fixed period of time before taking notification actions.

Owner:TELULAR

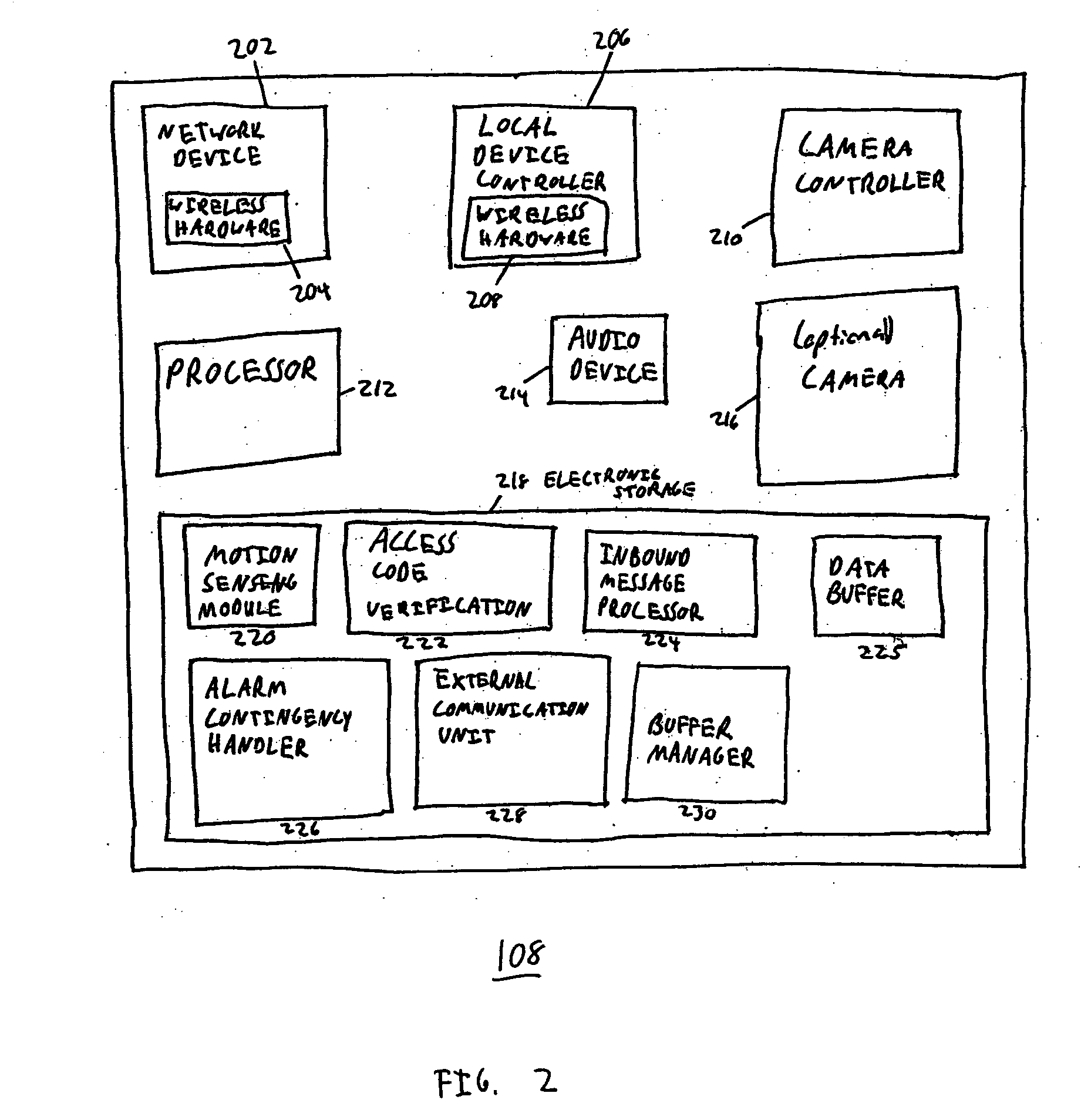

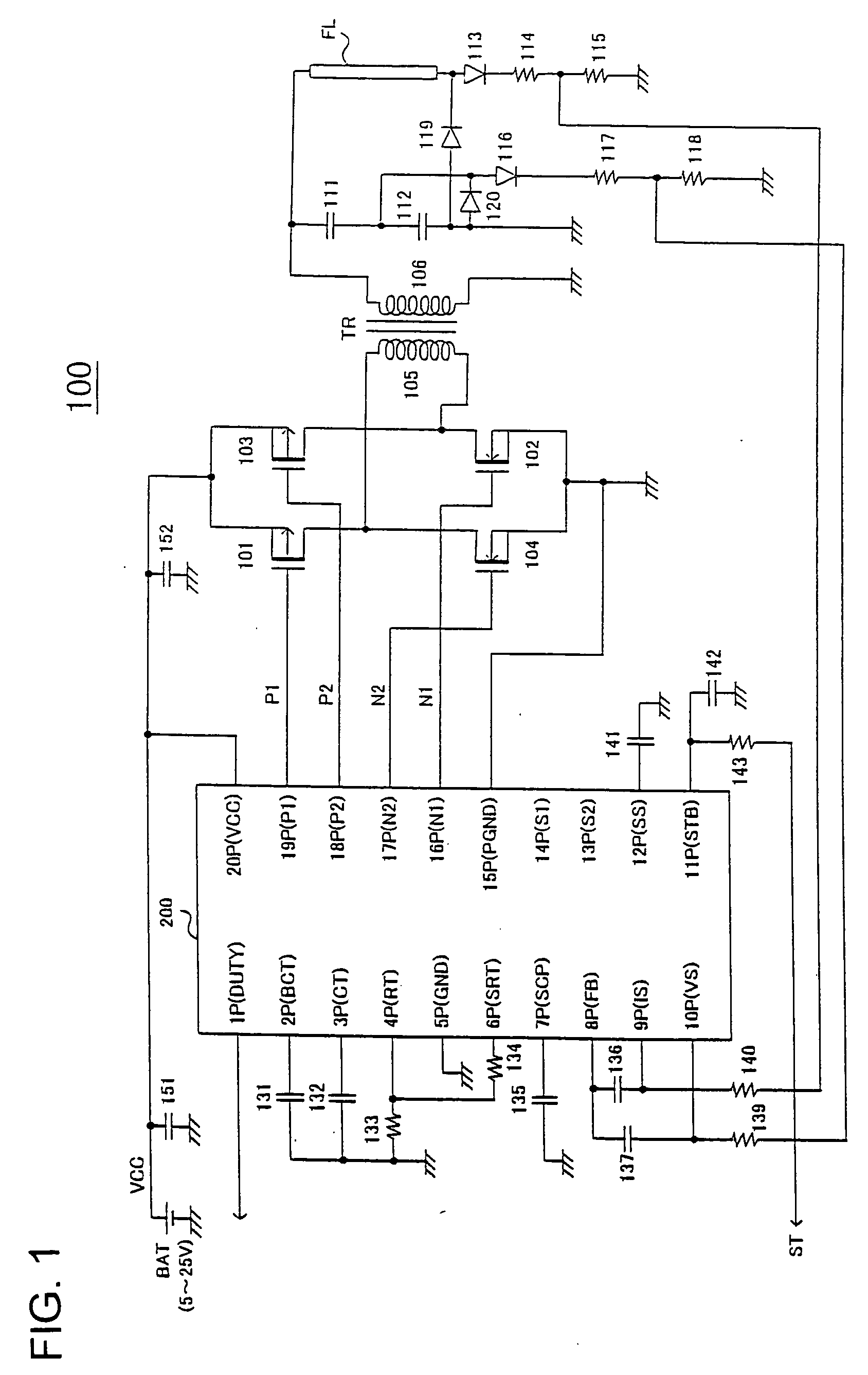

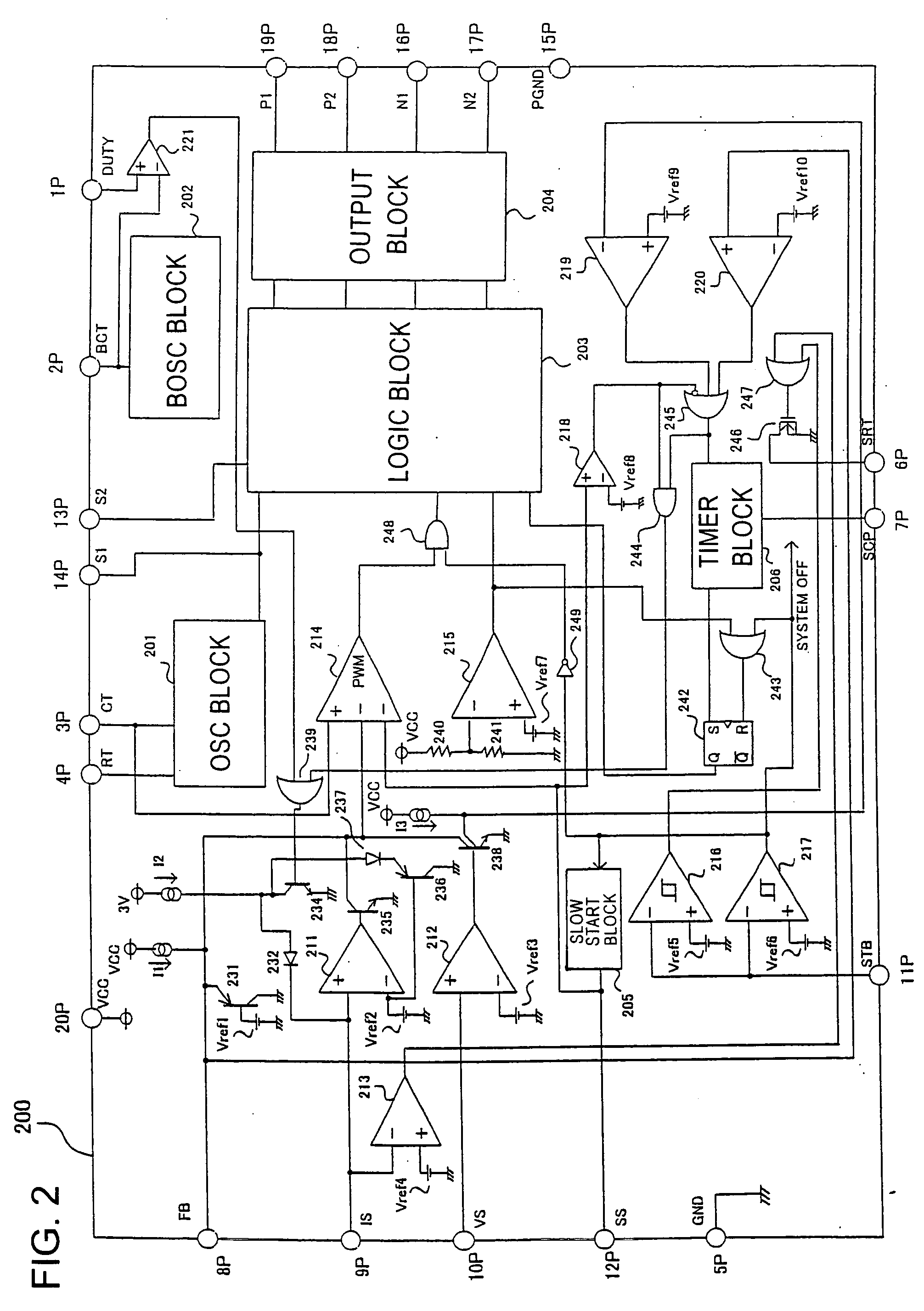

Dc-ac converter parallel operation system and controller ic therefor

InactiveUS20050128775A1Simplify structureLimited numberBatteries circuit arrangementsElectric lighting sourcesTriangular waveDc ac converter

A multiplicity of synchronized inverters for driving a multiplicity of loads such as CCFLs that require high ac voltages are arranged in close proximity of the respective loads and controlled in phase. A frequency determination capacitor and a frequency determination resistor are connected to one of the inverters to generate a triangular wave signal and a clock signal. The triangular wave signal and clock signal thus generated are supplied to other inverters to synchronize all the loads so that they can be controlled in phase. The resistance of the frequency determination resistor is set to a substantially small magnitude at the time of startup to increase the frequency of the triangular wave signal, thereby enabling quick startup of the loads.

Owner:ROHM CO LTD

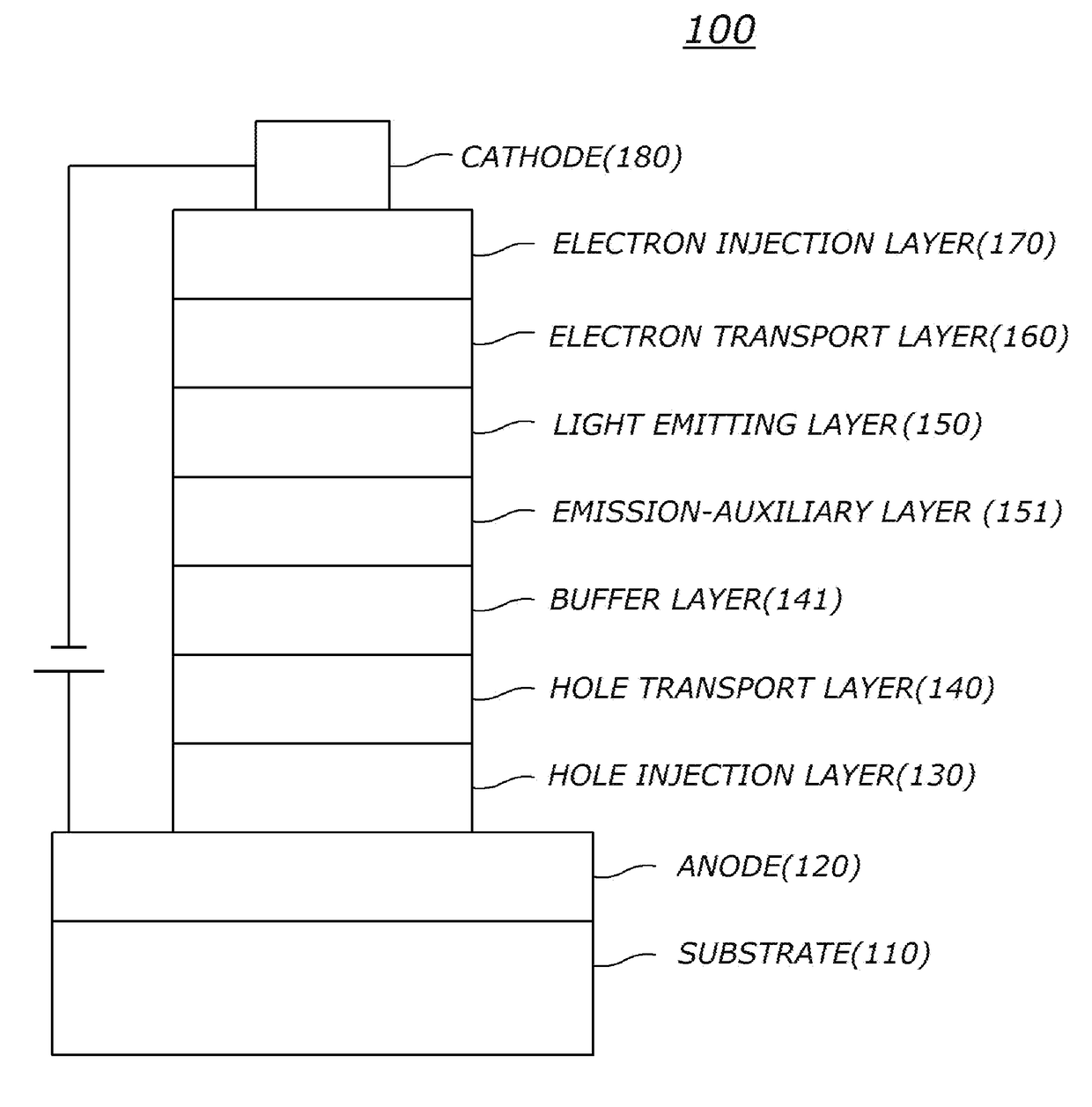

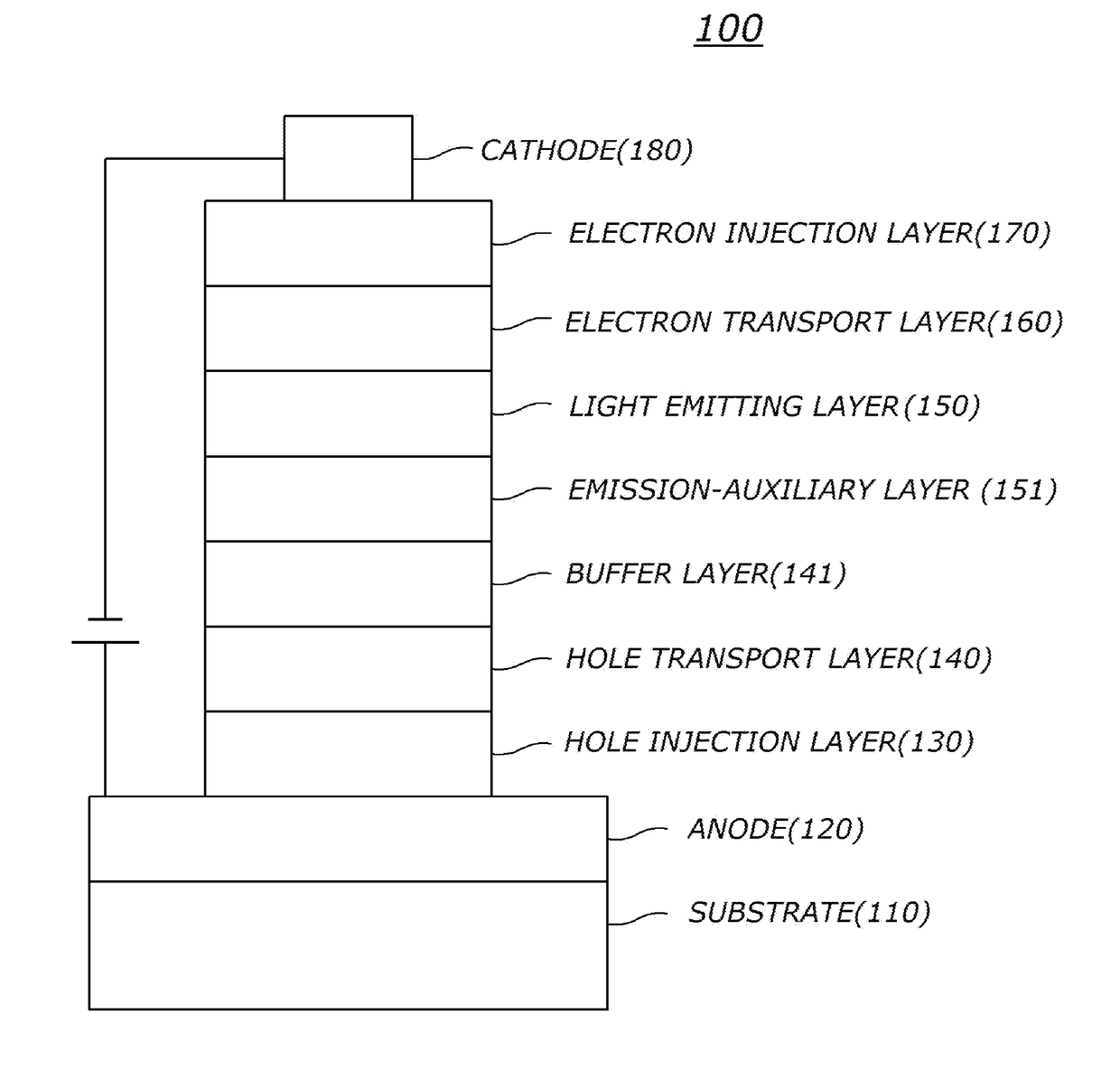

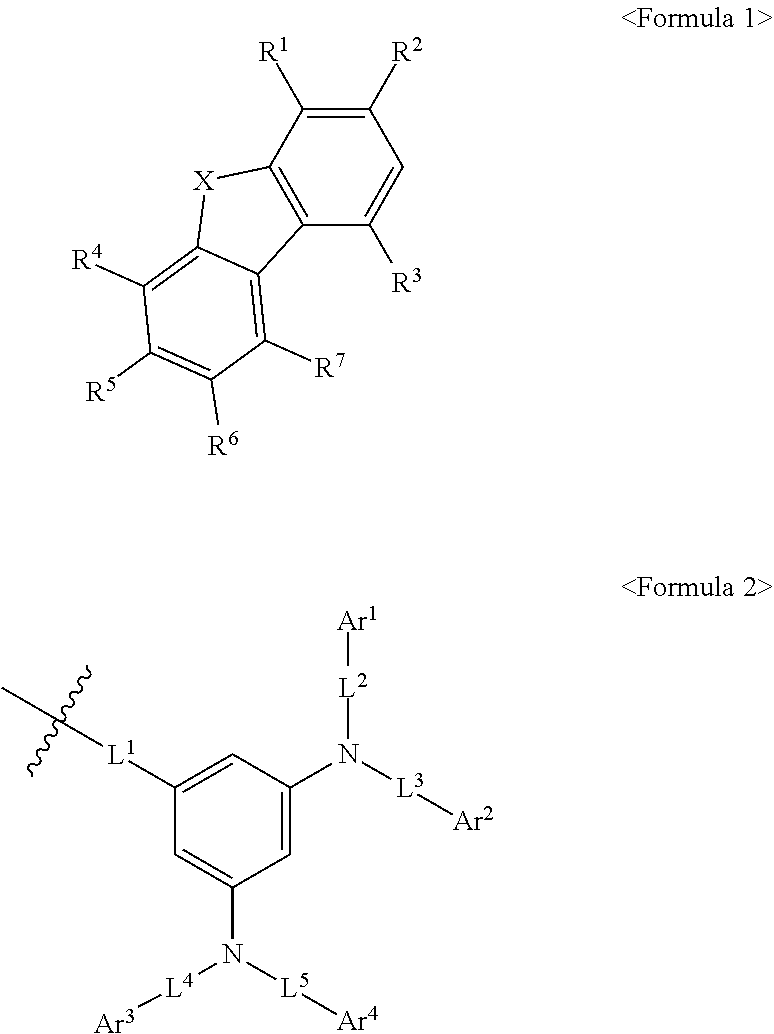

Compound for organic electric element, organic electric element comprising the same and electronic device thereof

ActiveUS20180072695A1Reduce the driving voltageEasy to chargeOrganic chemistryElectroluminescent light sourcesElectronic componentElectron

Provided are a compound represented by Formula 1, and an organic electric element comprising a first electrode, a second electrode, and an organic material layer formed between the first electrode and the second electrode, wherein the organic material layer comprised the compound represented by Formula 1, and the driving voltage of an organic electronic device can be lowered, and the luminous efficiency, color purity and life time of an organic electronic device can be improved by comprising the compound represented by Formula 1 in the organic material layer.

Owner:DUK SAN NEOLUX

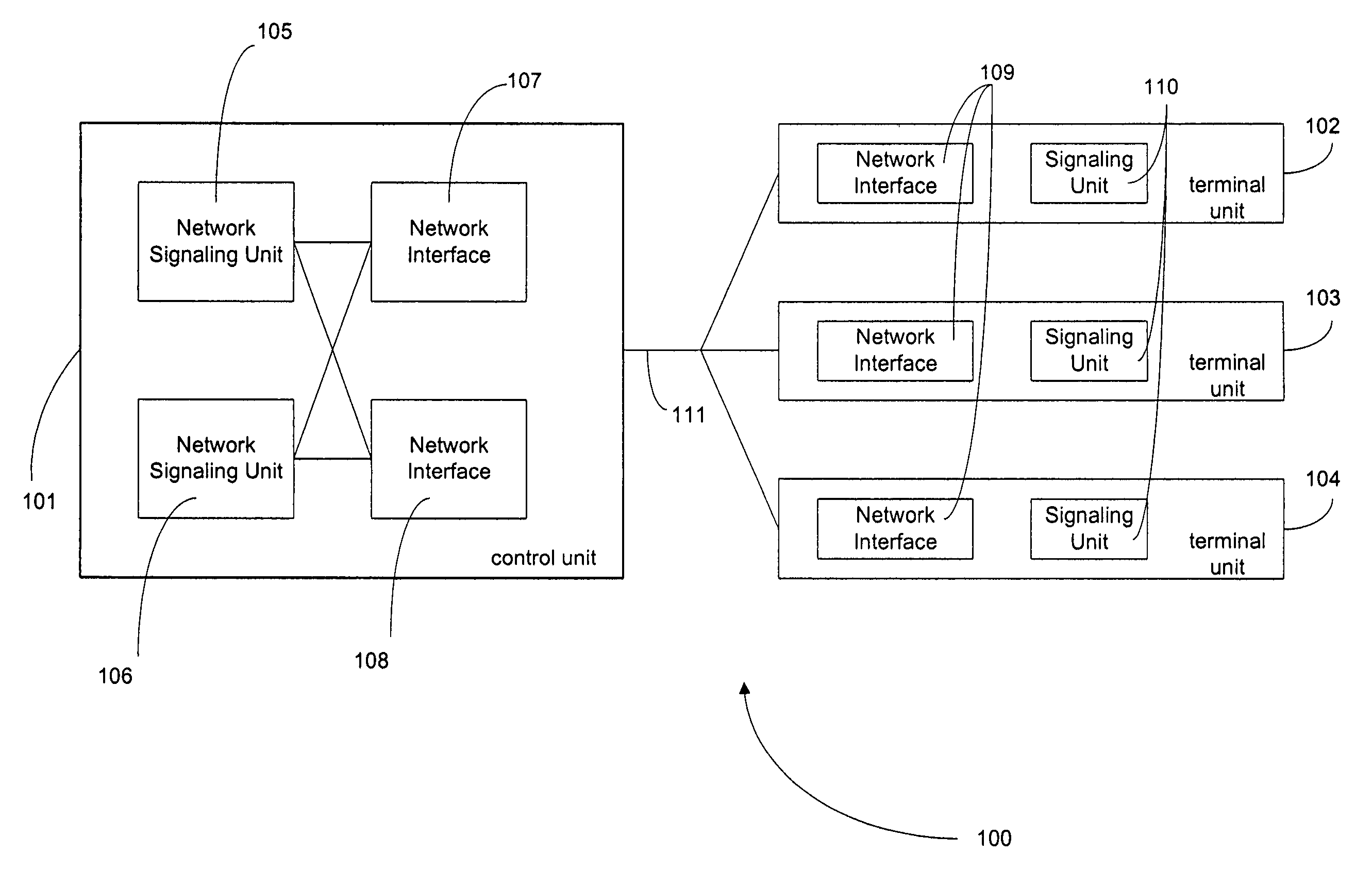

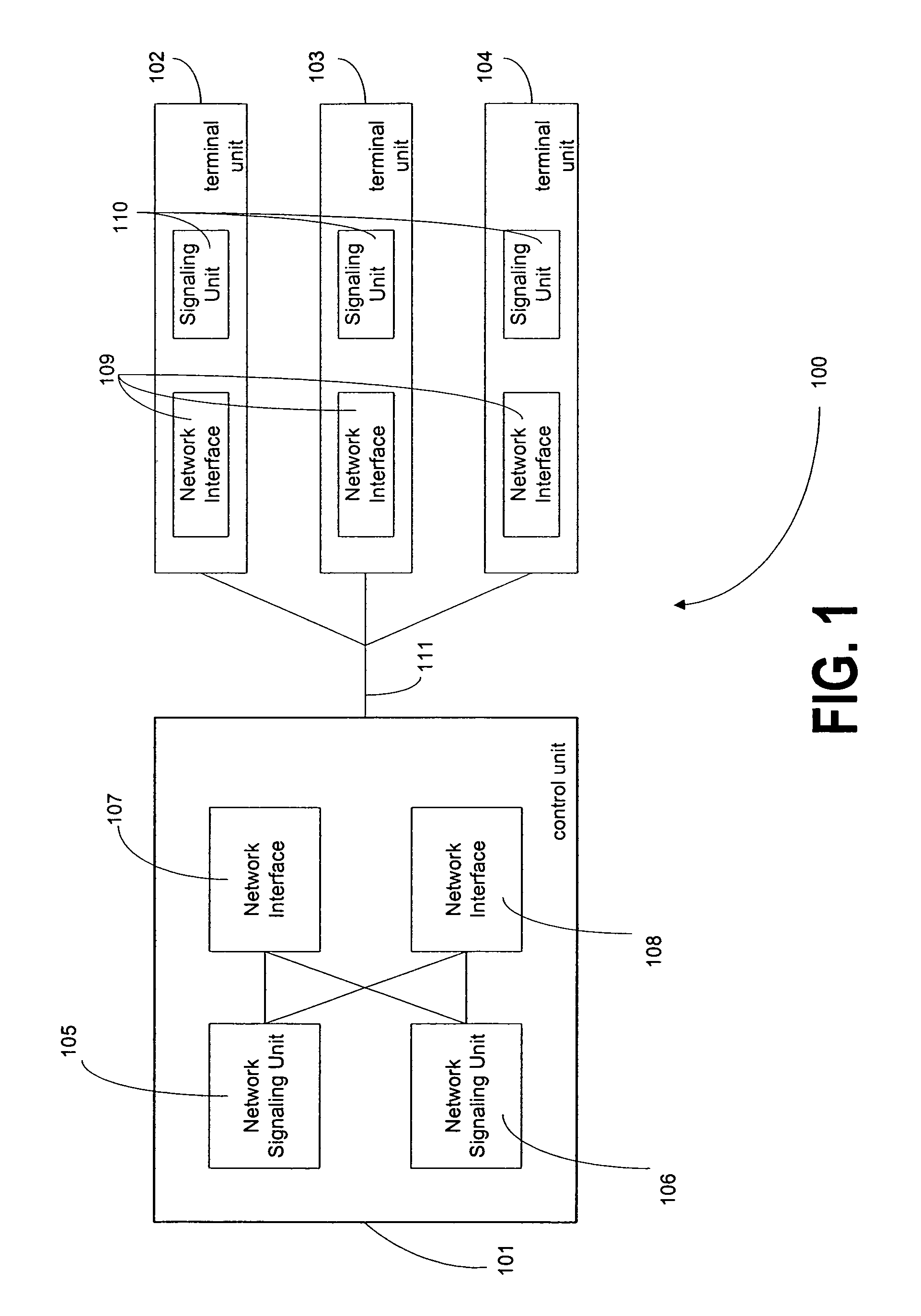

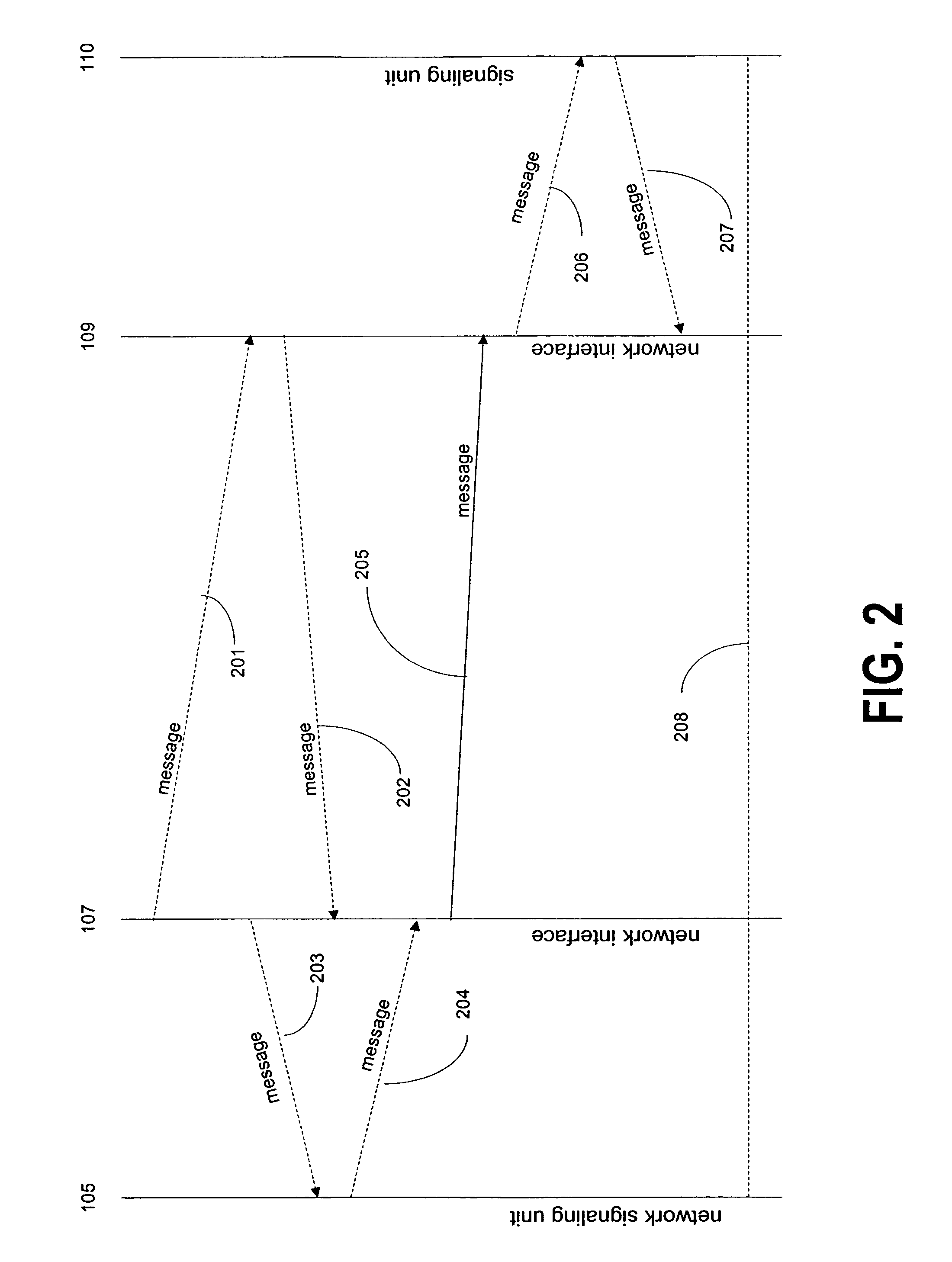

Method arrangement and receiver for establishing connections in a multiple-protocol communications network

InactiveUS7006528B1Limited numberPulse modulation television signal transmissionTelephonic communicationEngineeringConnected device

A communications system comprises a central unit (101) and terminals (102, 103, 104). It is equipped so as to establish and maintain a signaling connection between the central unit and at least one terminal using one of at least two alternative signaling protocols. To that end it comprises in the central unit a device for indicating to a terminal the signaling protocols supported by the central unit, and a device for setting up via the central unit's network interface a signaling connection between the central unit's signaling unit and the terminal, using a selected signaling protocol. Correspondingly, in the terminal the system comprises a device for indicating to the central unit the signaling protocol supported by the terminal in response to a message sent by the central unit as well as a device for setting up via the terminal's network interface a signaling connection between the terminal's signaling unit and the central unit, using a protocol supported by the terminal.

Owner:NOKIA TECHNOL GMBH

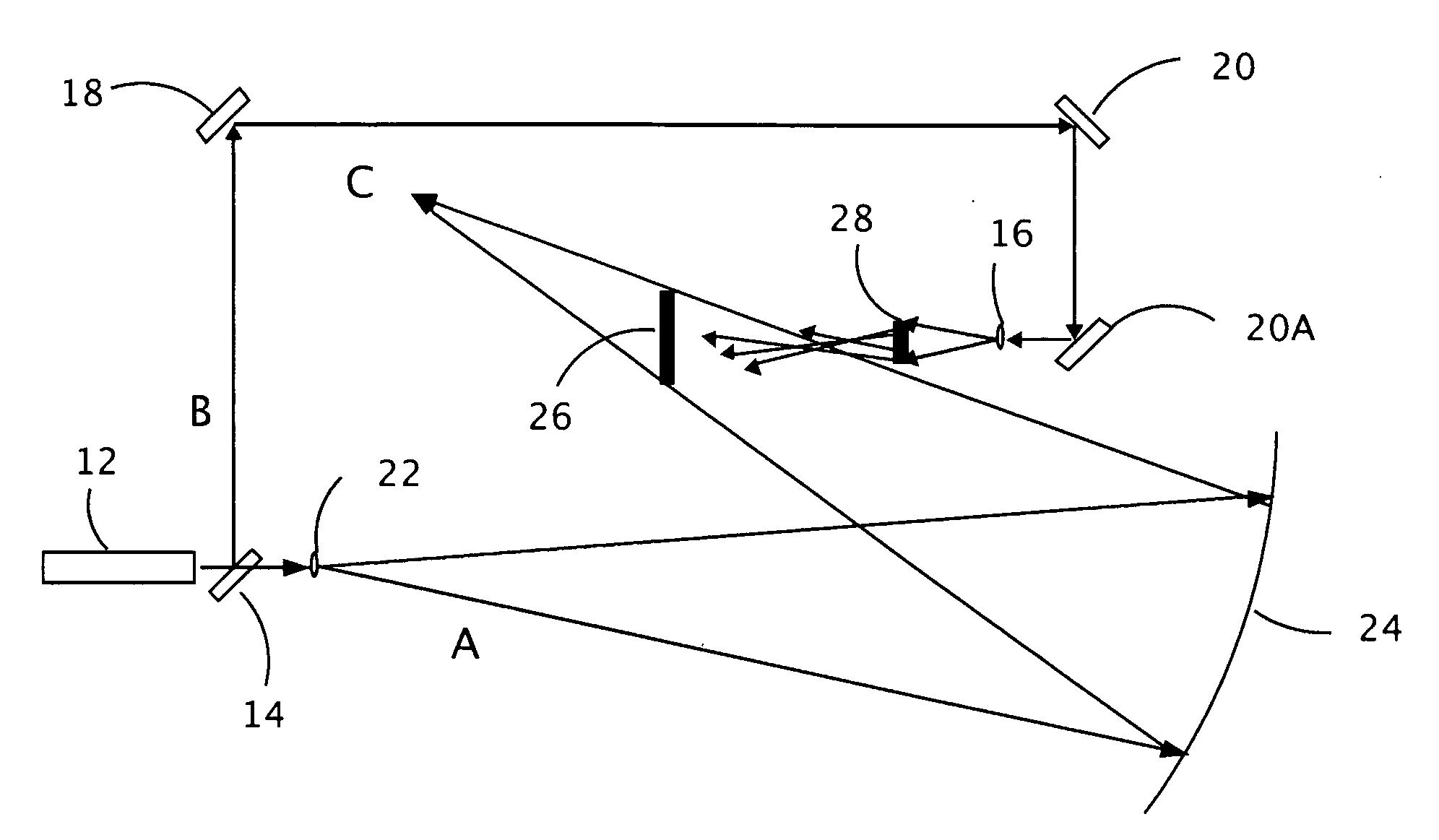

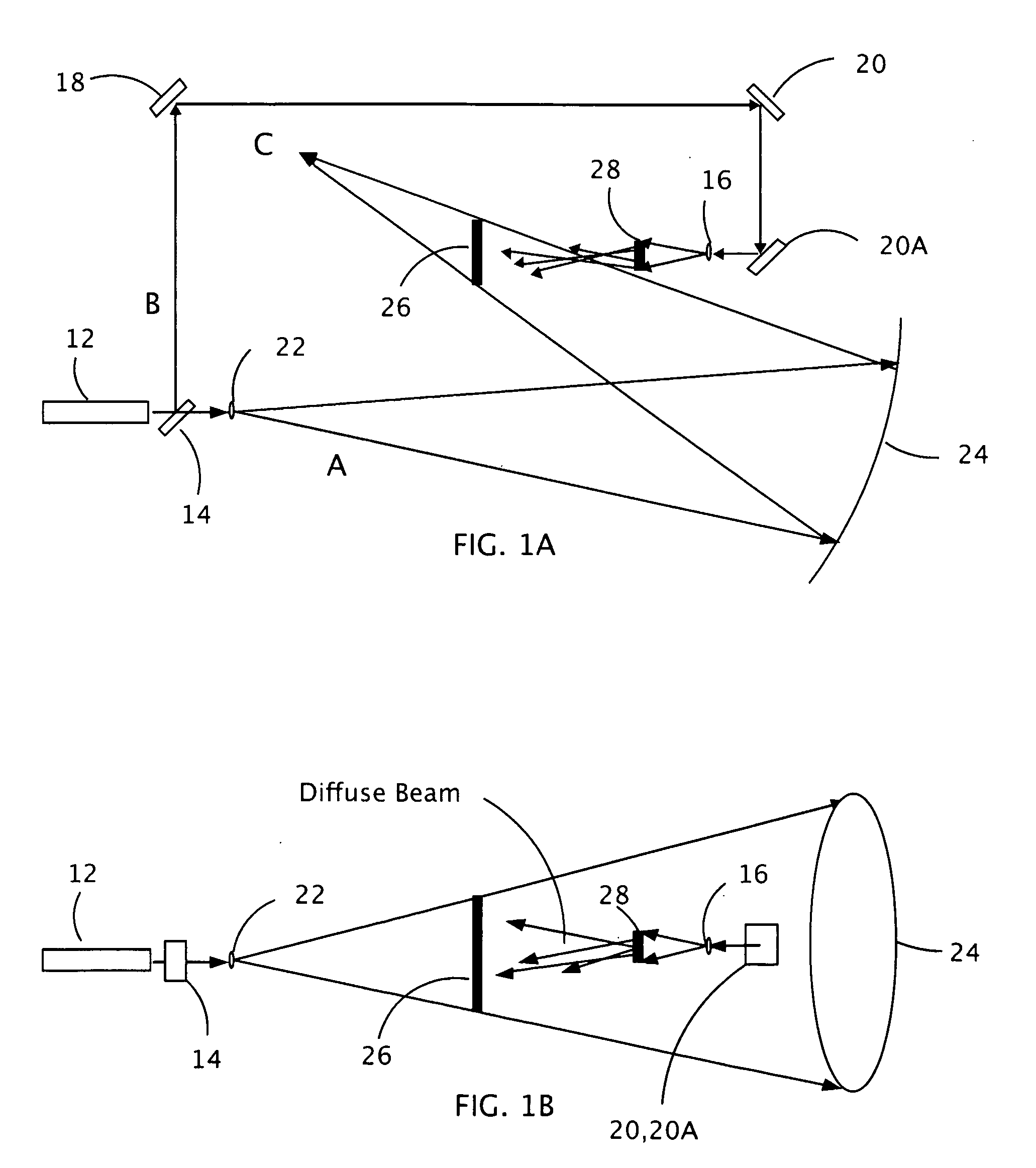

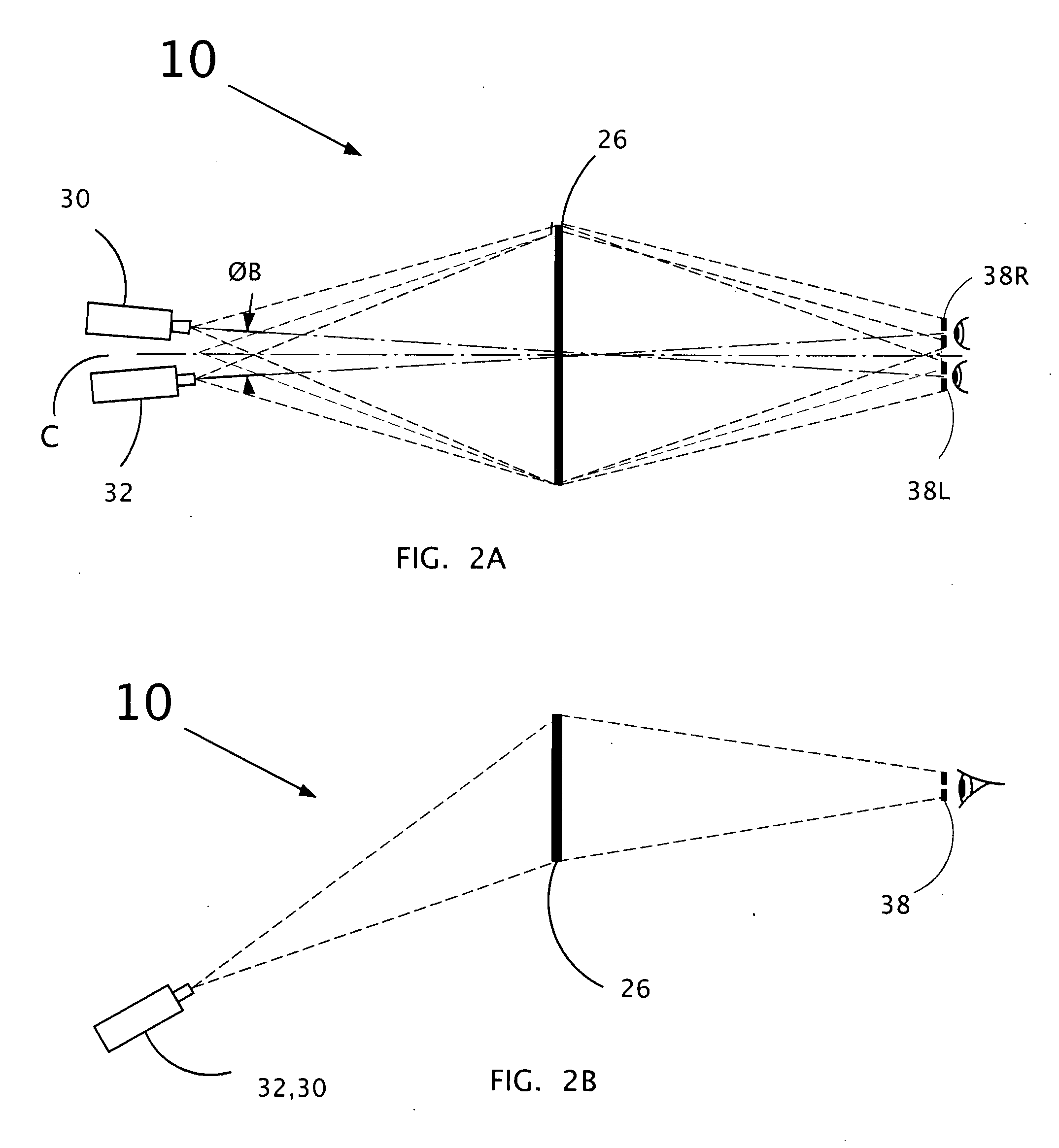

Auto-stereoscopic diffraction optics imaging system providing multiple viewing pupil pairs

InactiveUS20080007809A1Limited numberHolographic light sources/light beam propertiesSteroscopic systemsStereoscopic imagingPhysics

An autostereoscopic imaging system is disclosed that provides for a three dimensional display of an image to multiple observers simultaneously from a single pair of stereoscopic projectors. The system provides for high quality immersive imagery using a holographic diffractive optical element that is made and configured to contain multiple holograms of optical diffusers, each of the holograms having a common reference beam and being made with each diffuser in a different location. A pair of projectors placed astride the reference beam virtual focus projects a stereoscopic image onto the diffractive optical element, such that the plurality of holograms reconstructs multiple stereoscopic images at multiple locations corresponding to the location where the diffusers were previously located during the recording of each respective hologram. Methods of making the diffractive optical element with a plurality of holograms are also disclosed. The holograms may be made on separate plates and laminated together, or may be made by simultaneous, sequential, or repeated partial sequential exposures onto a single holographic plate.

Owner:MOSS GAYLORD E

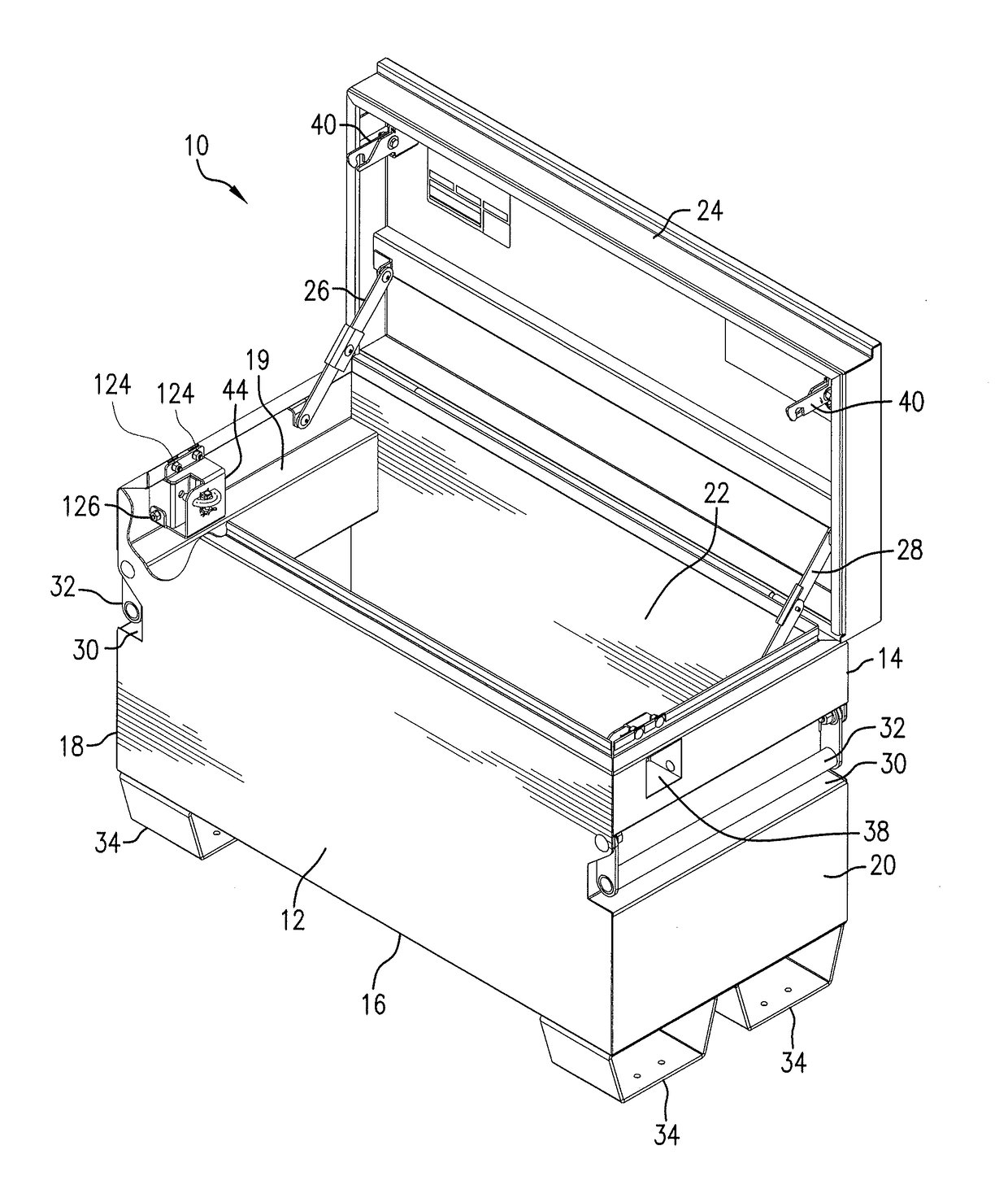

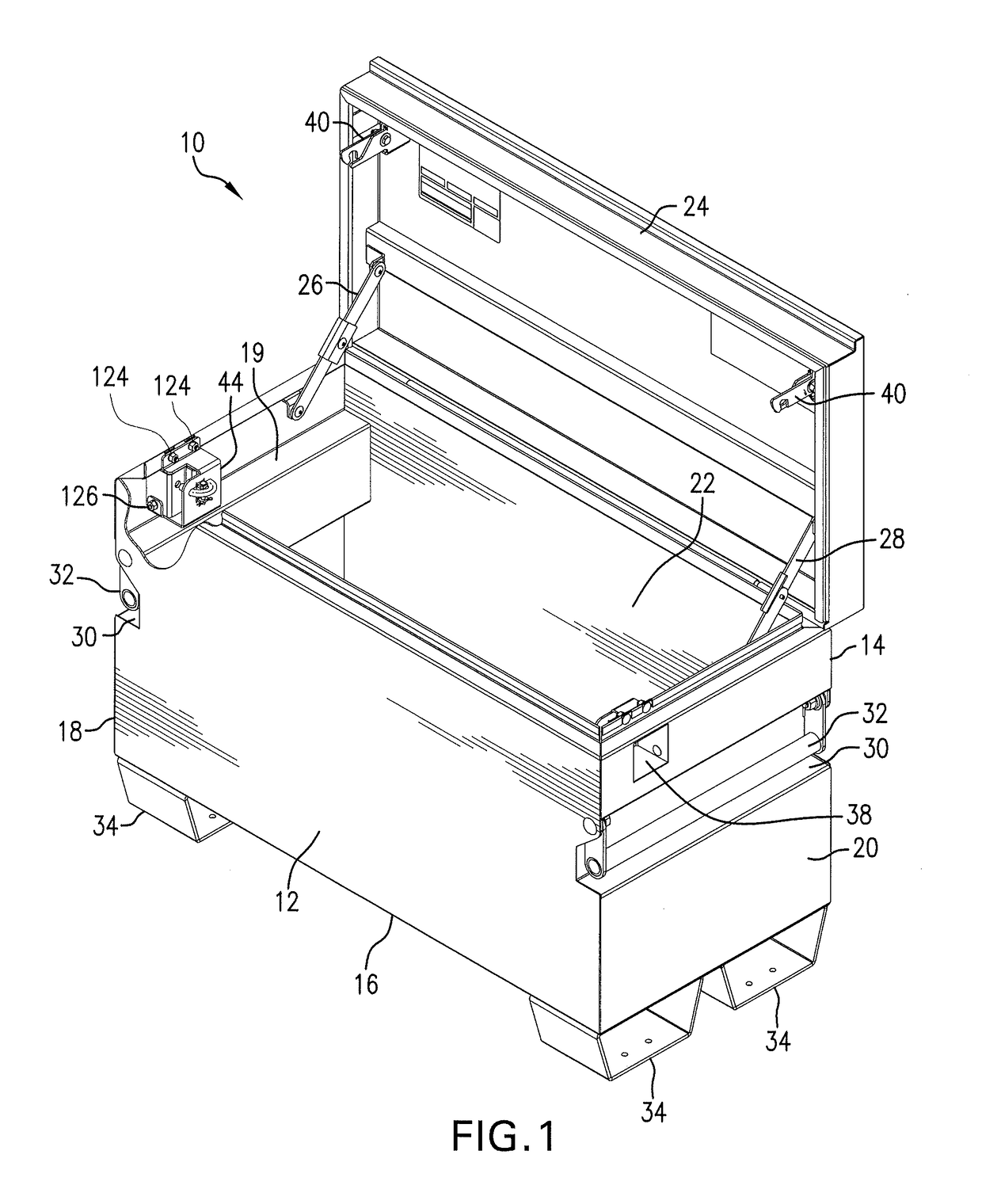

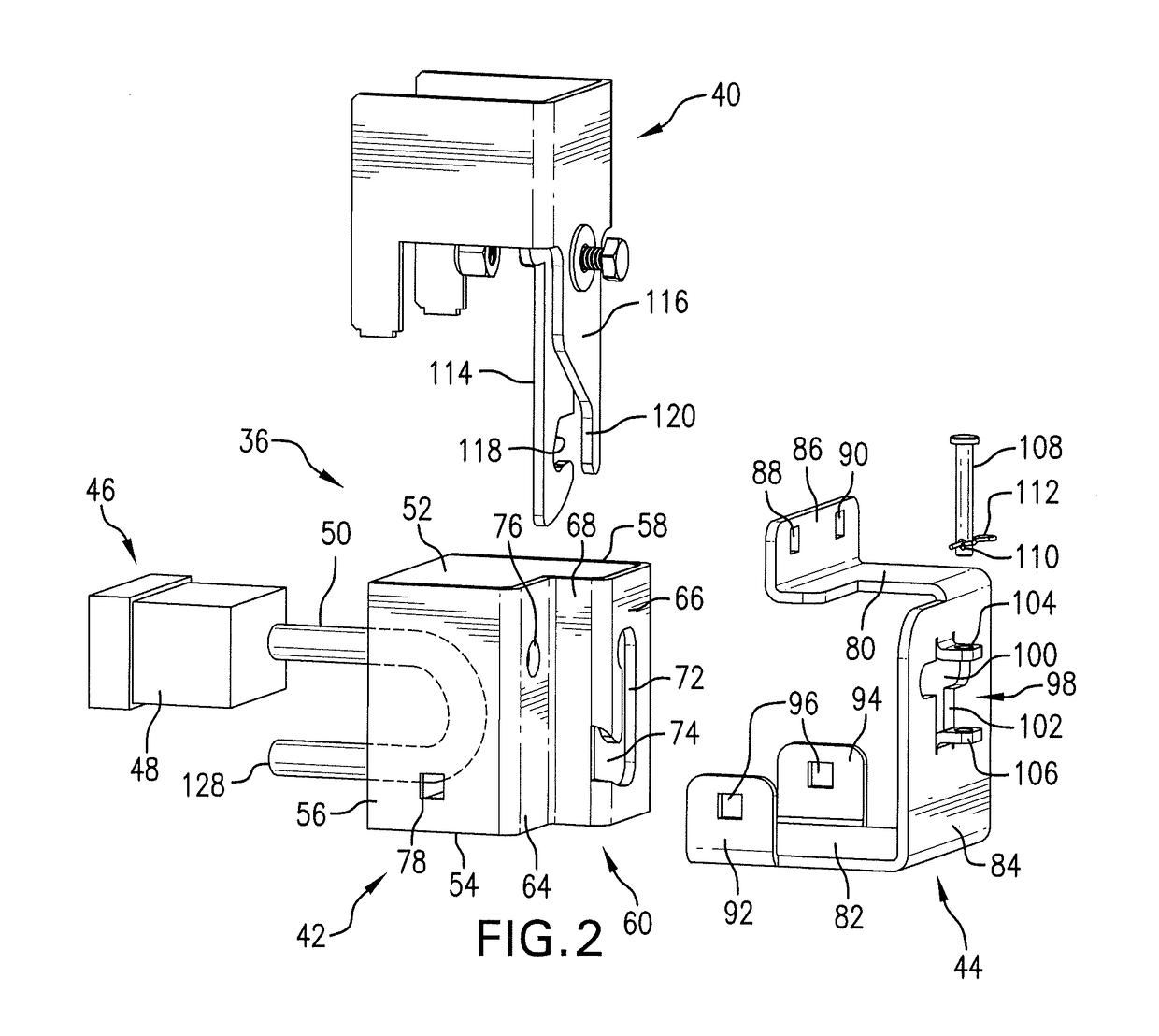

Container with improved locking system

ActiveUS20170233155A1Limited numberFirmly connectedPadlocksNon-removalbe lids/coversMechanical engineeringEngineering

A locking system for a storage container provides a reliable and durable means of locking the lid in the closed position with a limited number of moving parts while providing resistance to tampering and theft.

Owner:WERNER CO

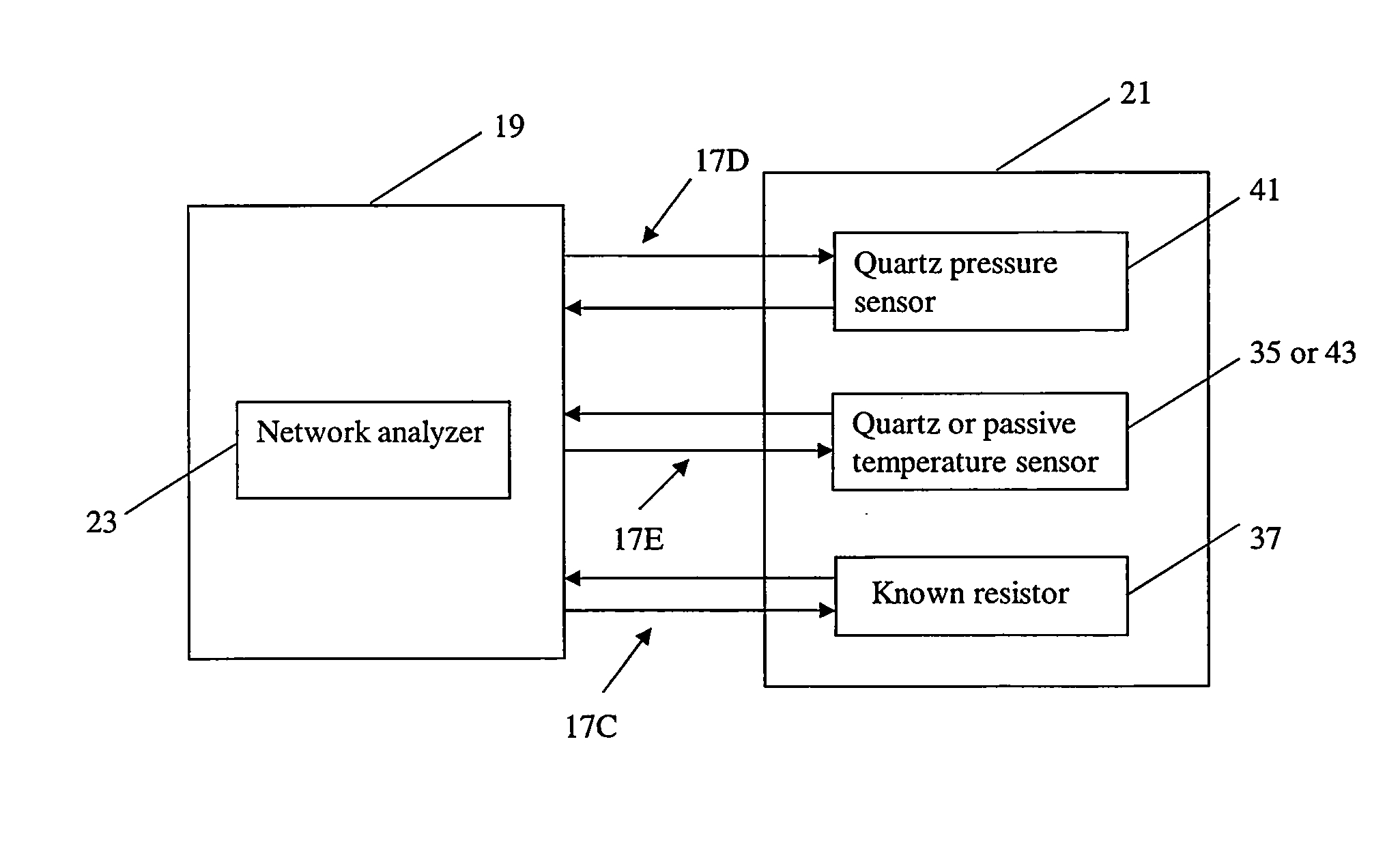

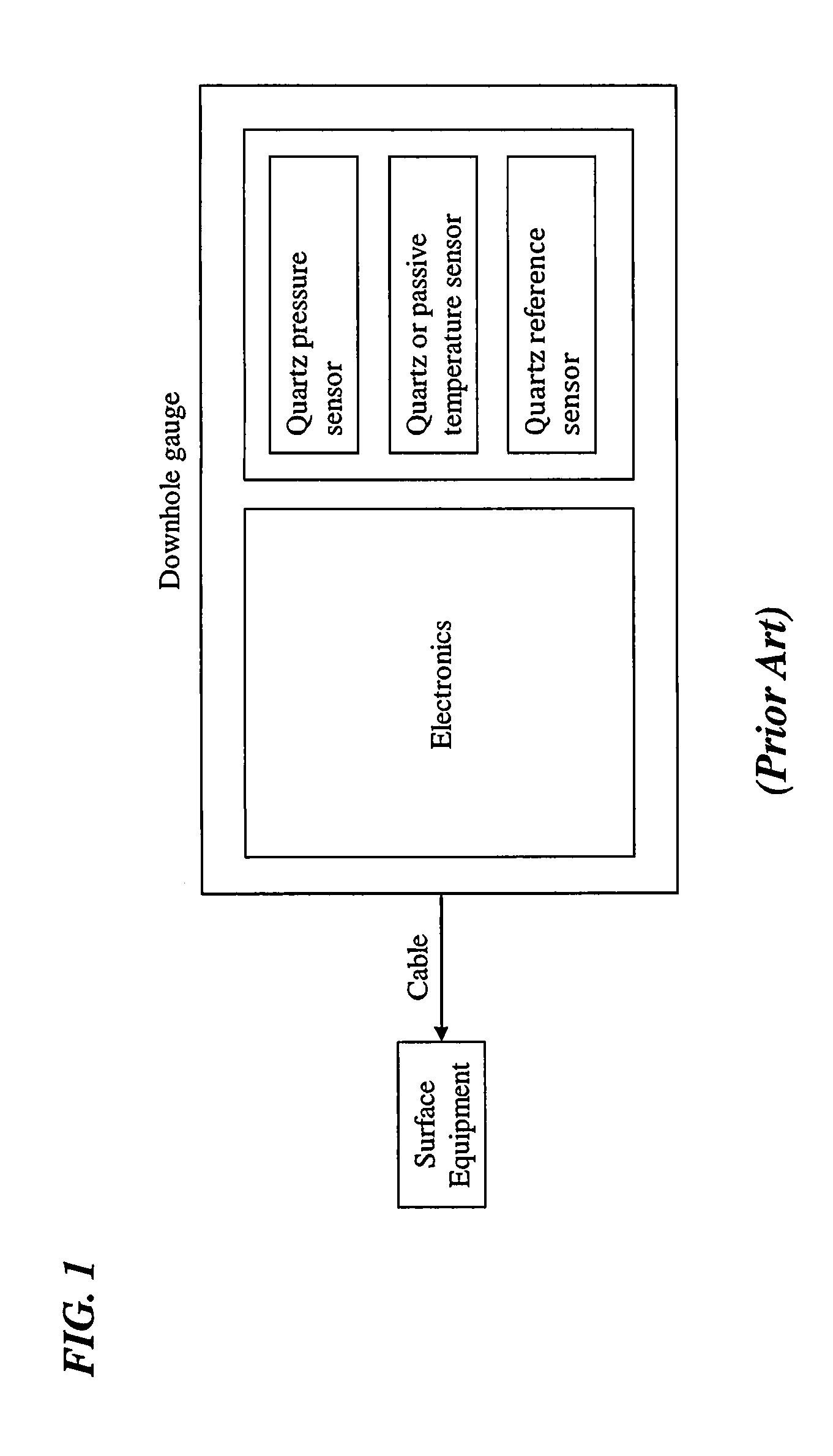

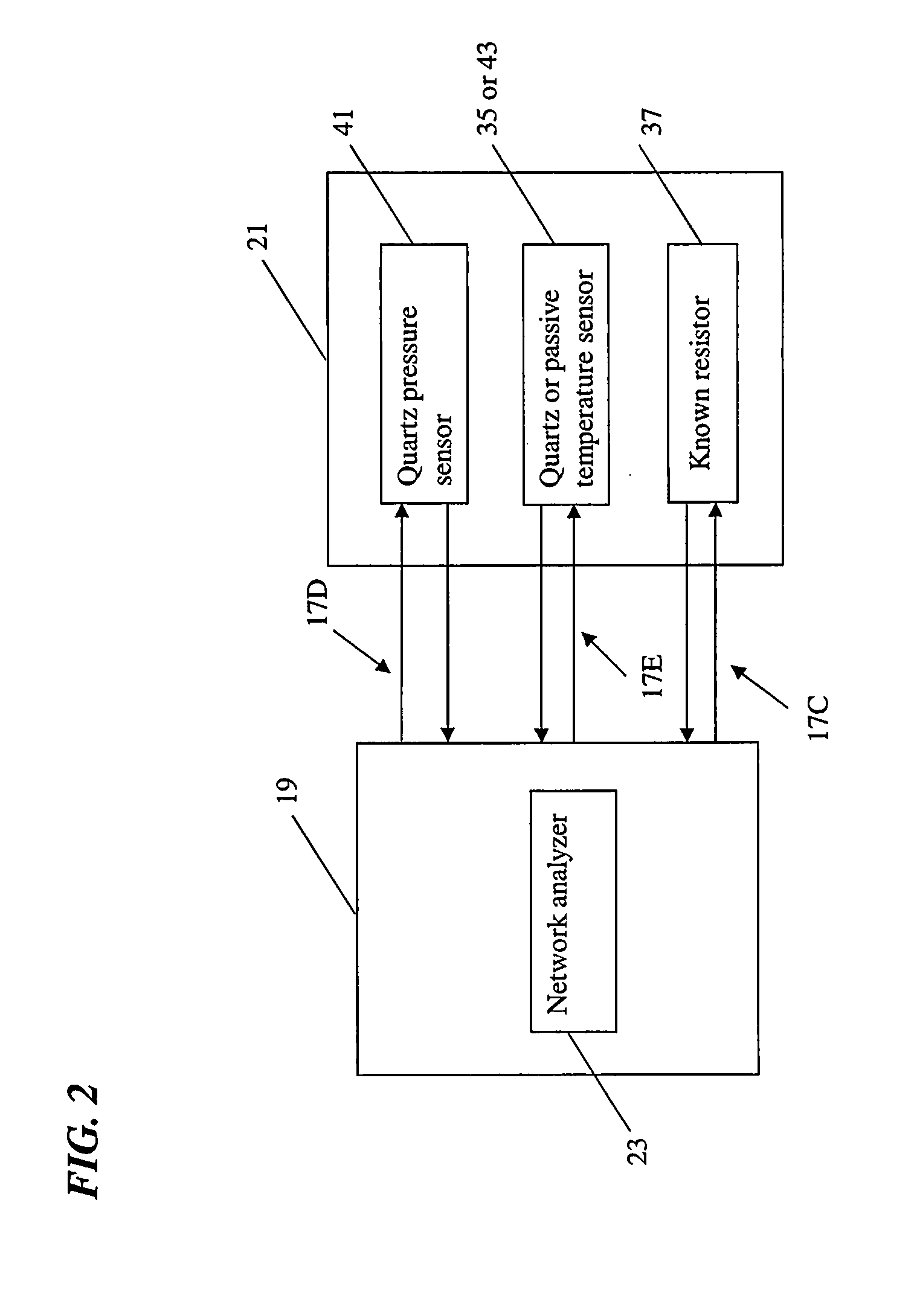

Downhole Quartz Gauge with Minimal Electronics

ActiveUS20140311235A1Limited numberImprove reliabilitySurveyConstructionsTransmission lineElectronics

A system and method of monitoring a pressure, temperature, and / or vibration of a hostile environment without requiring the use of active electronics or an oscillator circuit in that environment. The system and method interrogate a resonant pressure sensor and a resonant or passive temperature sensor connected to a transmission line and located at least 100 feet (30.48 m) away from a network analyzer. The system and method use the reflected frequencies from the sensors to determine the pressure, temperature, and / or vibration. If the sensors are networked by the transmission line or a network filter, the reflected portion can include the reflected transmission energy. The applied signal and reflected portion travel along the transmission line, which is preferably impedance matched to that of the system. If a multi-conductor cable is used, the effects of the cable's length and temperature are compensated for via a system calibration when in field use.

Owner:SERCEL INC

Hematopoietic cell phenotyping using free circulating cellular markers

The present invention provides methods of identifying cluster of differentiation (CD) marker phenotype for hematopoietic cells using multiple soluble CD markers circulating in bodily fluid. In particular aspects, the CD marker phenotype can be used to classify the tumor type of a patient having a proliferative disorder. In other aspects, treatment and disease progression can be monitored by measuring the levels of CD markers in bodily fluids of a patient over time.

Owner:QUEST DIAGNOSTICS INVESTMENTS INC

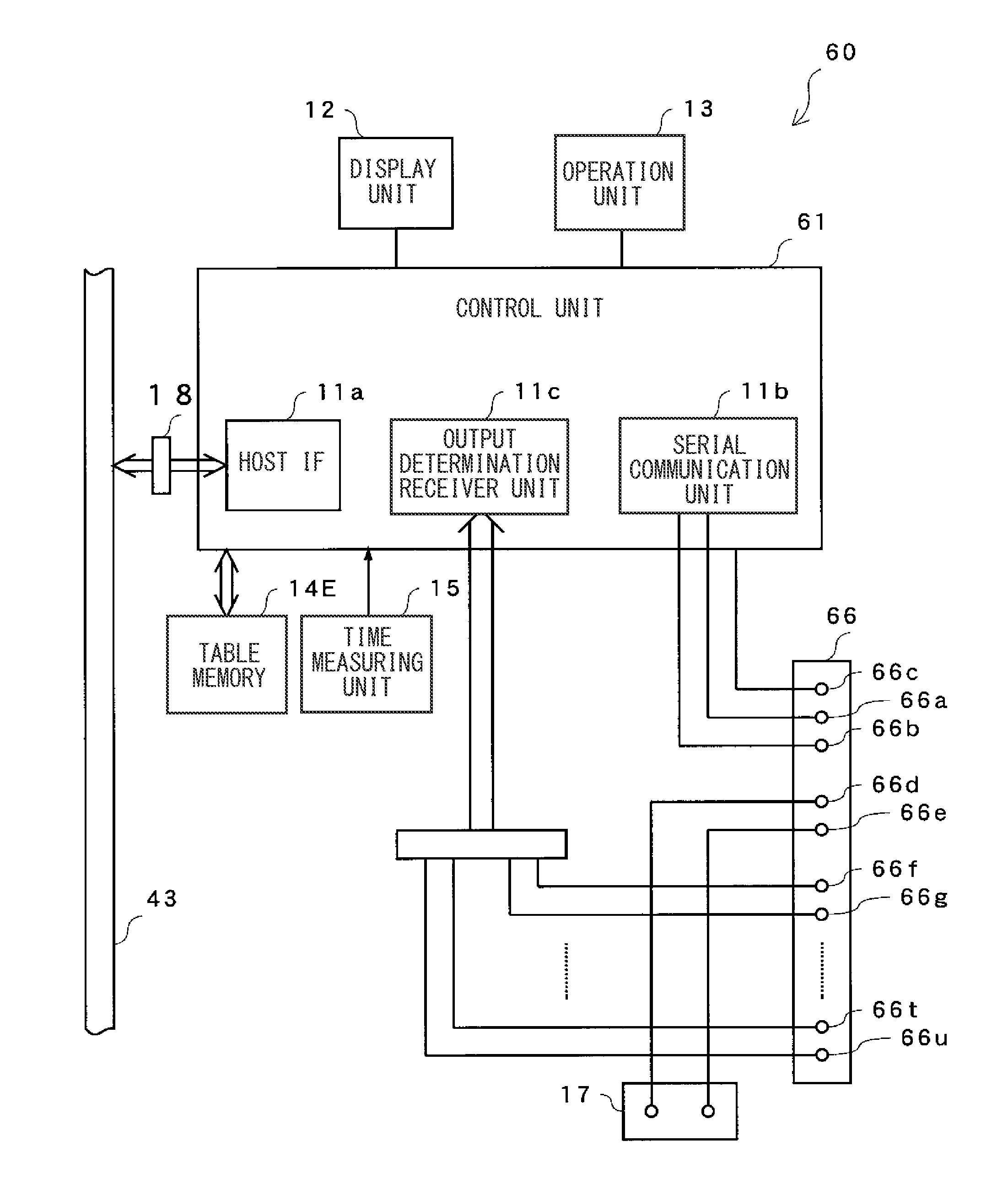

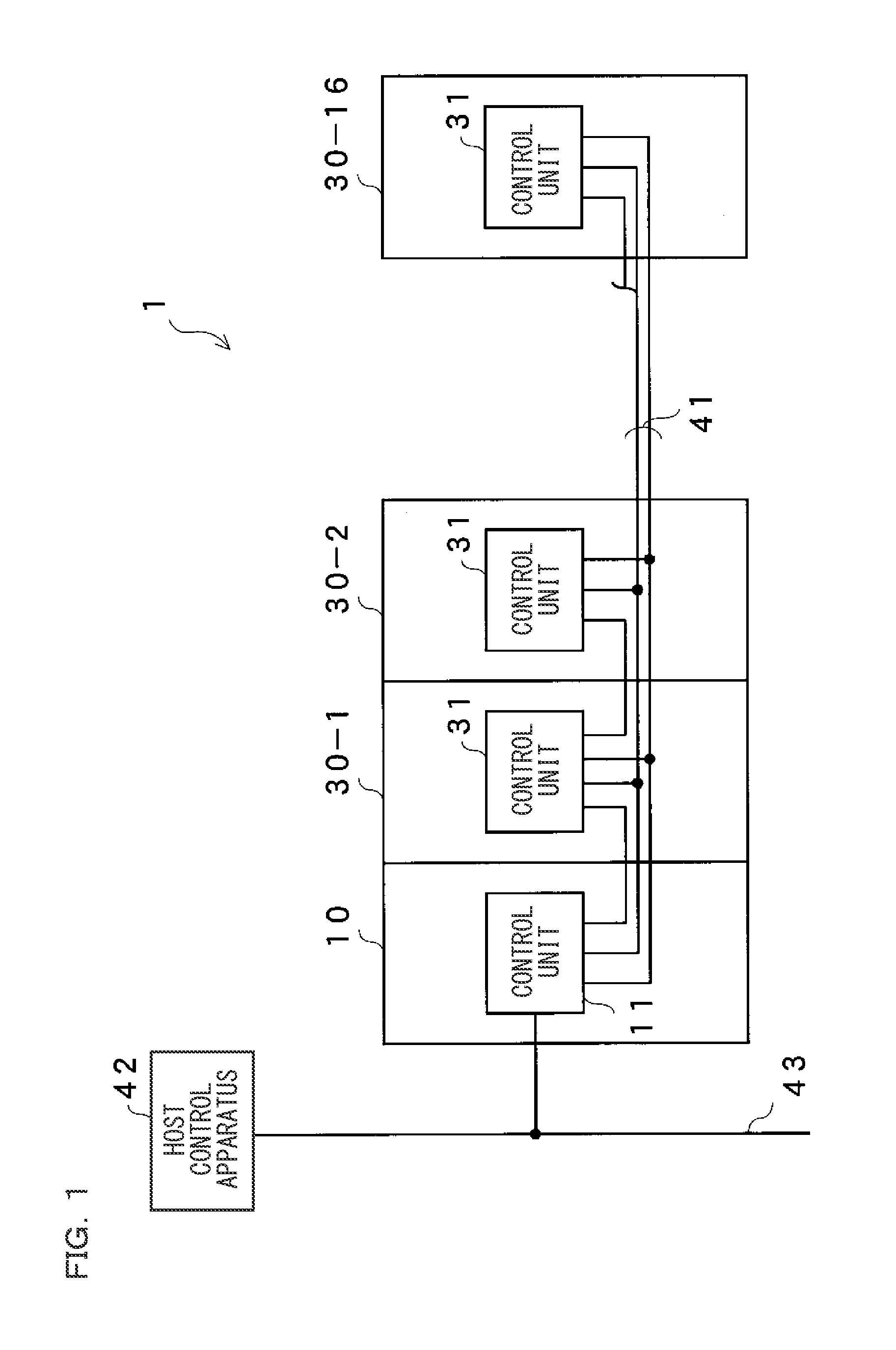

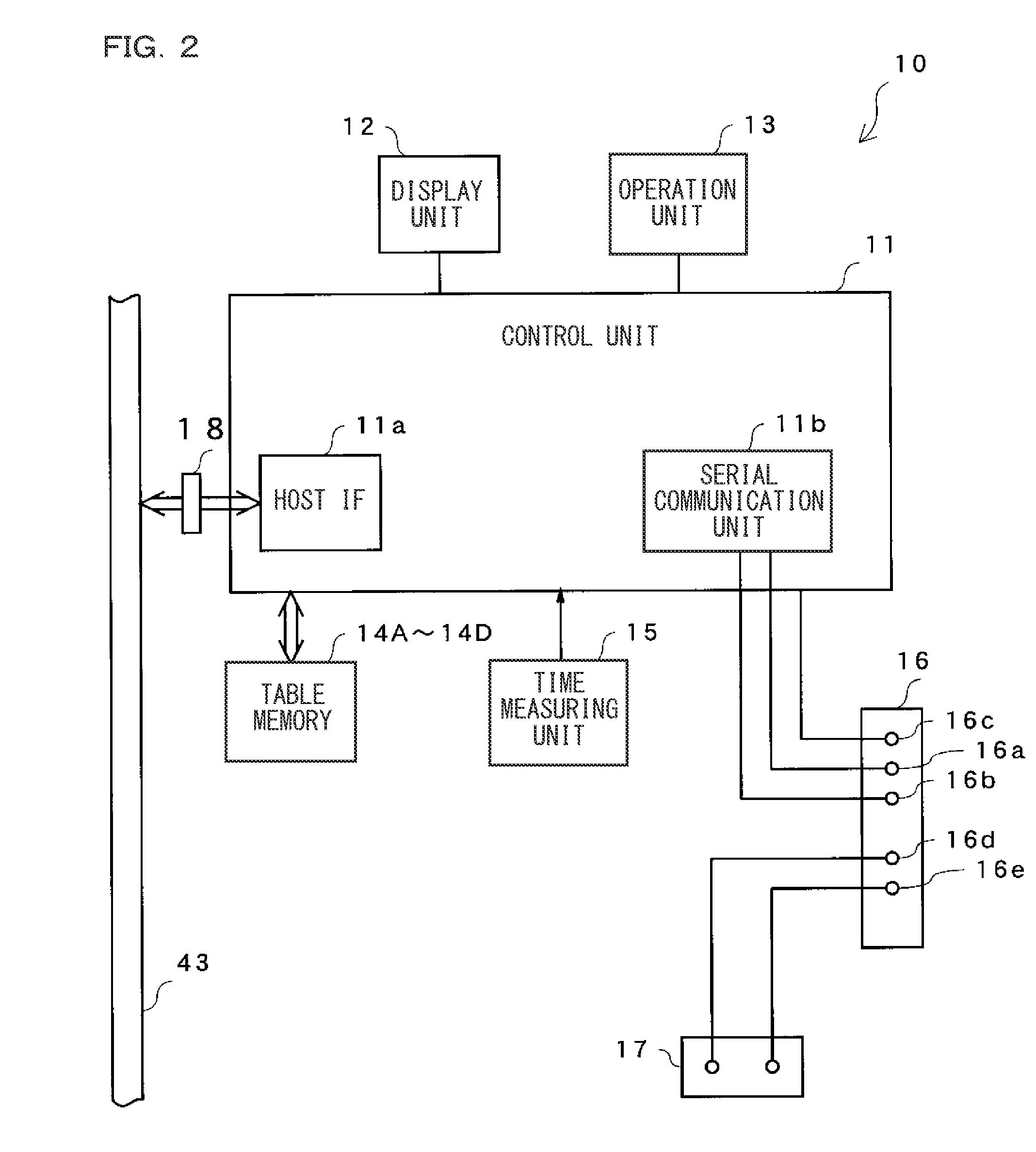

Continuously-Arranged Sensor System, Network Unit, and Sensor Unit

InactiveUS20100185418A1Limited numberTime obtainedError detection/correctionDigital computer detailsTransmission lineEngineering

A continuously-arranged sensor system is provided that can recognize a time of a determination signal provided by each sensor unit so that a host control apparatus can use the time to perform timing control. The continuously-arranged sensor system includes a network unit and a plurality of sensor units, which are connected by a serial transmission line. In accordance with a command sent from the network unit, each sensor unit transmits the determination signal to the network unit via the serial transmission line. The network unit stores the time information and the determination information to a table memory.

Owner:KEYENCE

Methods and apparatus for reducing data capture and storage requirements for call and transaction related message monitoring and fraud detection

InactiveUS20060233316A1Limited numberReduce the amount requiredMultiplex system selection arrangementsSupervisory/monitoring/testing arrangementsInformation fieldReal-time computing

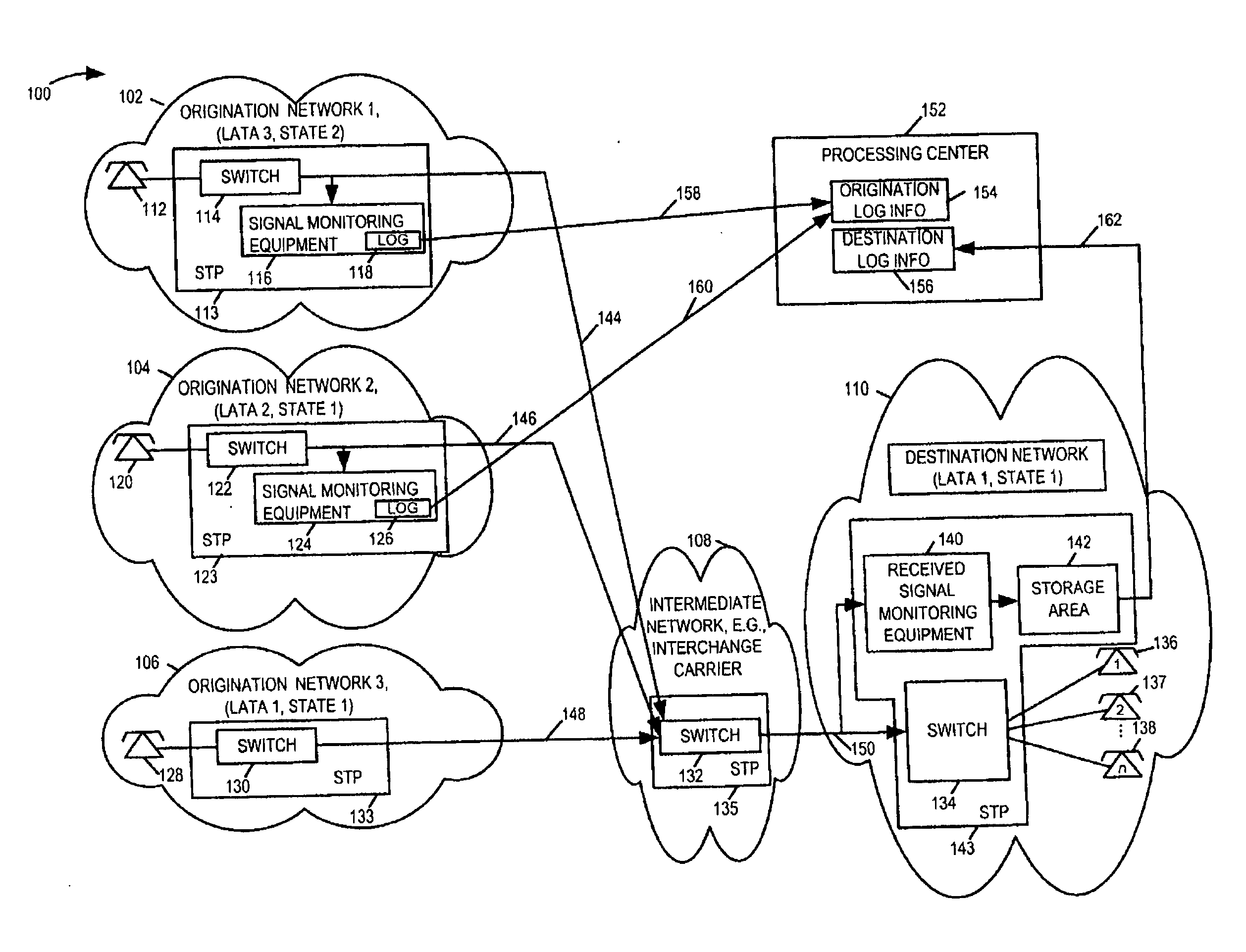

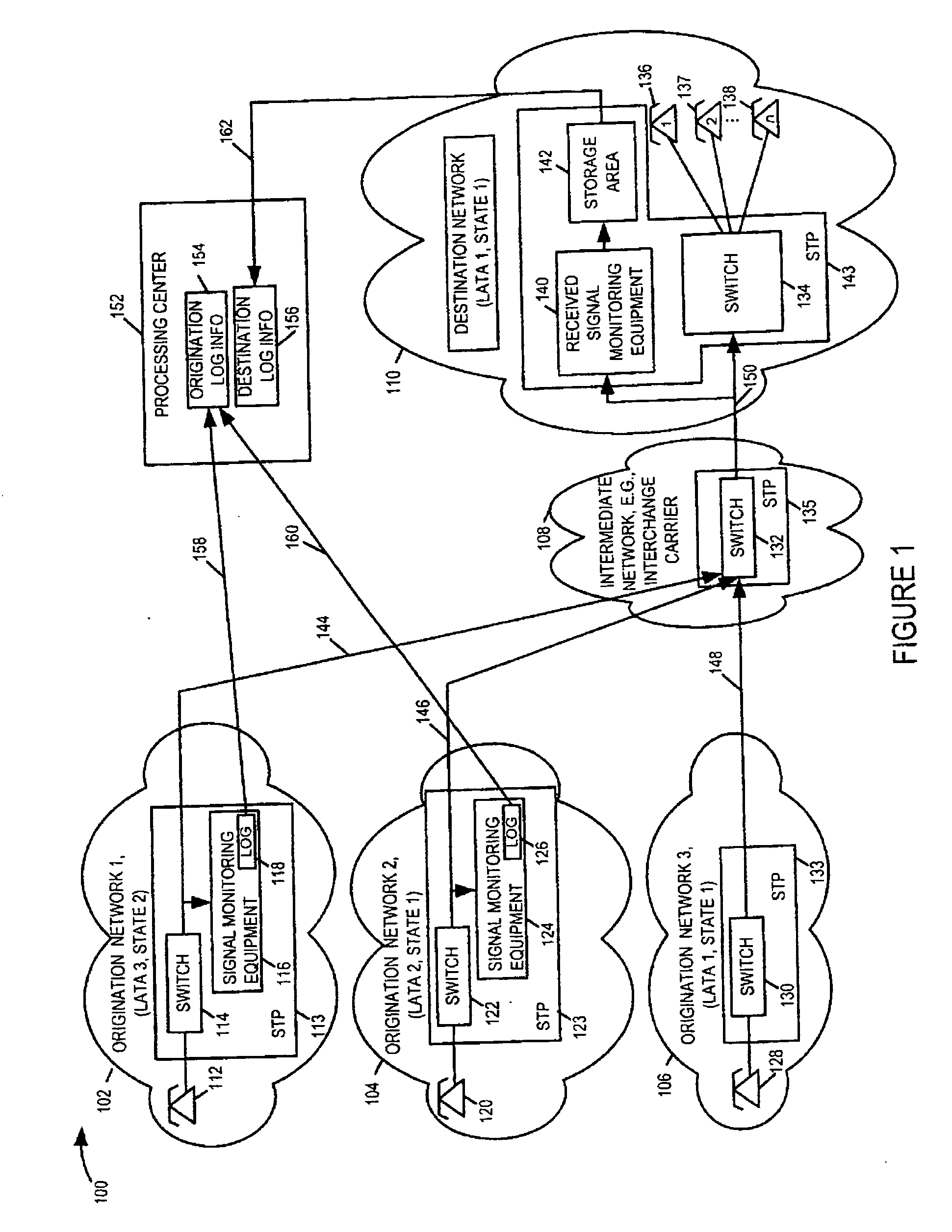

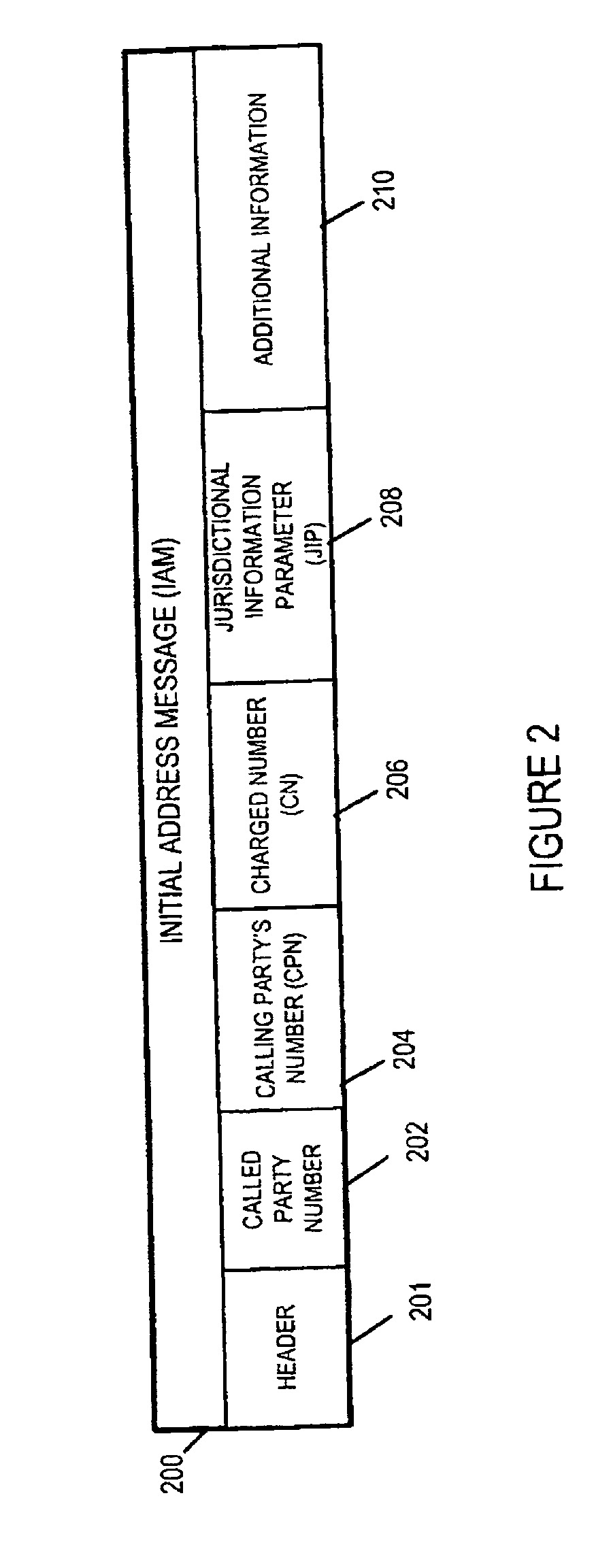

Systems for monitoring, storage, and analysis of information in signaling messages, communicated from originating networks to a destination network through one or more intermediate networks are described. Correlation and comparison between signaling messages of interest sent from an origination network to signaling messages received by the destination network allows for the detection of inconsistent information, e.g., information fields in a communicated message that have been altered, either intentionally or unintentionally, by an intermediate carrier. The introduction of an additional communications path over which notification messages are forwarded from signaling monitoring equipment in the origination network to signaling monitoring equipment in the destination network allows for a significant reduction in the memory storage requirements at the destination network and in the amount of processing required to match, compare, and evaluate signaling messages. In addition, the reduction in stored messages and processing time allows the monitoring system to operate in near-real time allowing for fraud detection while a call is still in progress.

Owner:VERIZON PATENT & LICENSING INC

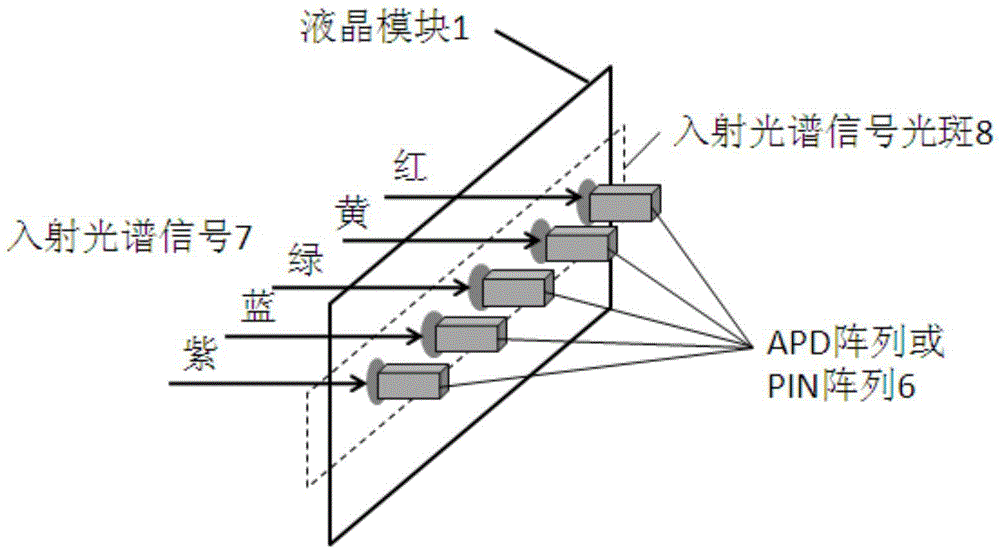

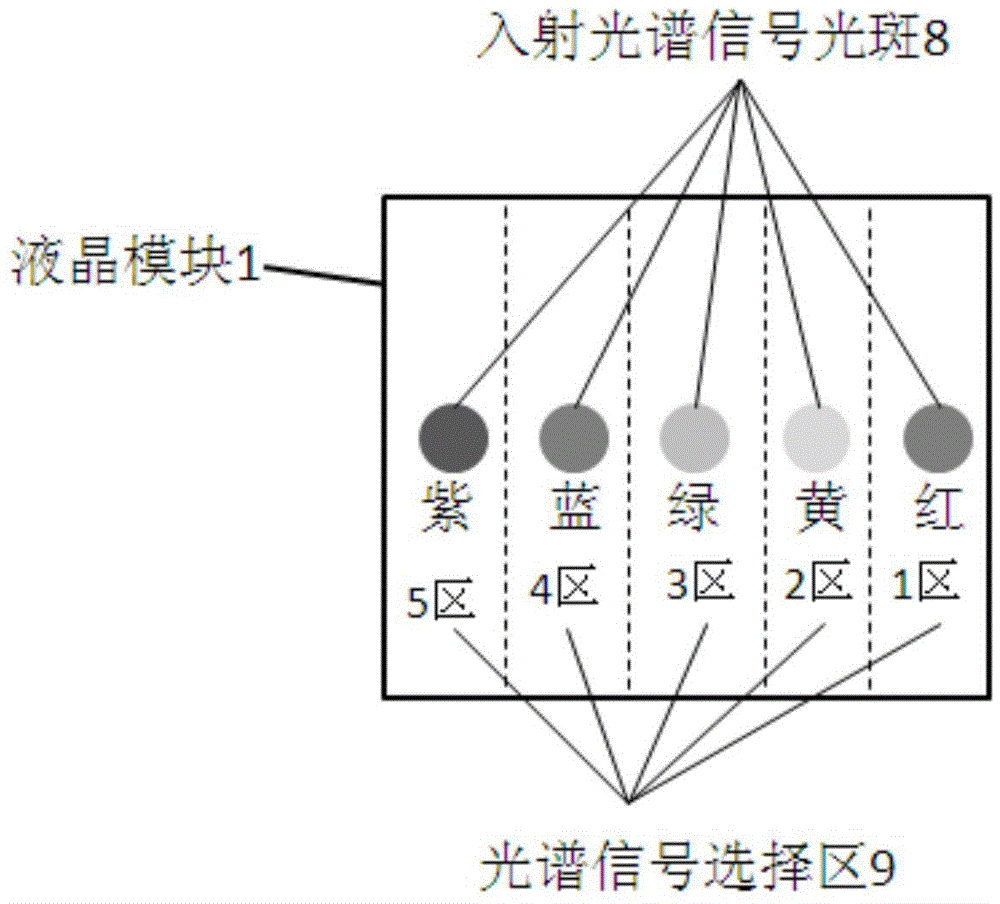

Multichannel spectral signal channel selection and reception system used for wireless optical communication

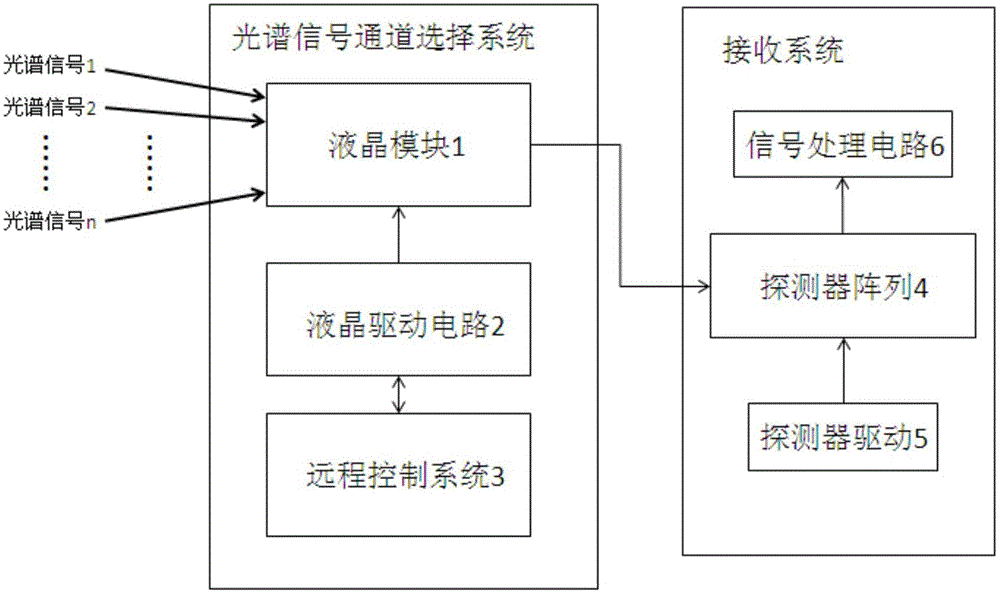

InactiveCN104410449AReduce crosstalkGuarantee the validity of the signalFree-space transmissionSignal processing circuitsControl system

The invention discloses a multichannel spectral signal channel selection and reception system used for wireless optical communication. The multichannel spectral signal channel selection and reception system comprises a spectral signal channel selection system and a reception system, wherein the spectral signal channel selection system comprises a liquid crystal module, a liquid crystal drive circuit and a remote control system; and the reception system comprises a detector array, a detector drive and a signal processing circuit. The multichannel spectral signal channel selection and reception system used for wireless optical communication is mainly used for the wireless optical communication, and is capable of implementing selection and reception of optical communication signals at a plurality of spectrum sections by adopting liquid crystal devices and carrying out selection and reception on multichannel single spectral signals for space division multiplexing.

Owner:BEIJING INSTITUTE OF TECHNOLOGYGY

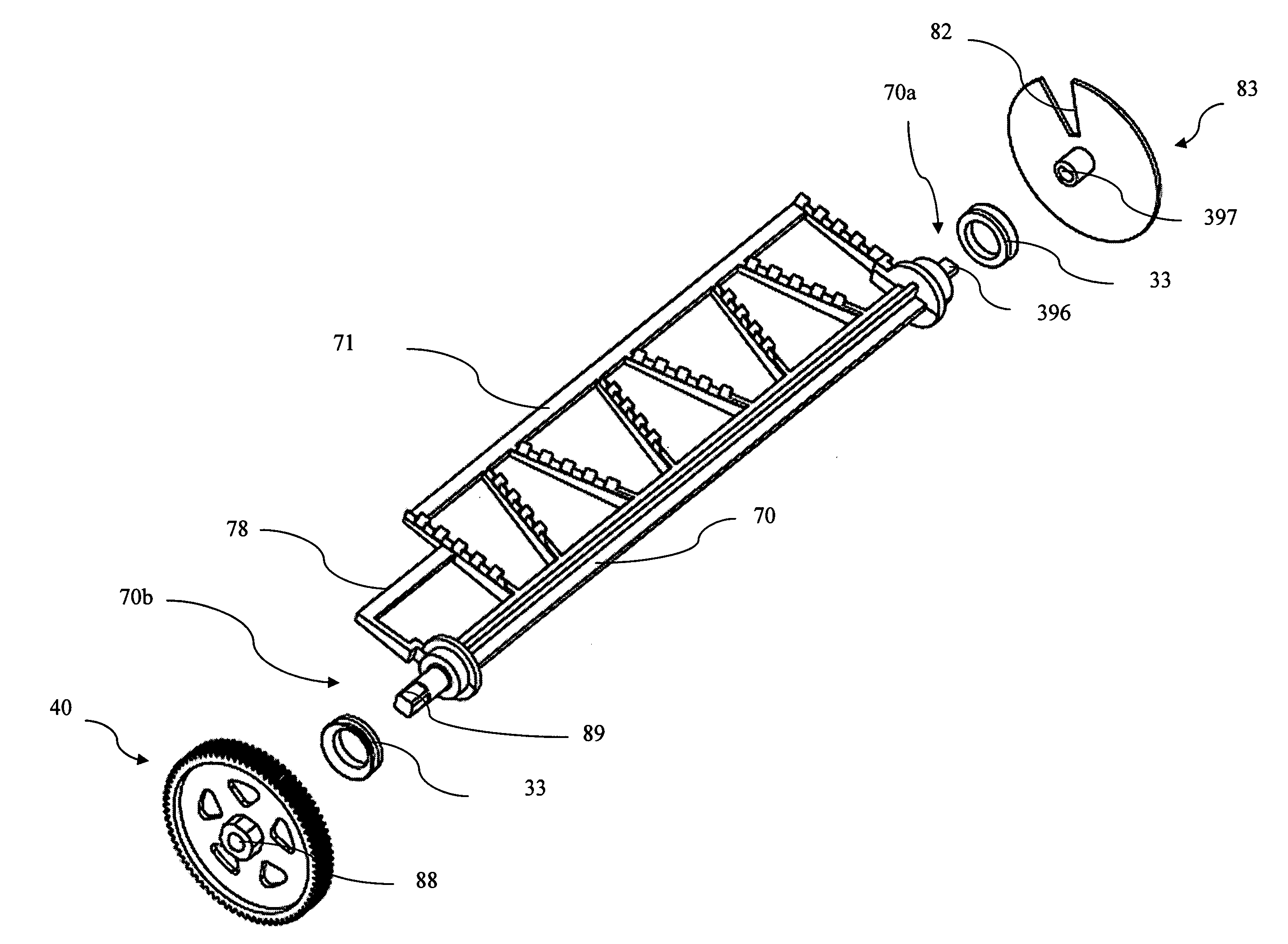

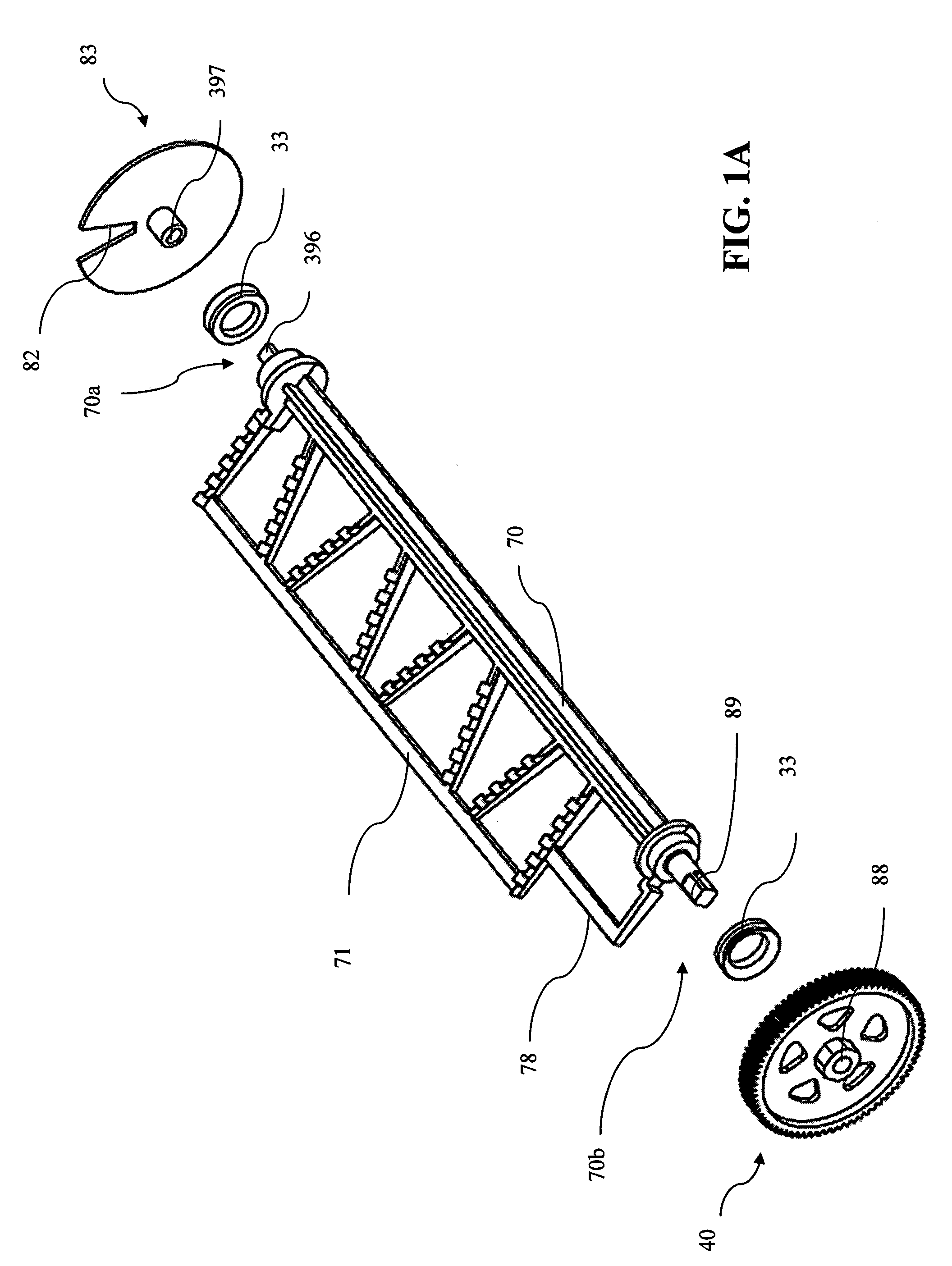

Rigid agitator and shaft assembly

InactiveUS7174123B1Limited numberEasy constructionElectrographic process apparatusEngineeringMechanical engineering

A toner cartridge includes a waste bin and hopper designed with a rigid agitator assembly. A non-yieldable agitator is mounted on a shaft whereby the rotation of the shaft results in the synchronous rotation of the agitator. As the shaft rotates, the agitator enters into, through, and out of engagement with the toner within said toner chamber.

Owner:AMERICAN IMAGING CARTRIDGE

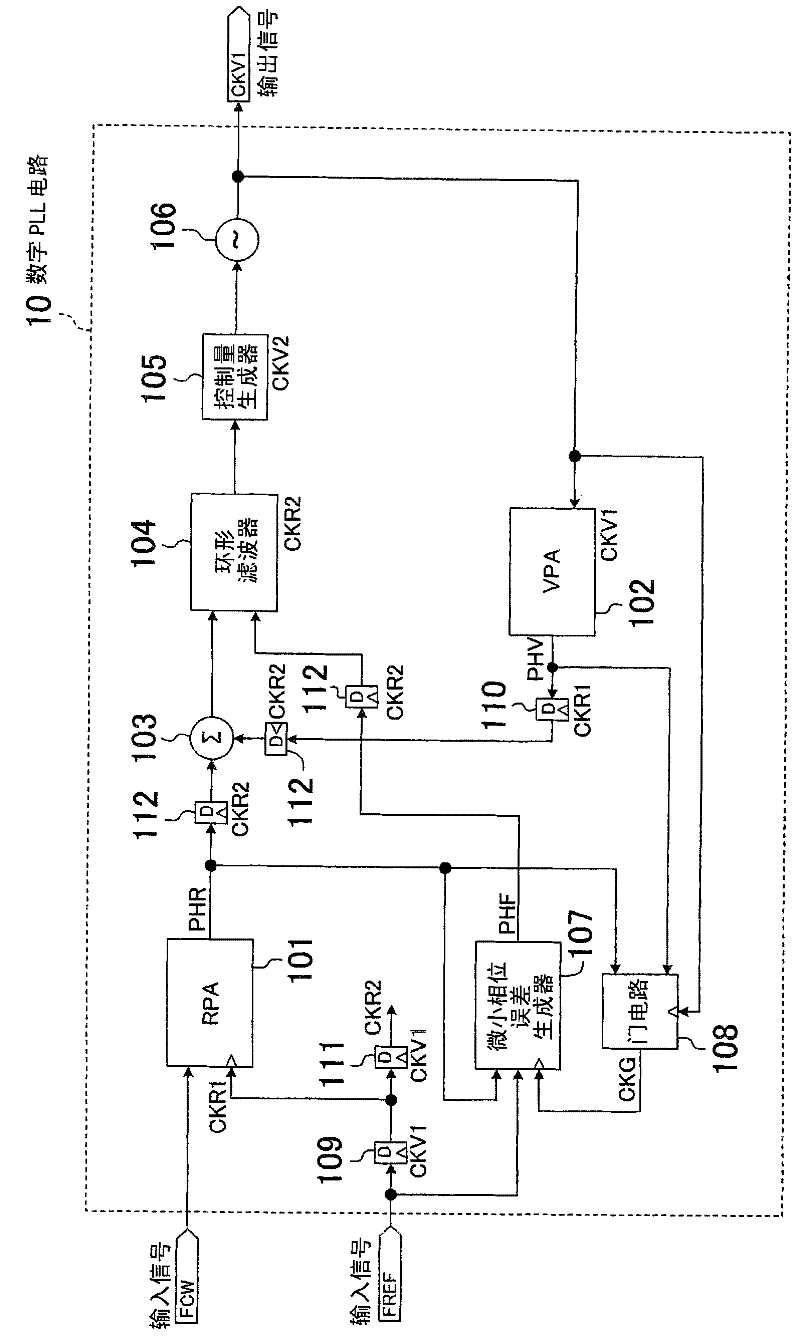

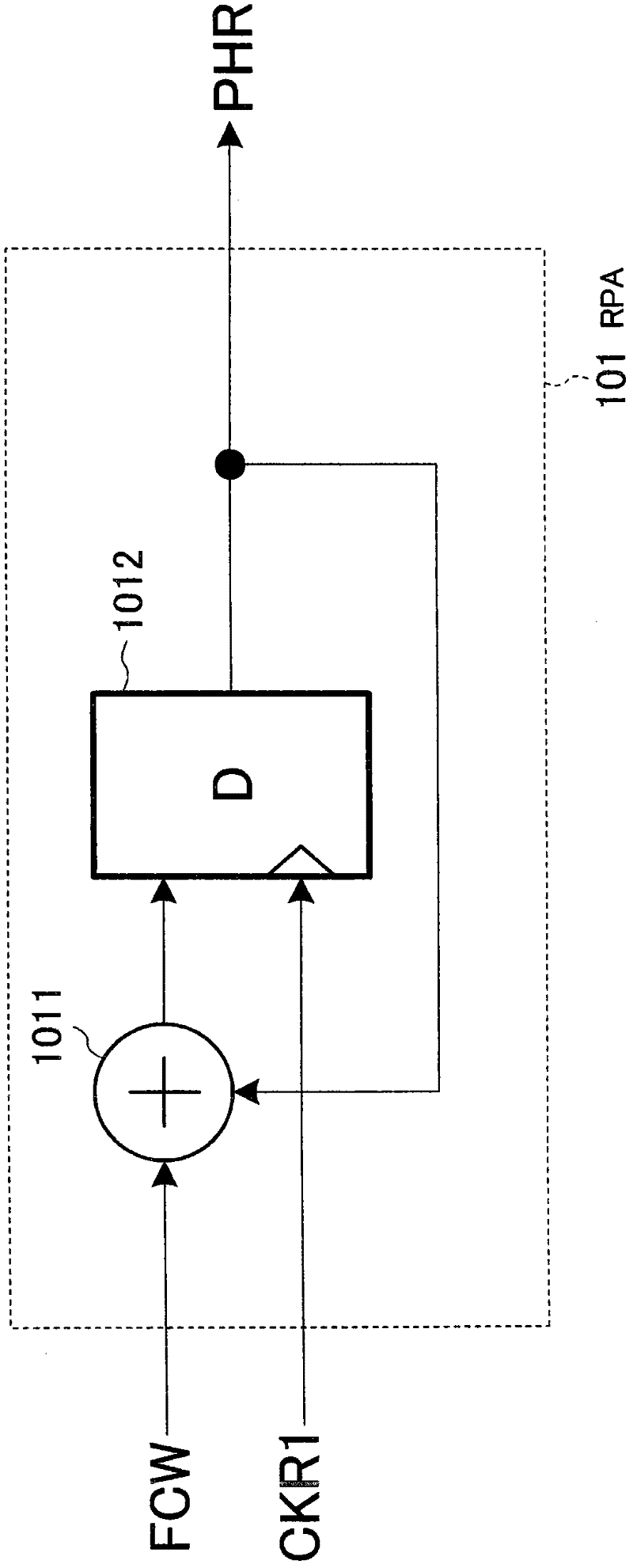

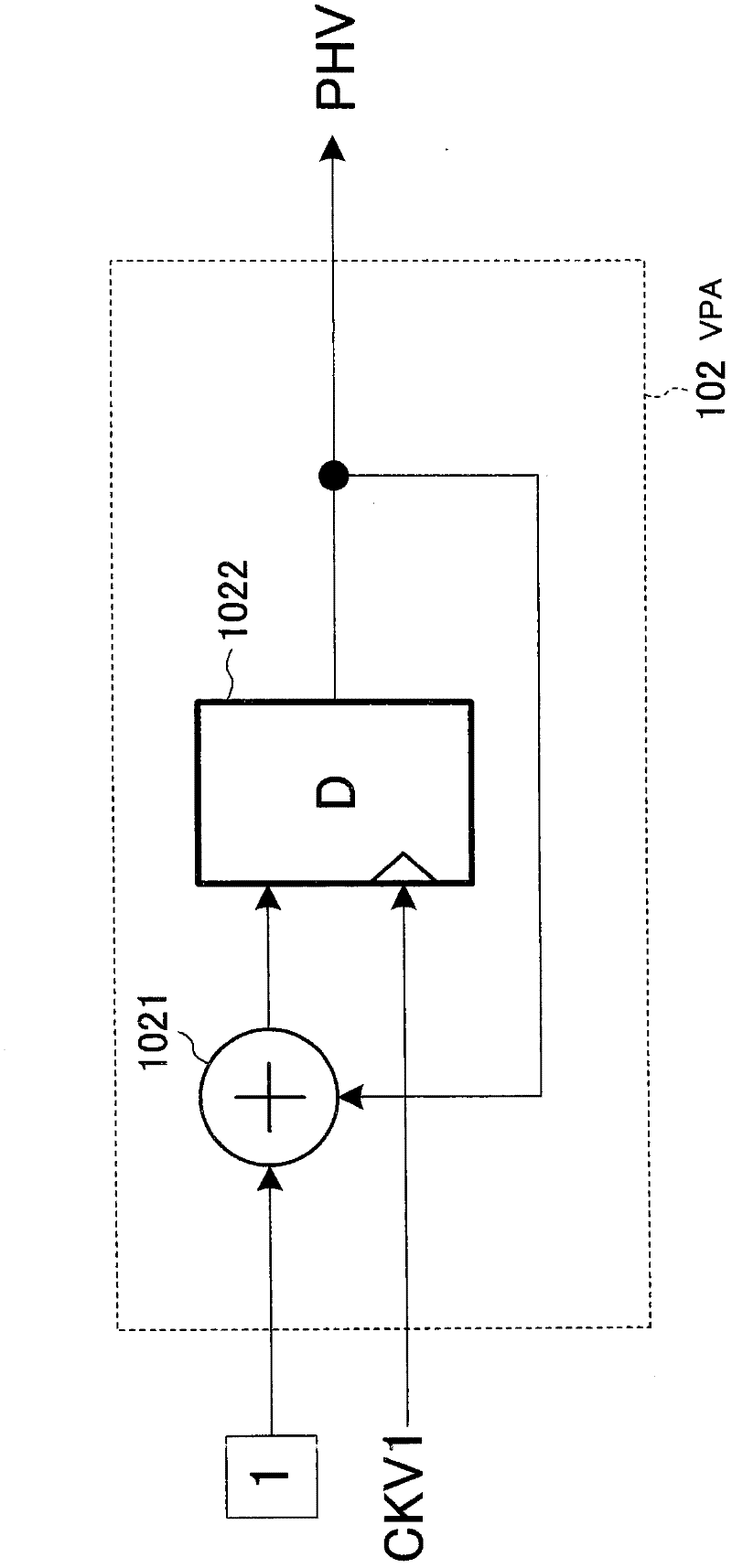

Digital pll circuit and communication apparatus

InactiveCN102187579AReduce power consumptionGood phase noise characteristicsPulse automatic controlVIT signalsFrequency ratio

A digital PLL circuit for providing as an output a clock signal having a frequency obtained by multiplying the frequency of a reference signal by a frequency control word (frequency ratio). In the digital PLL circuit, an RPA circuit (101) sequentially adds frequency control words (FCW) each having a decimal component. An output from the RPA circuit (101) is supplied to a micro-phase-error generator (107), which generates, based on the decimal part of the sequentially added value of the frequency control words (FCW), a plurality of threshold values in the vicinity of the actual amplitude value of a reference signal (REF), and which then calculates, based on these threshold values, an amplitude value of the reference signal (REF) and also calculates a phase error of the reference signal (REF) in accordance with the calculated amplitude value, and which further calculates a micro-phase-error between the reference signal (REF) and an output clock (CKV1). Thus, even if the frequency control words include decimal components, the residual micro-phase-error between the reference signal and the output clock can be calculated and corrected in a smaller area and with a less power consumption.

Owner:PANASONIC CORP

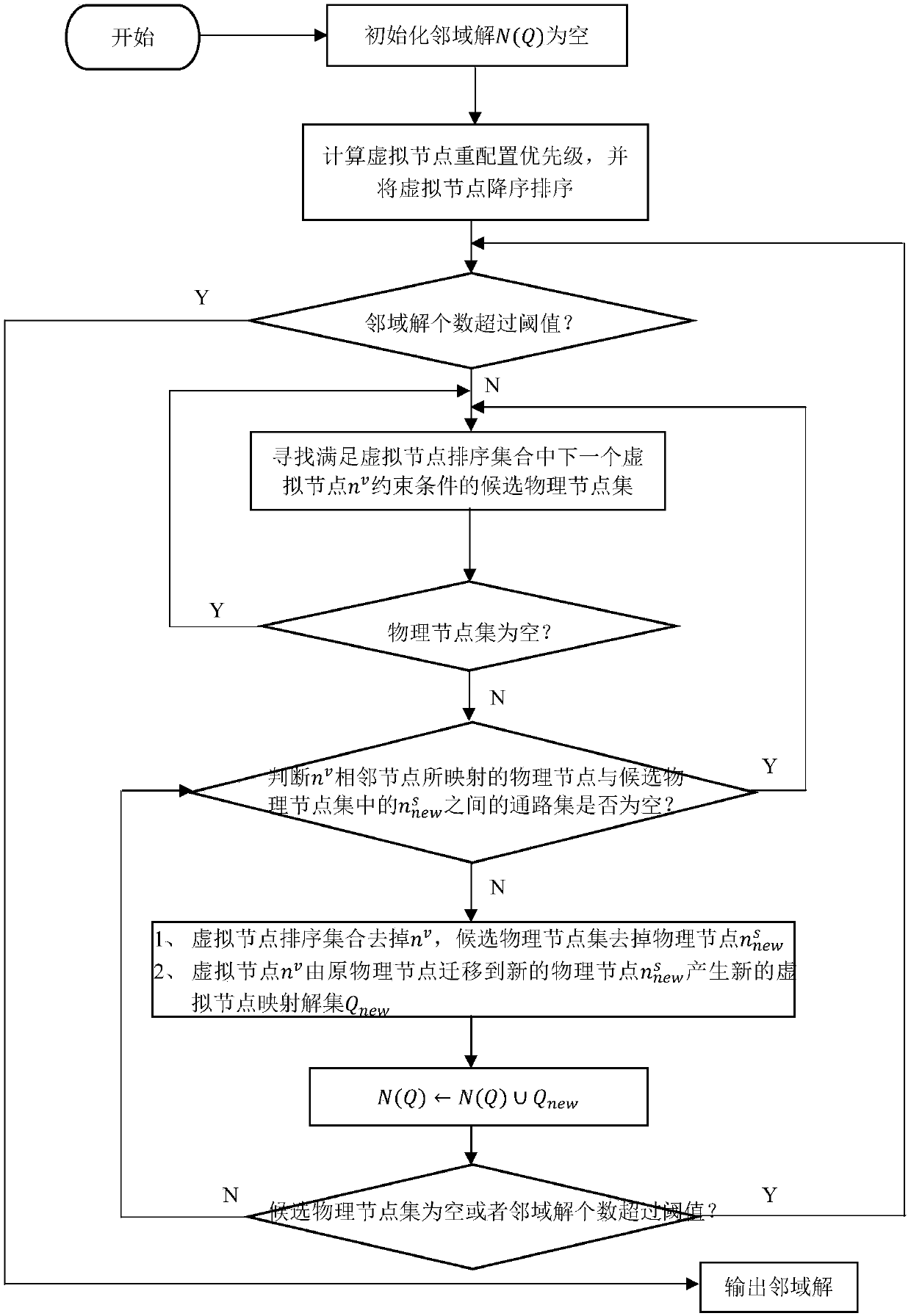

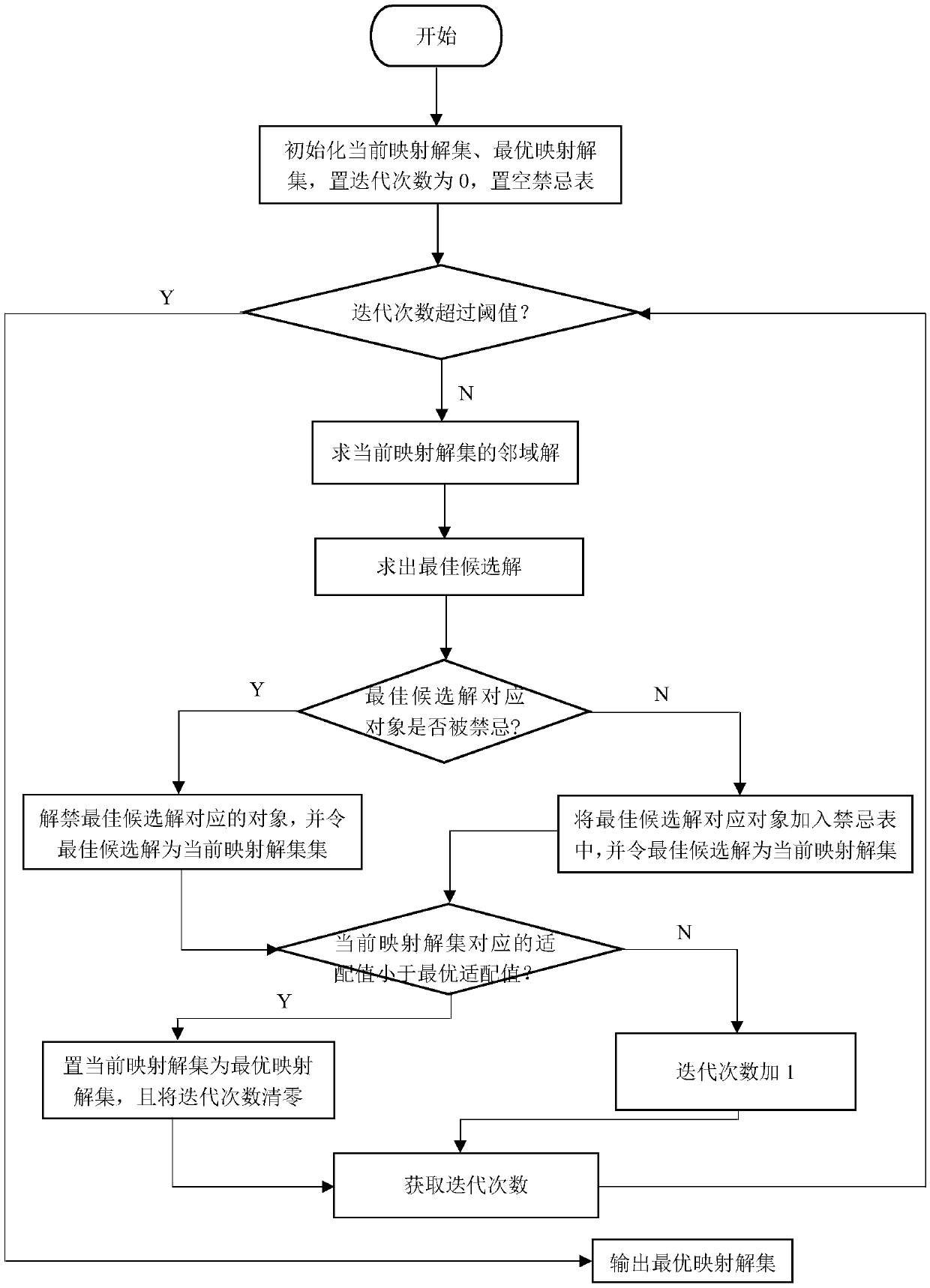

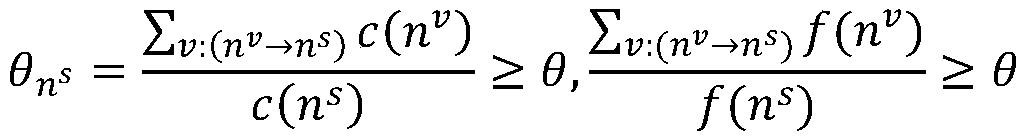

SDN-oriented virtual network reconfiguration method based on taboo search

ActiveCN108833295AIncrease acceptance rateReduce in quantityData switching networksSoftware simulation/interpretation/emulationTabu searchGlobal optimal

A SDN-oriented virtual network reconfiguration method based on taboo search is provided. The method comprises determining the reconfiguration priority of a virtual node when a virtual network leaves and a physical network includes a [theta]-crowded physical node or physical link; determining the adaptive value function of a taboo search algorithm and obtaining the optimal solution of virtual network reconfiguration by optimizing the adaptive value function; finally, determining the initial solution, the neighborhood solution, the taboo table, the aspiration criterion and the termination criterion of the taboo search algorithm, and achieving the reconfiguration of the virtual network when a constraint condition is satisfied. Compared with a conventional method, the method achieves the reconfiguration of the virtual network by the taboo search, can search for the global optimal solution, balances the physical network load, improves the acceptance rate of the virtual network, and minimizes the reconfiguration cost of the virtual network.

Owner:XI AN JIAOTONG UNIV

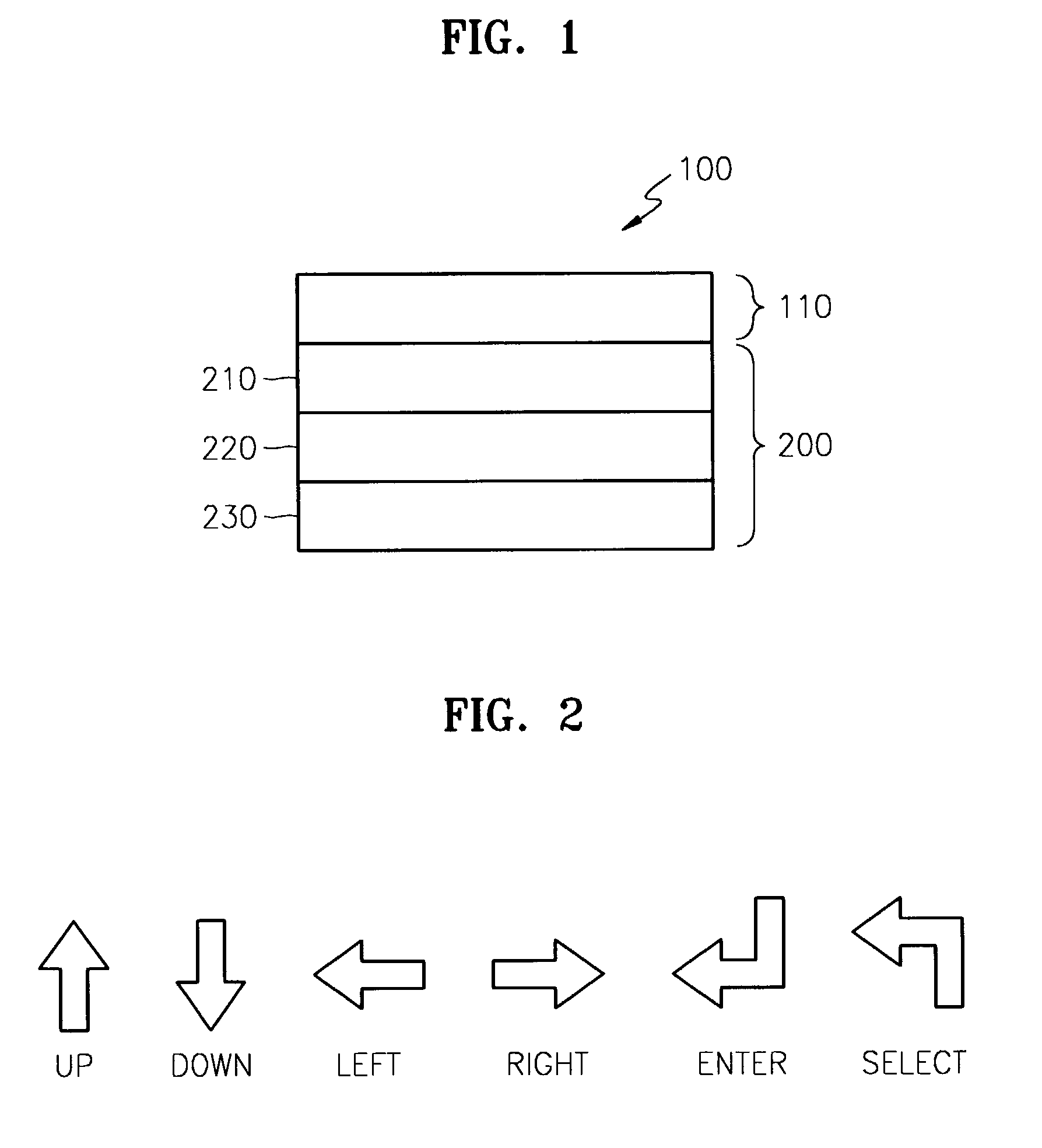

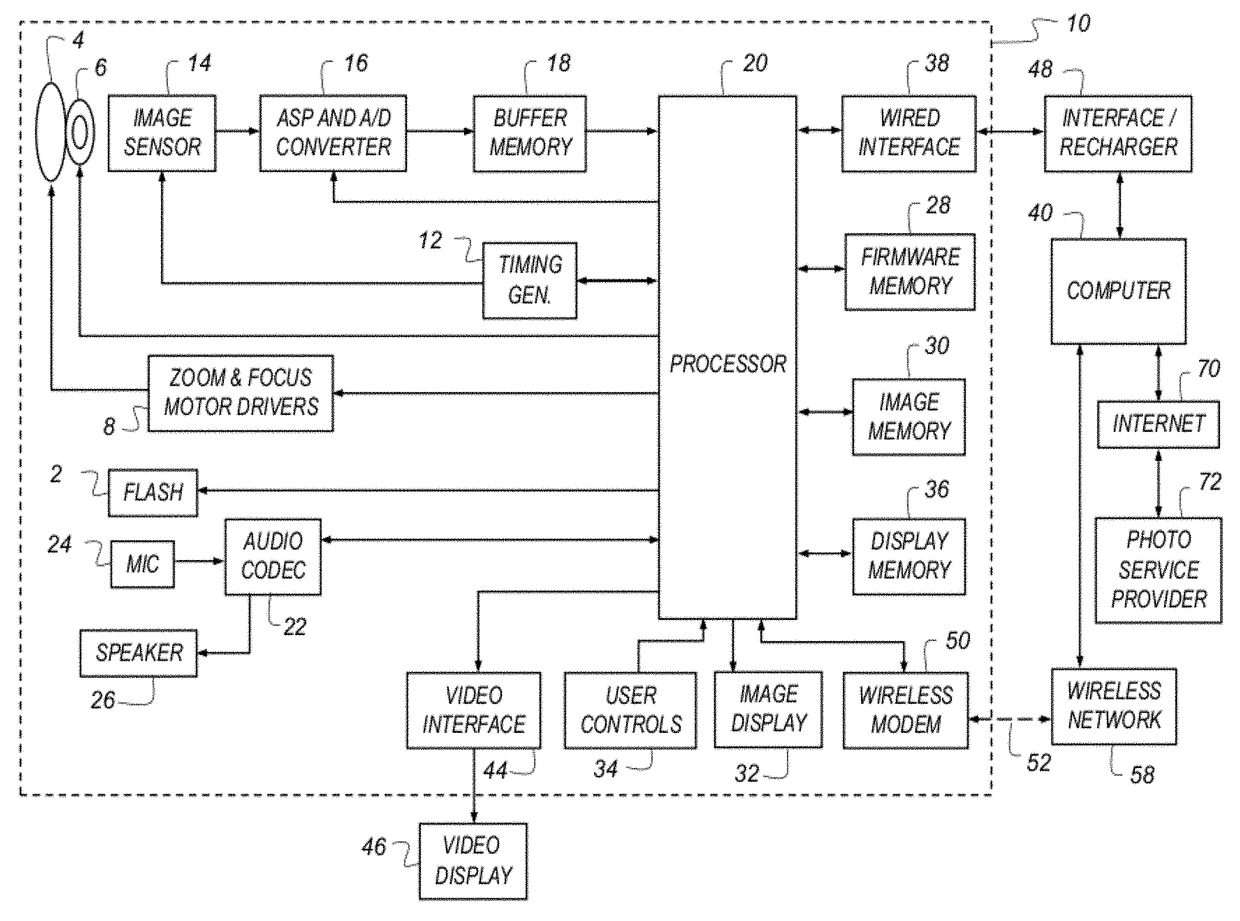

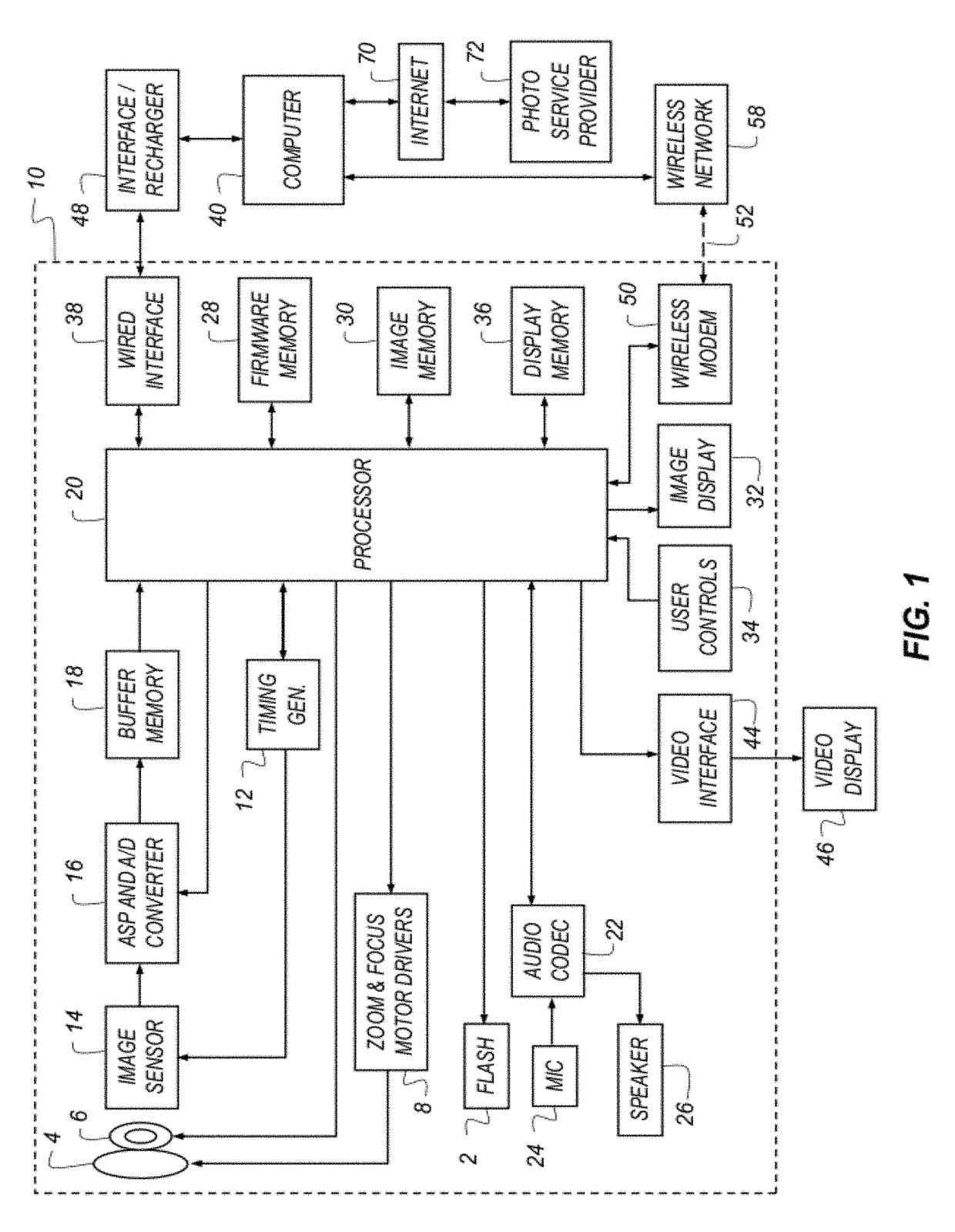

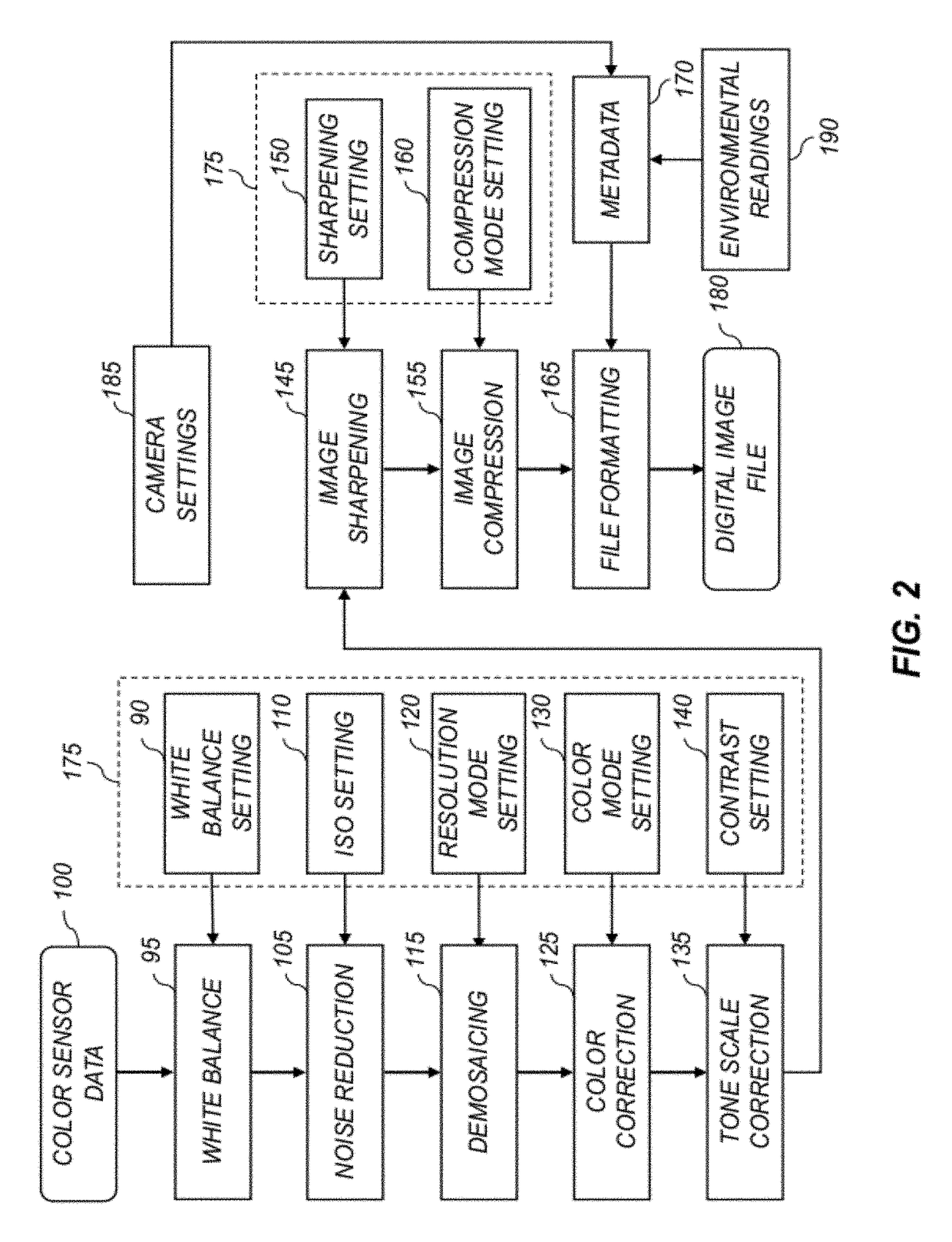

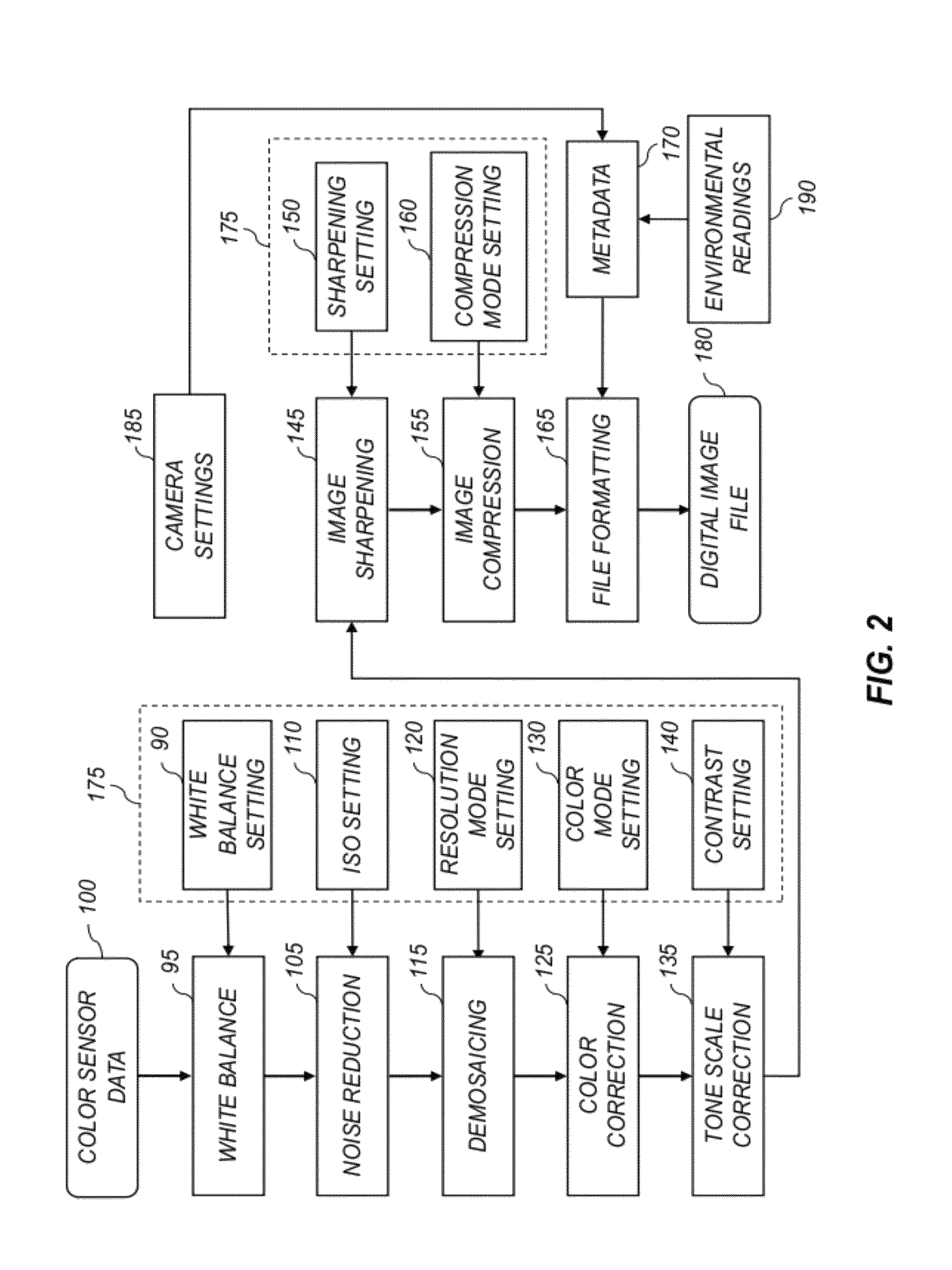

Digital camera user interface for video trimming

ActiveUS9848158B2Small displayLimited numberTelevision system detailsRecord information storageDigital videoComputer graphics (images)

A digital video camera comprising: user controls enabling a user to select between at least an up input, a down input, a left input, a right input, and a confirmation input; and a program memory storing instructions to implement a method for trimming a digital video sequence. The method includes: selecting a digital video sequence; initiating a trimming operation; accepting user input to select a start frame and an end frame for a trimmed digital video sequence, wherein the up input and the down input are used to select between a start frame selection mode and an end frame selection mode, and the left input and the right input are used to scroll through the frames of the selected digital video sequence; and trimming the selected video sequence to include the frames between the selected start frame and the selected end frame.

Owner:MONUMENT PEAK VENTURES LLC

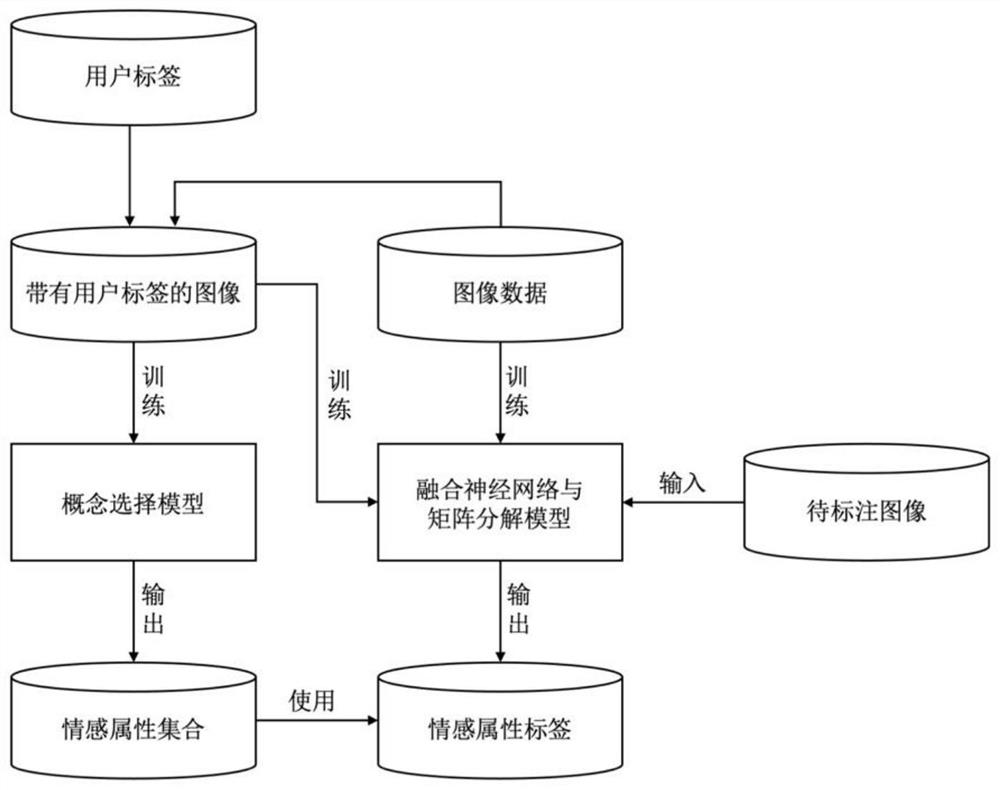

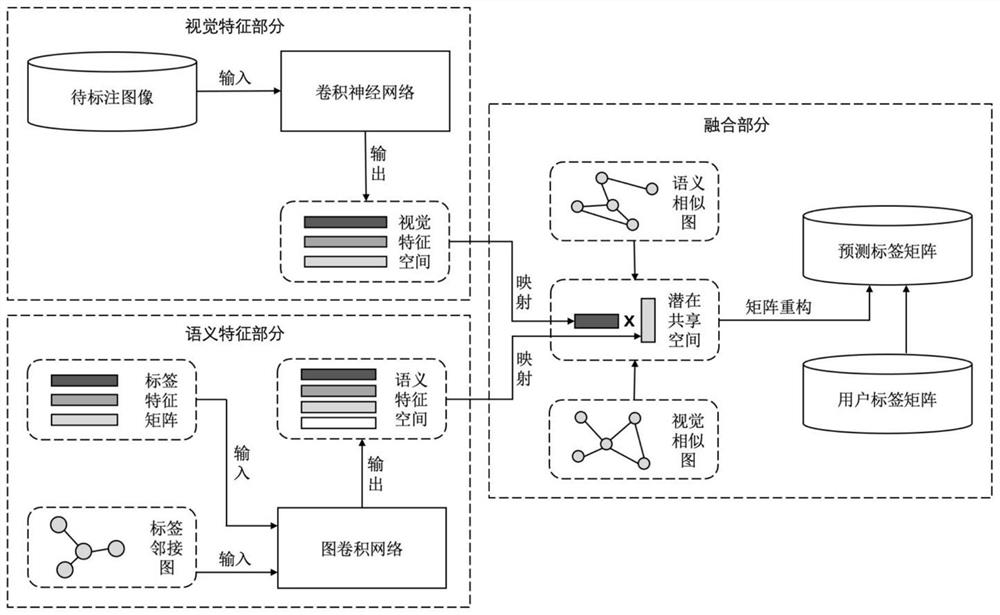

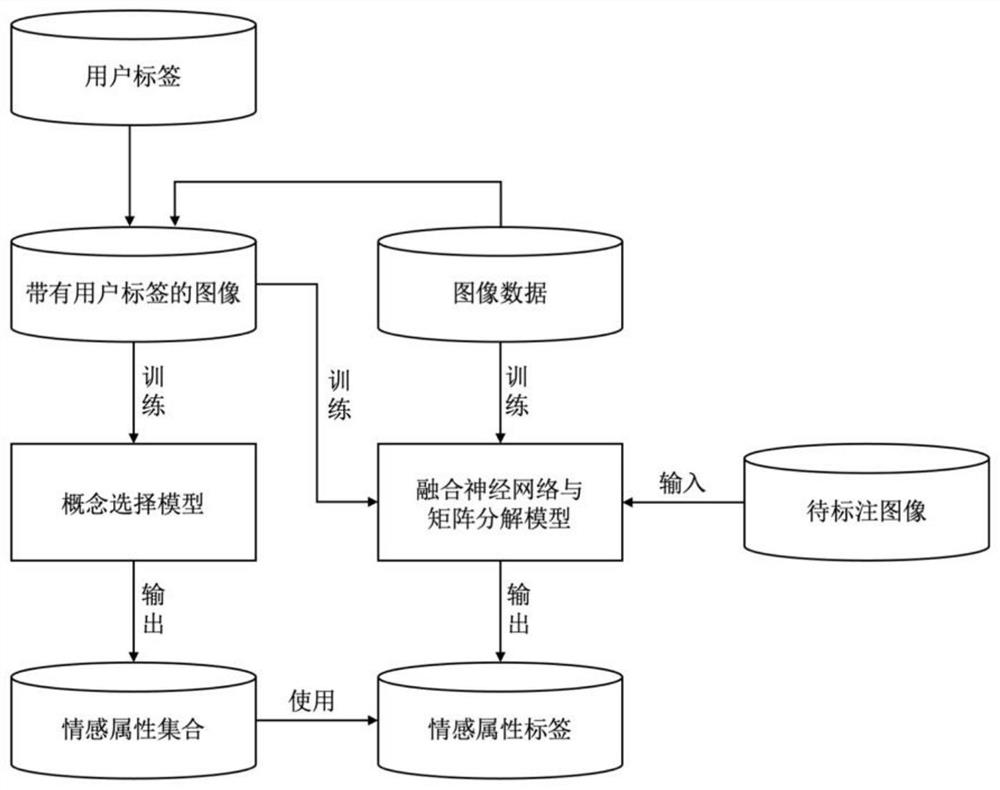

Image sentiment analysis method based on sentiment attribute mining

PendingCN114201960ALarge semantic coverageLimited numberSemantic analysisNeural architecturesMatrix decompositionContent analytics

The invention belongs to the field of image content analysis, and discloses an image sentiment analysis method based on sentiment attribute mining, which comprises the following steps: mining by using user metadata information, constructing a sentiment attribute subset with large semantic coverage and strong sentiment discriminatability, and predicting a label matrix by using a fusion neural network and a matrix decomposition model. And the accuracy and stability of an image emotion analysis result are improved. According to user tag meta-information and emotion attribute characteristics, fusing four emotion attribute characteristics and optimizing a concept selection model to complete emotion attribute subset selection; utilizing a convolutional neural network to extract visual features and performing consistency optimization through visual contents; constructing an adjacent graph guided by an external knowledge base, and performing semantic relevance optimization; mapping the image visual features and the label semantic features into a potential shared space to realize reconstruction of a prediction label matrix; and finally, reconstructing a prediction label matrix by using the trained reconstruction model, and performing final emotion recognition by using a linear classifier.

Owner:SHANGHAI UNIV

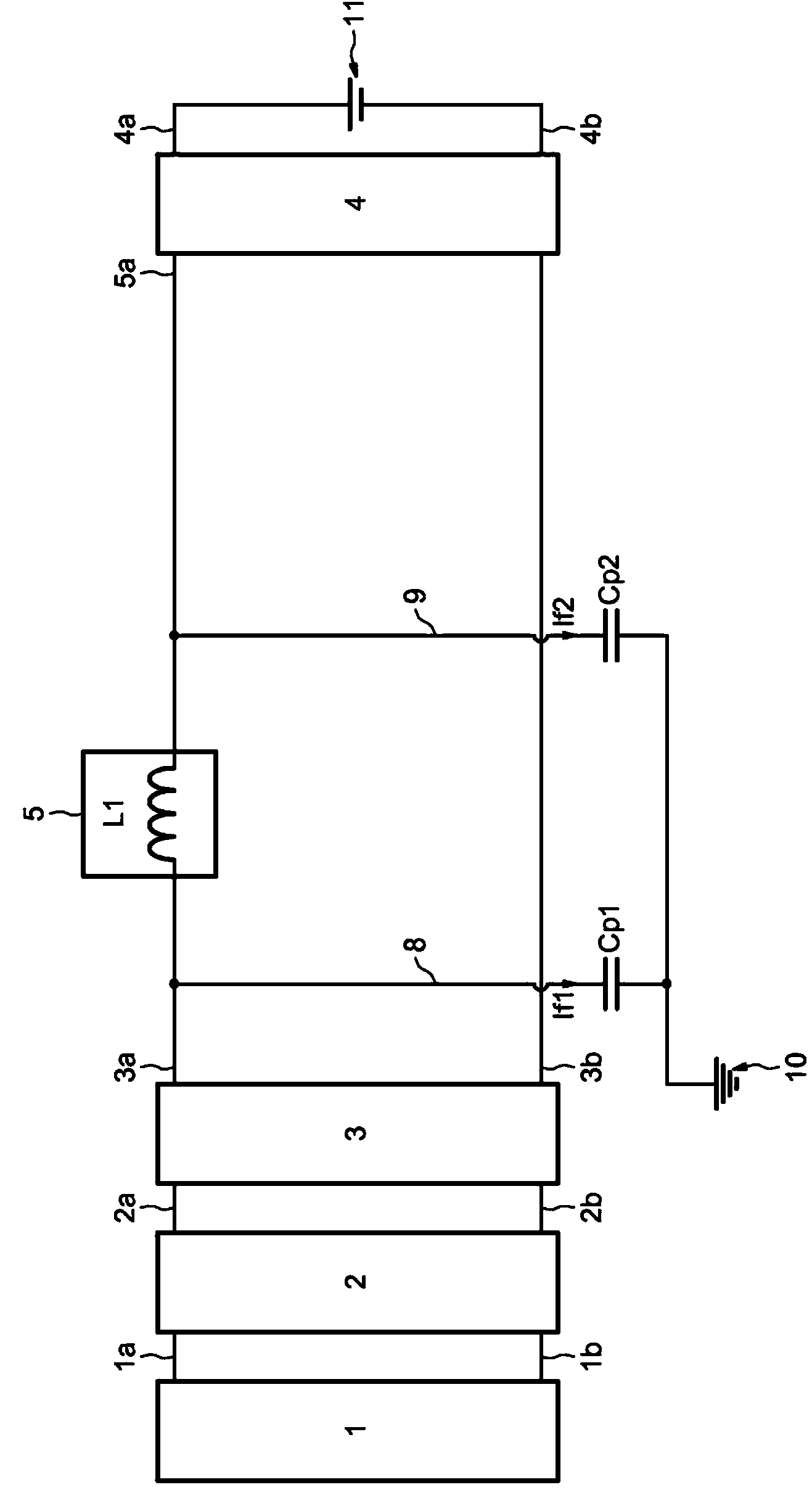

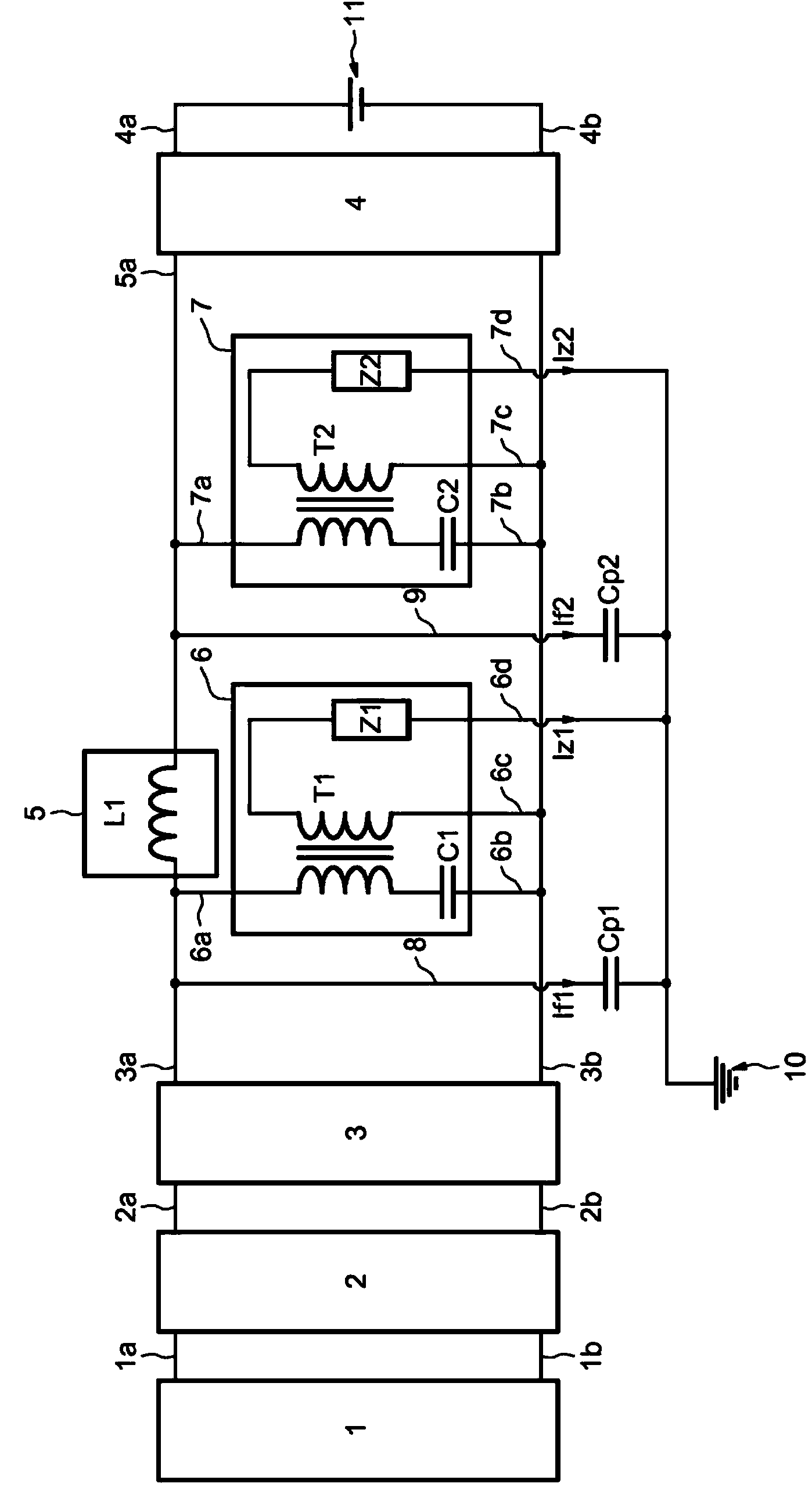

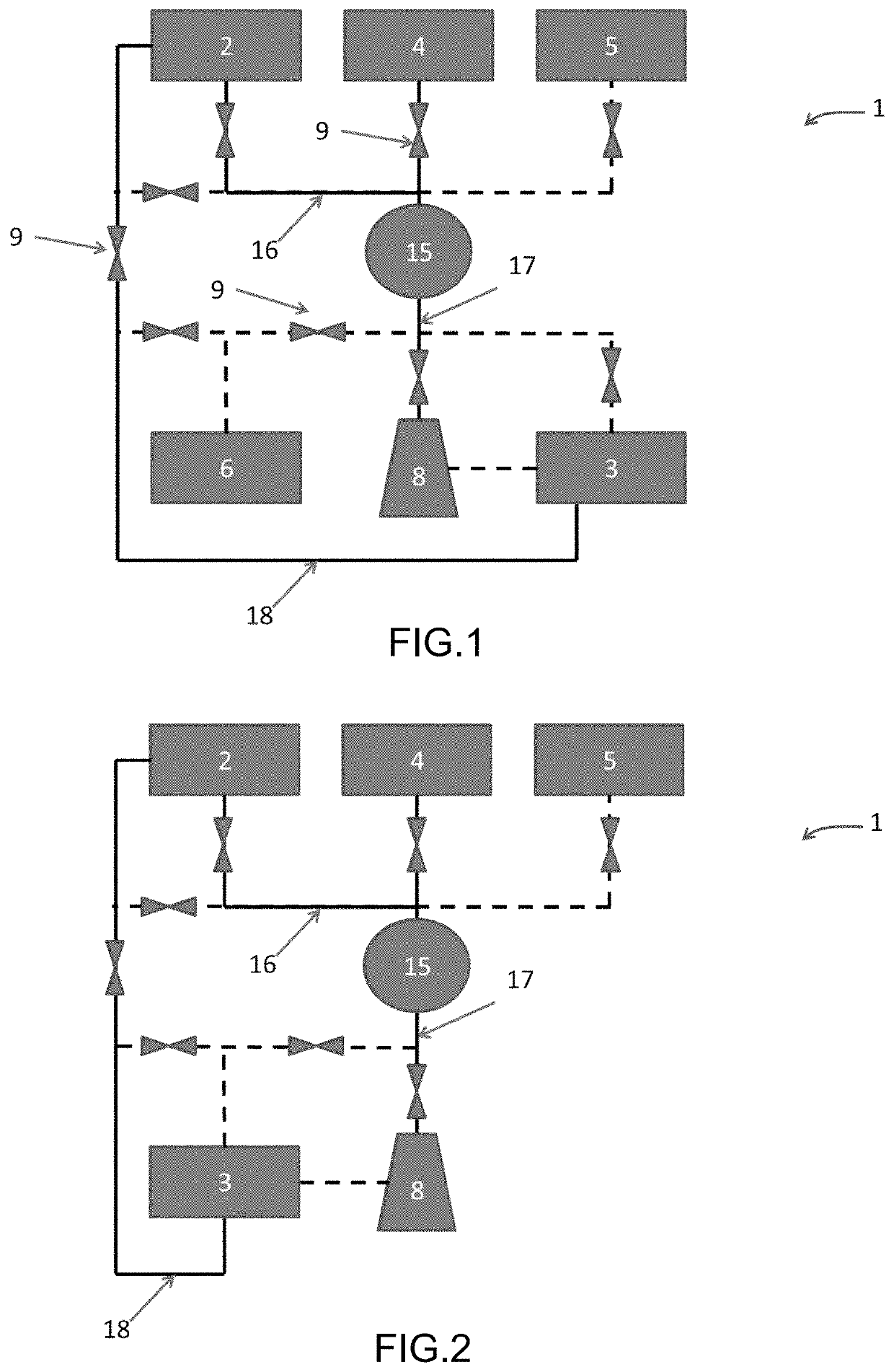

System and method for compensating for high-frequency leakage currents in a motor vehicle

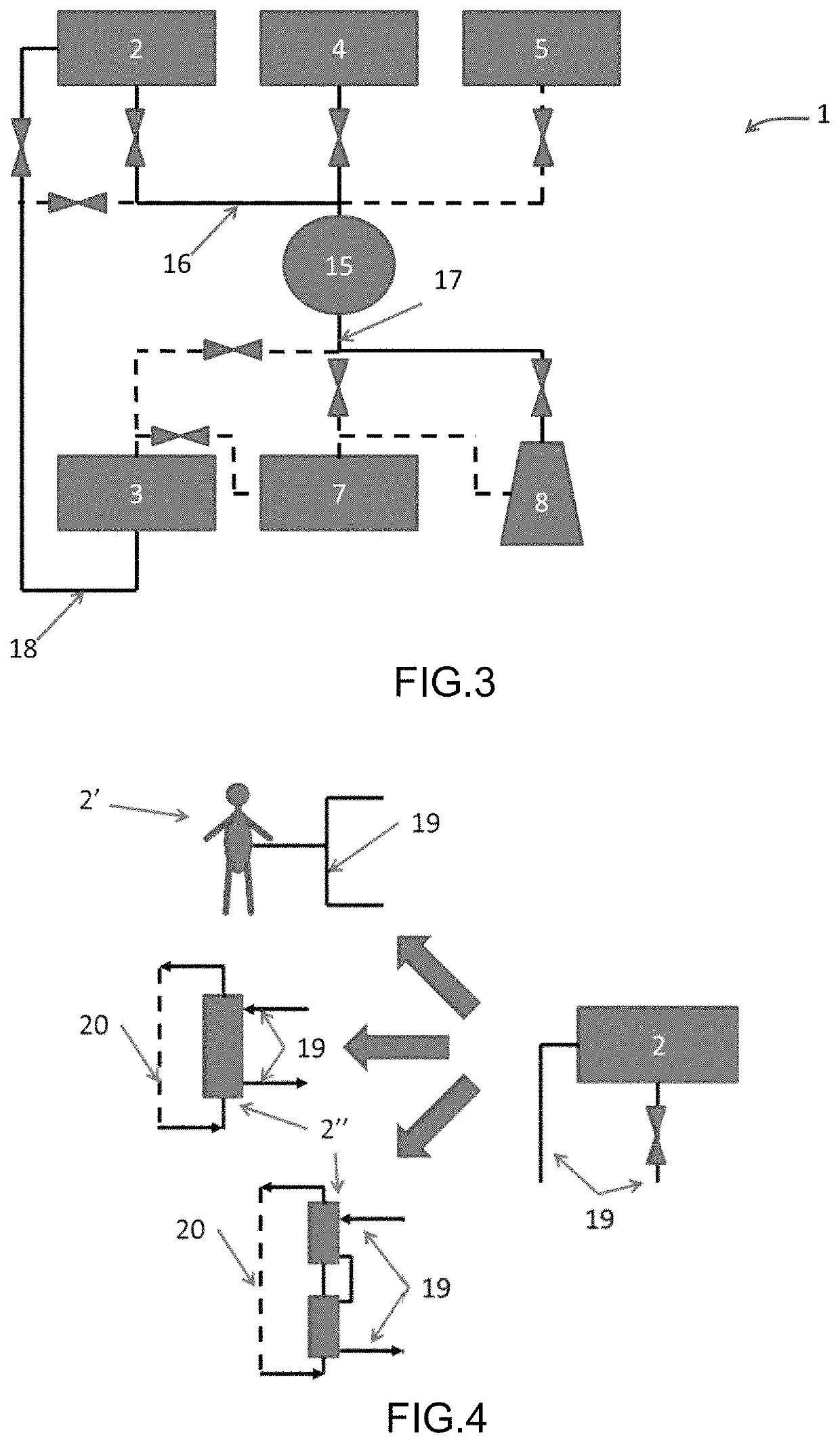

System for compensating for high-frequency leakage currents emanating from at least one component (5) of a motor vehicle, connected to a power supply network (1) via a rectifier device (3), the power supply network (1) having an earth and at least one phase other than earth. For each component, a first compensation device (6) is connected to rectified phases originating from the rectifier device (3) upstream of the component (5), and to the motor vehicle earth (10) and / or a second compensation device (7) is connected to rectified phases downstream of the component (5) and to the earth (10), the compensation devices (6, 7) being able to pick off some of the voltage applied to the component (5) and transmit to the earth (10) a compensation current of the same amplitude and direction as the leakage current but of opposite phase.

Owner:RENAULT SA

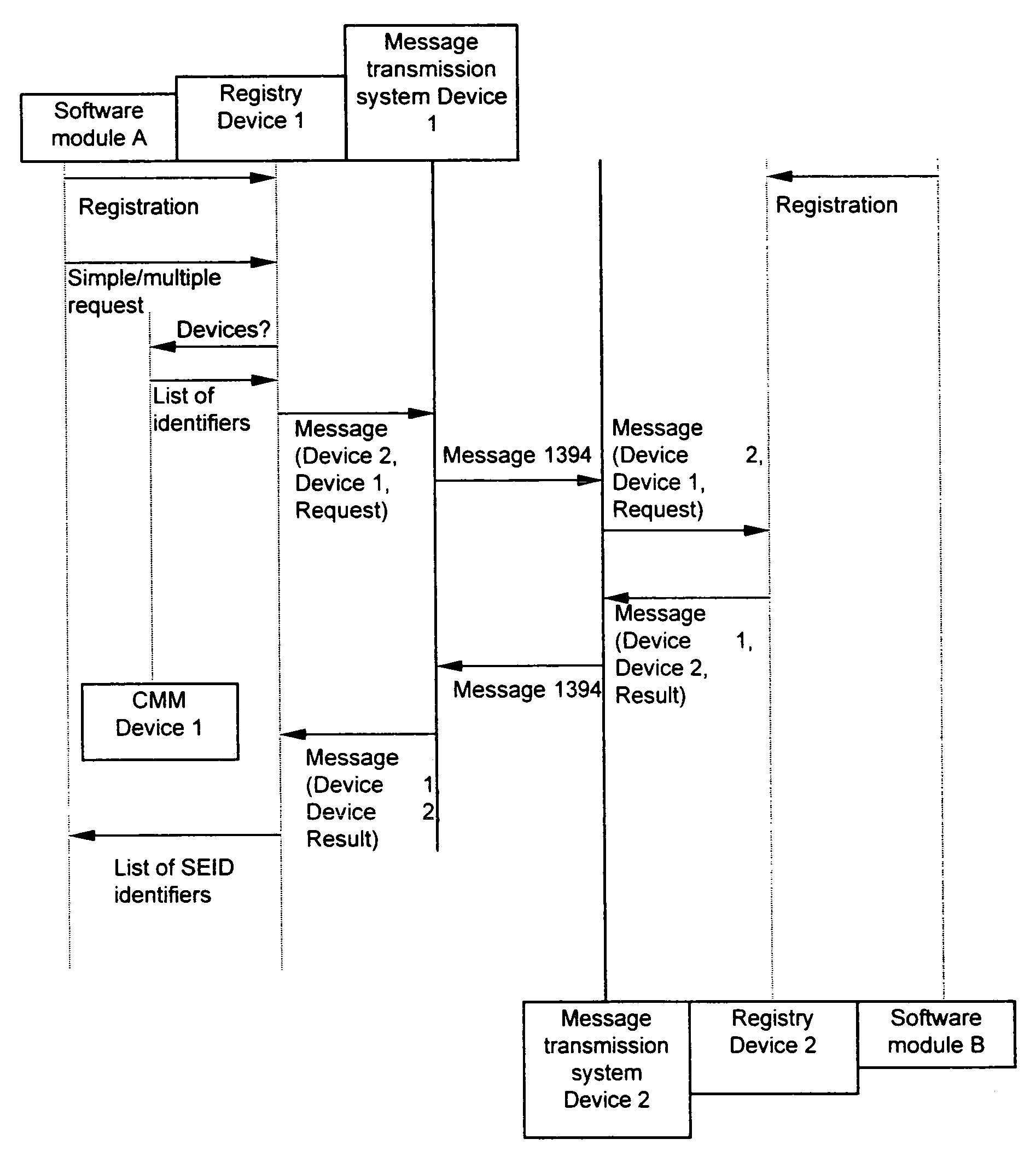

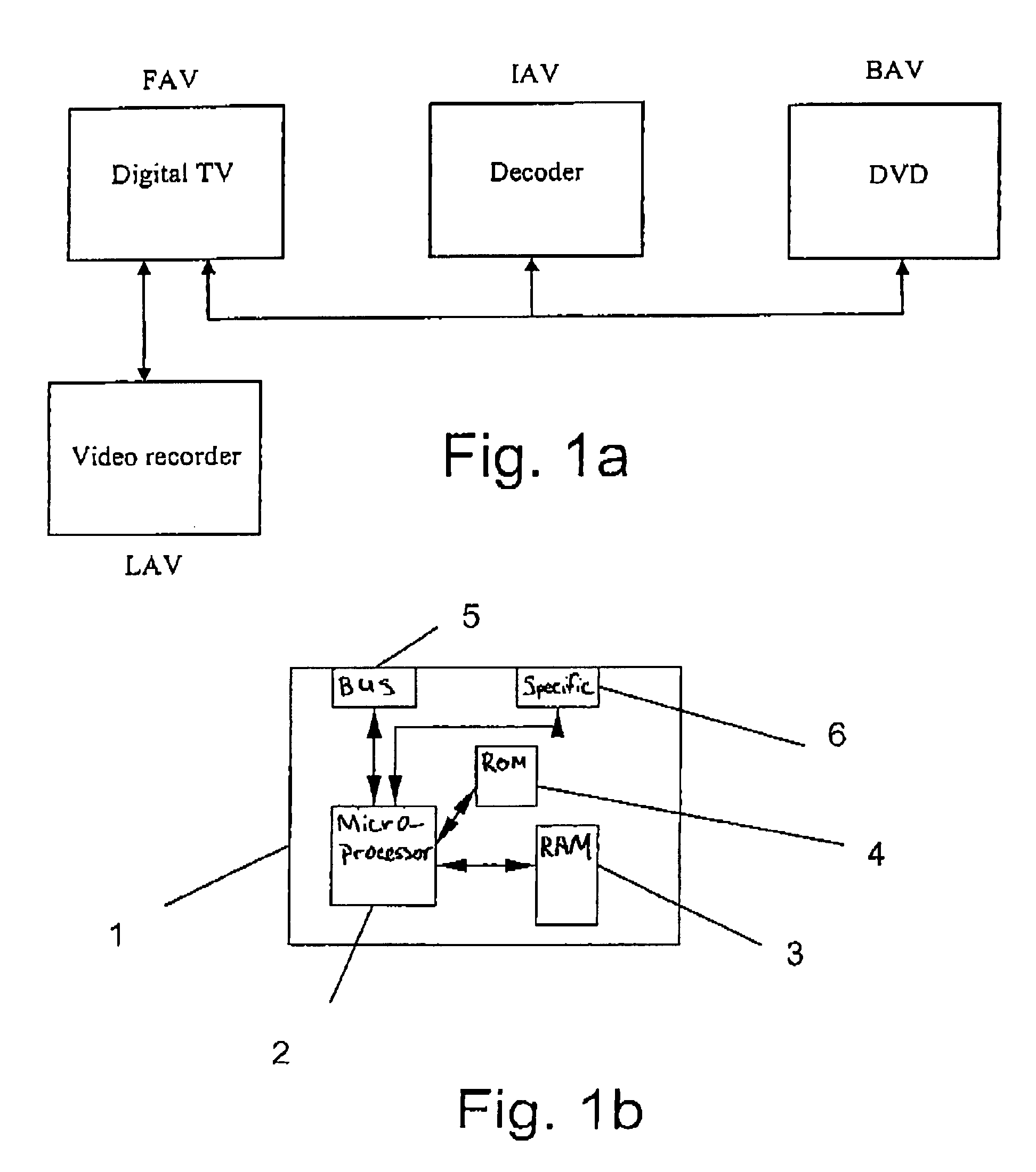

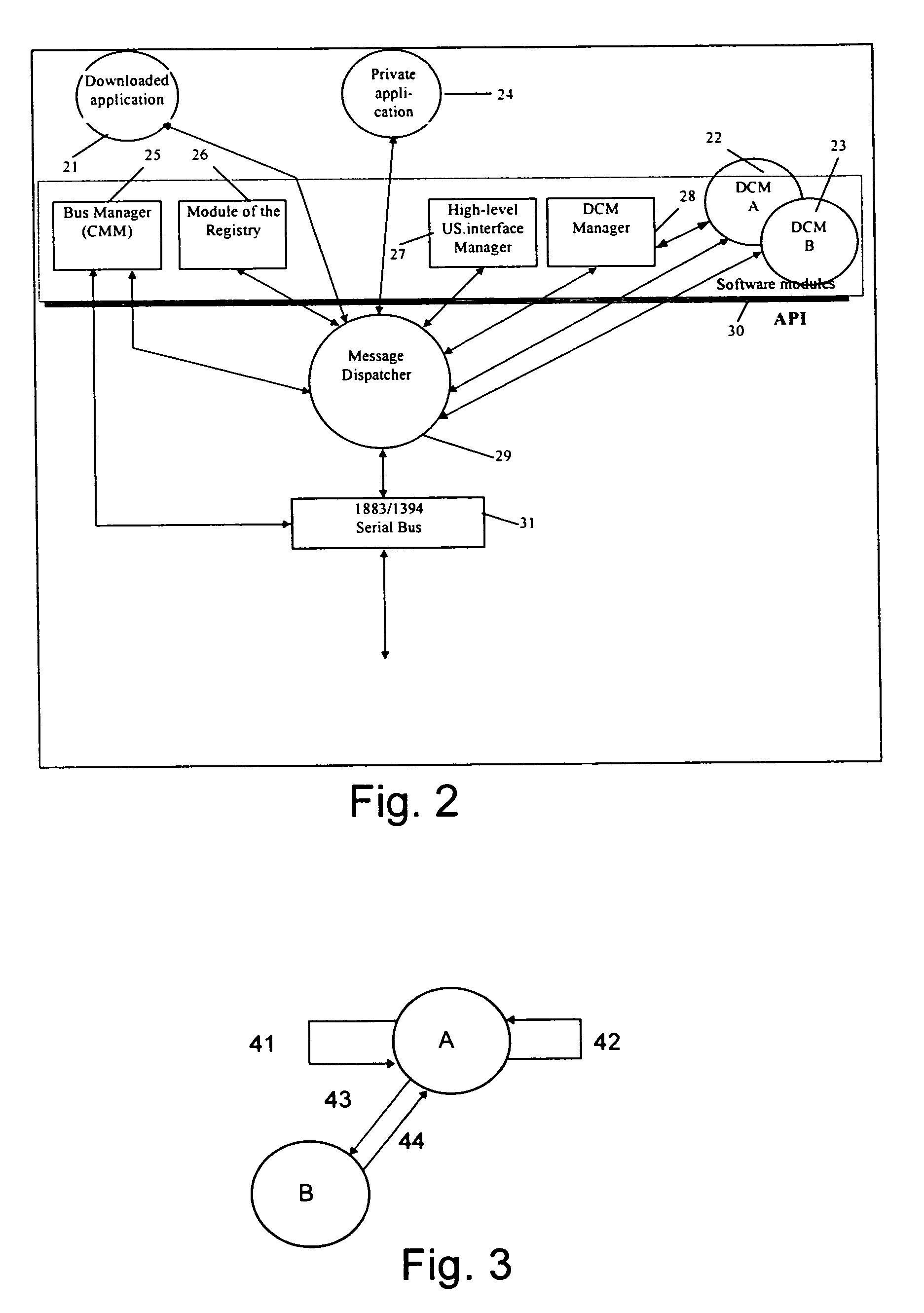

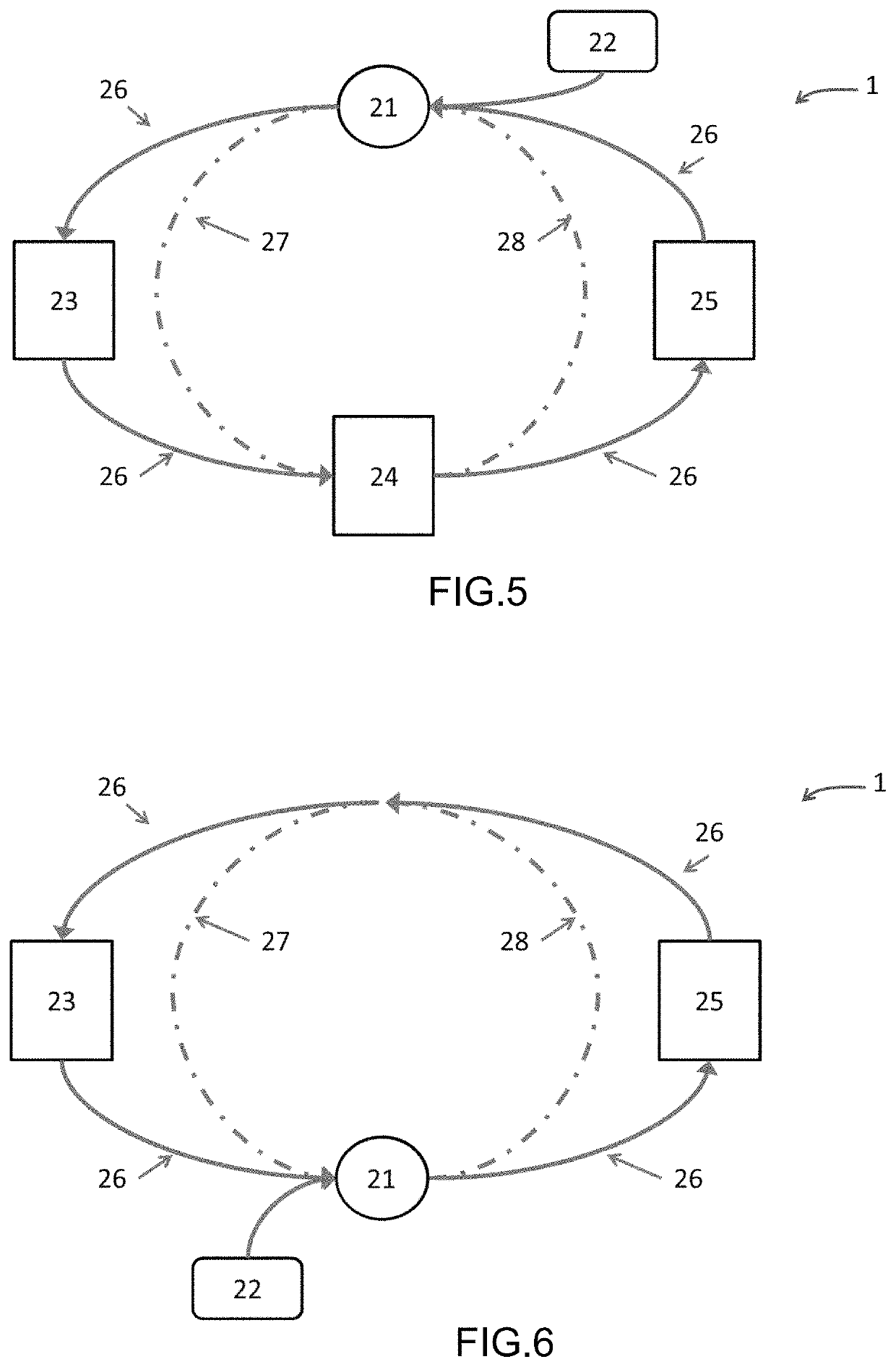

Method for managing objects in a communication network and implementing device

InactiveUS7680911B1Limited numberLimit propagationHybrid switching systemsInterprogram communicationManaged objectDistributed management

A method for distributed management of a catalogue of objects in a communication network comprising devices. The method comprises the step of registering local objects present in a device in a local registry managed at the level of the device, wherein a local object may formulate a request for a list of objects, and receive a collected response. The request is transmitted to the single local registry of the device hosting the local object and propagated through the local registry to distant registries. The responses are collected by the local registry and the collected response is transmitted to the local object that formulated the initial request. The invention applies in particular within the context of home communication networks.

Owner:INTERDIGITAL CE PATENT HLDG

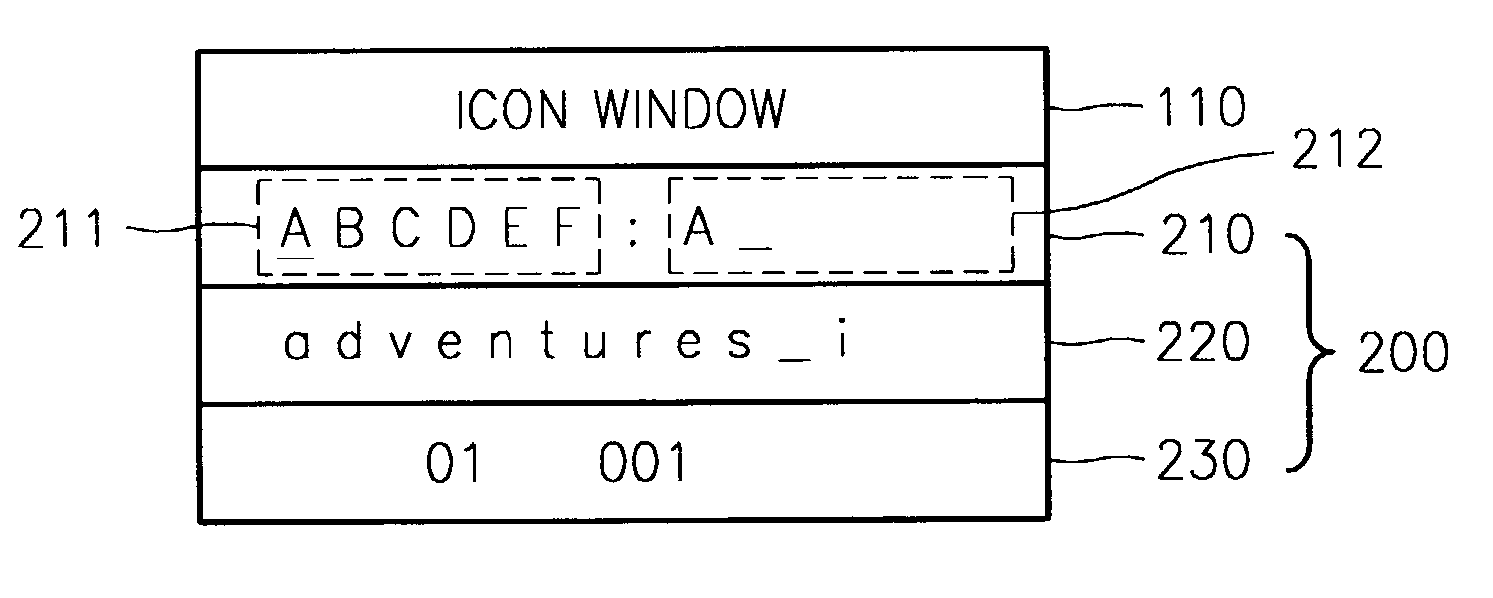

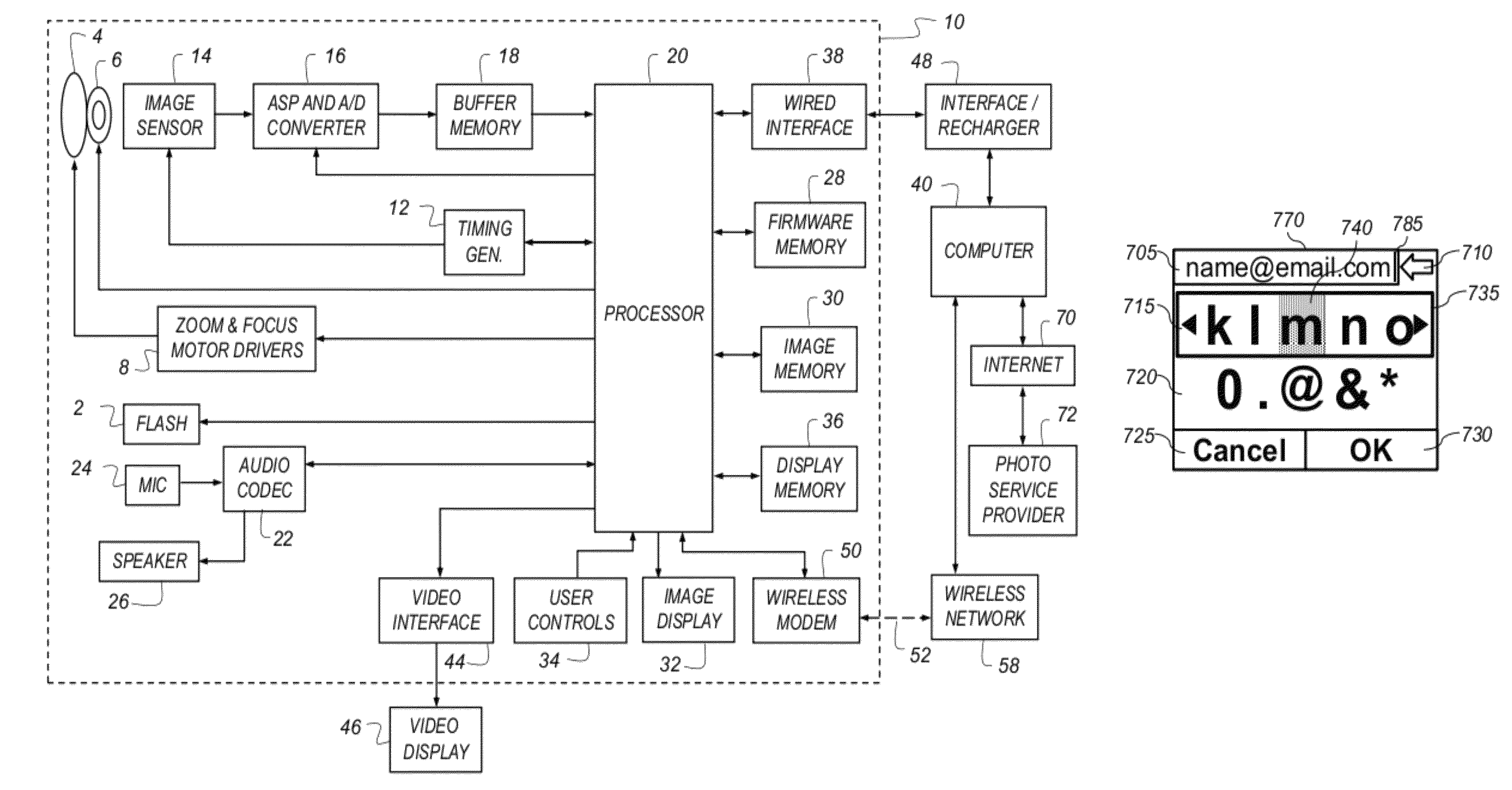

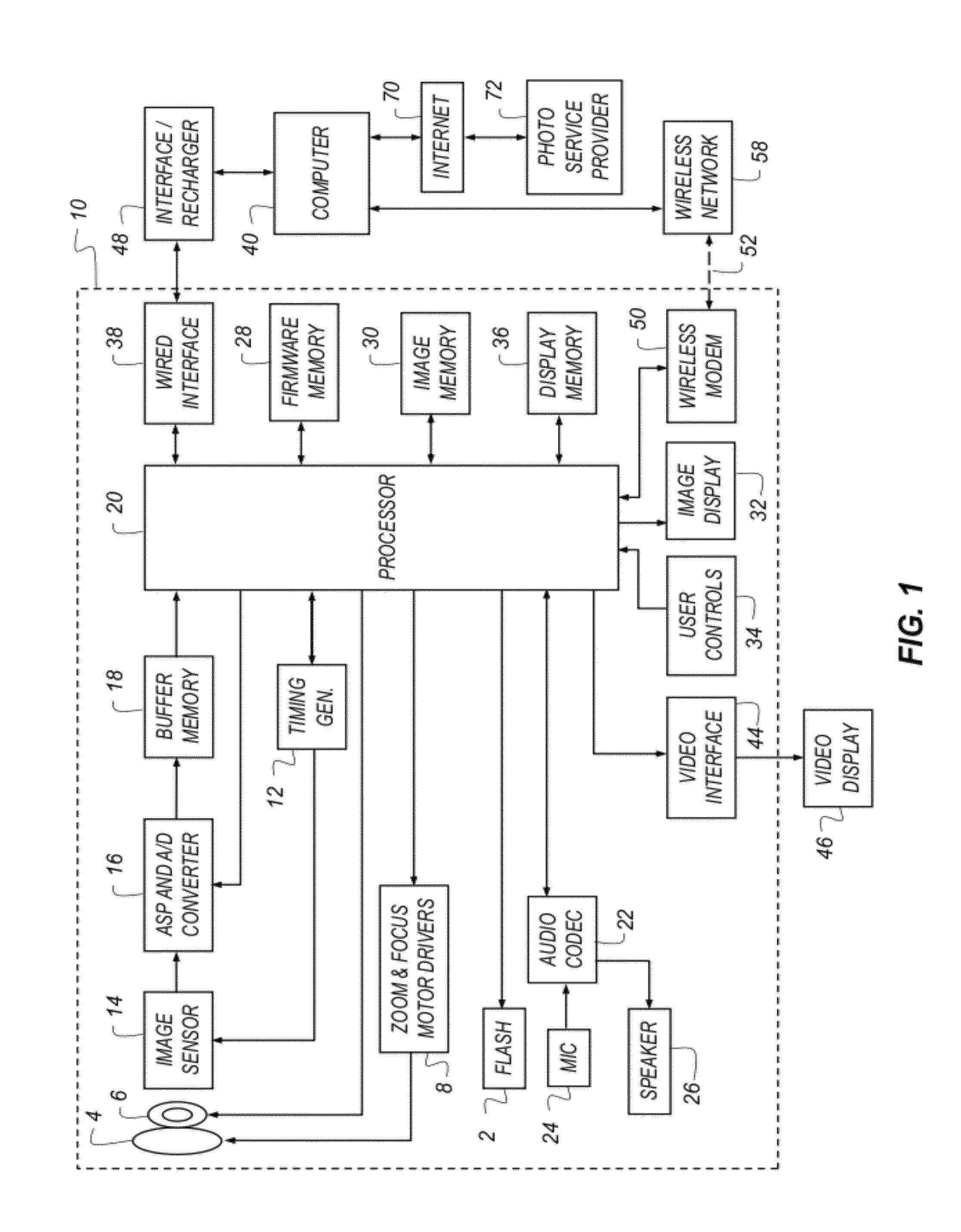

Digital camera user interface for text entry

ActiveUS9241101B2Small displayLimited numberTelevision system detailsElectronic editing digitised analogue information signalsUser inputText entry

A portable electronic device providing a user-specified input string, comprising: user controls enabling a user to select between at least an up input, a down input, a left input, a right input, and a confirmation input; and a program memory storing instructions configured to implement a method for providing a user-specified input string. The method includes: displaying a string input interface including a string entry section, and at least two independently scrollable character selection sections; accepting user input to sequentially select characters, wherein the up input and the down input are used to select a scrollable character selection section, the left input and the right input are used to scroll through the characters in the selected scrollable character selection section to select a particular character, and the confirmation input is used to add the selected particular character to the input string displayed in the string input section.

Owner:MONUMENT PEAK VENTURES LLC

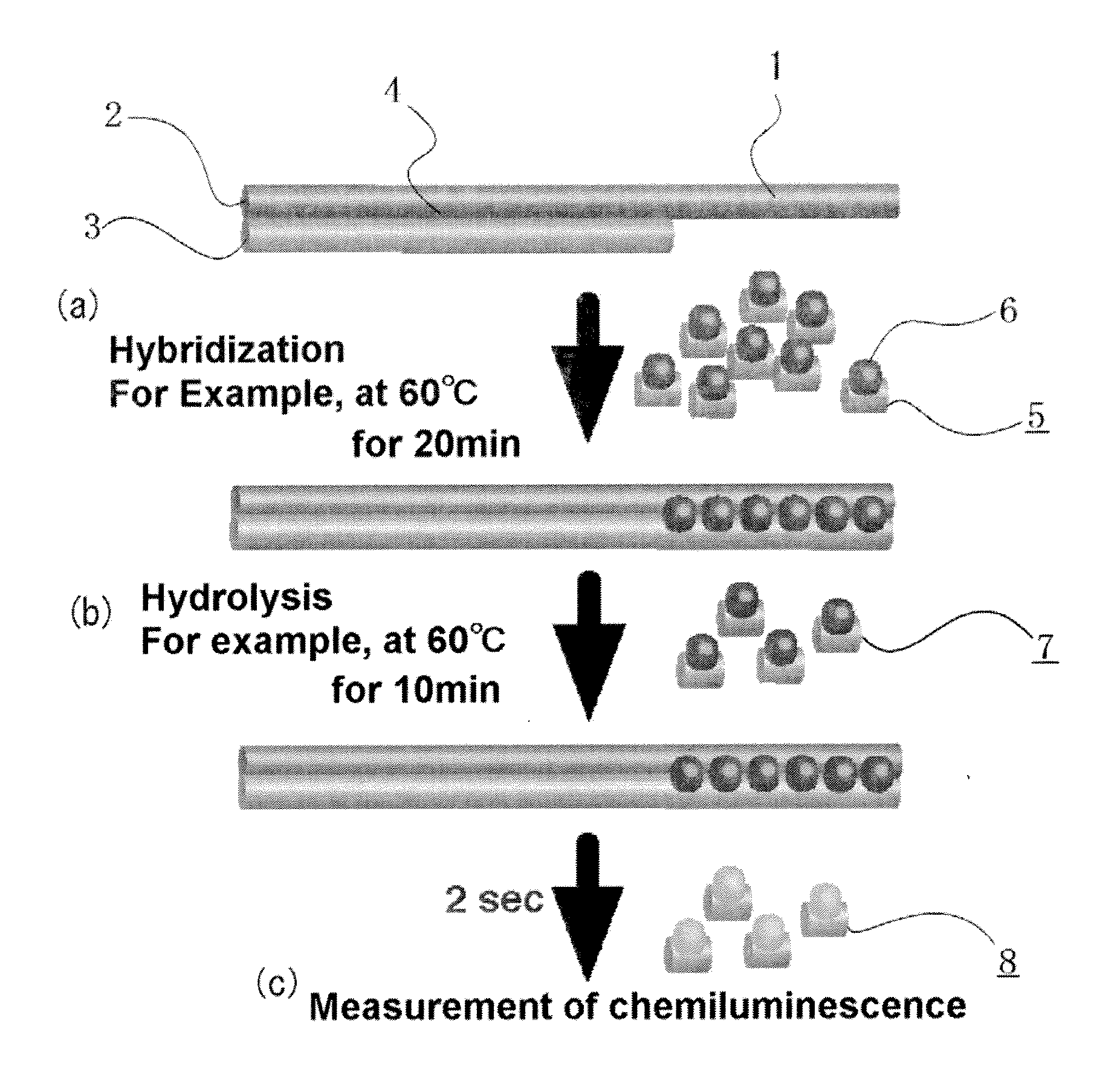

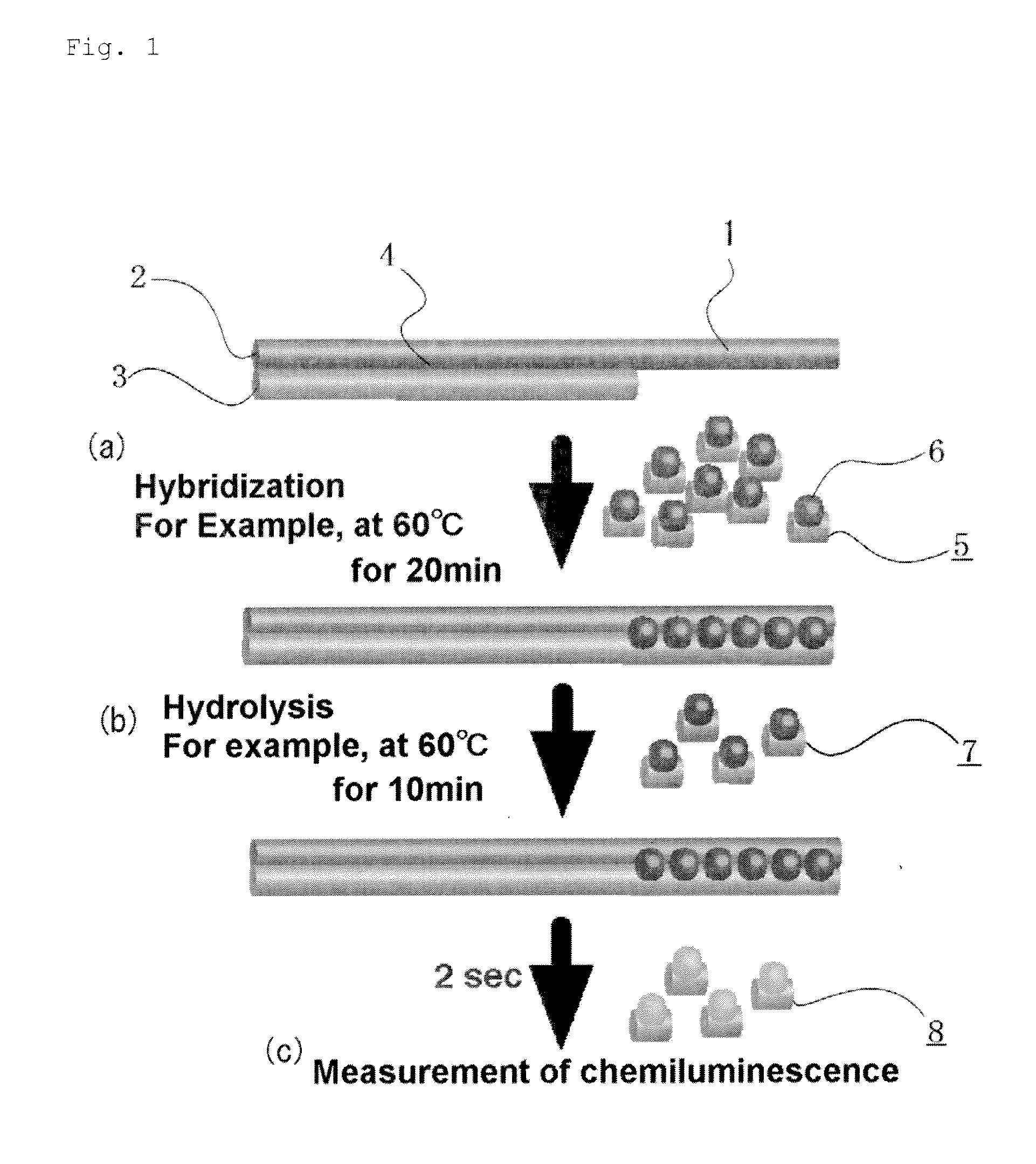

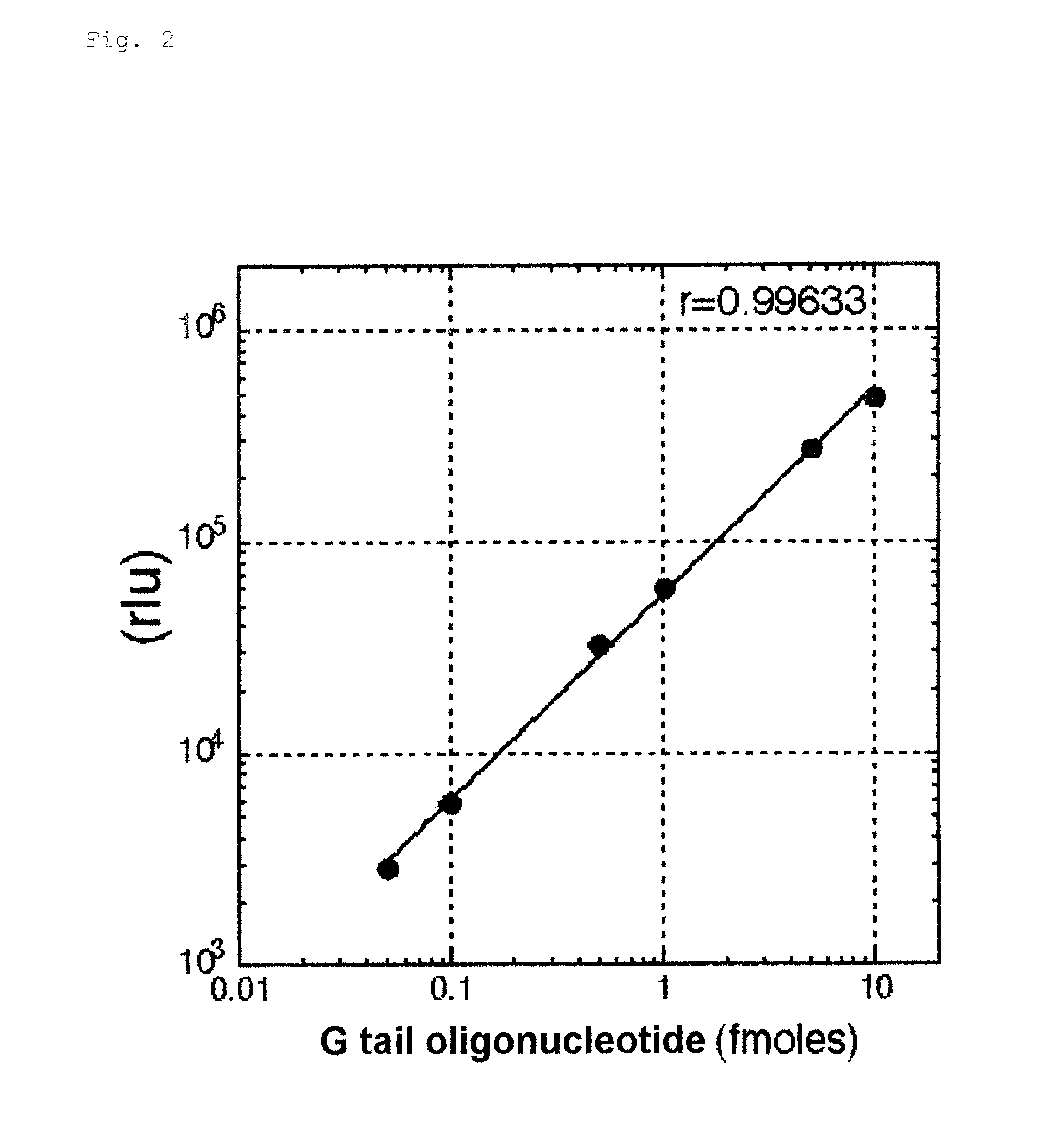

Method for determination of the length of the g-tail sequence and kit for the method

InactiveUS20090298062A1High sensitivityLimited numberMicrobiological testing/measurementChemiluminescenceTelomere

A method of measuring the length of a G tail sequence, characterized by hybridizing the G tail of an nondenatured chromosomal DNA in a sample with a labeled DNA probe having a sequence complementary to the telomere repeat sequence, measuring chemiluminescence from the hybridized DNA probe, and determining the length of the G tail sequence from the measured value, and a kit used for use in such a method.

Owner:HIROSHIMA UNIVERSITY +1

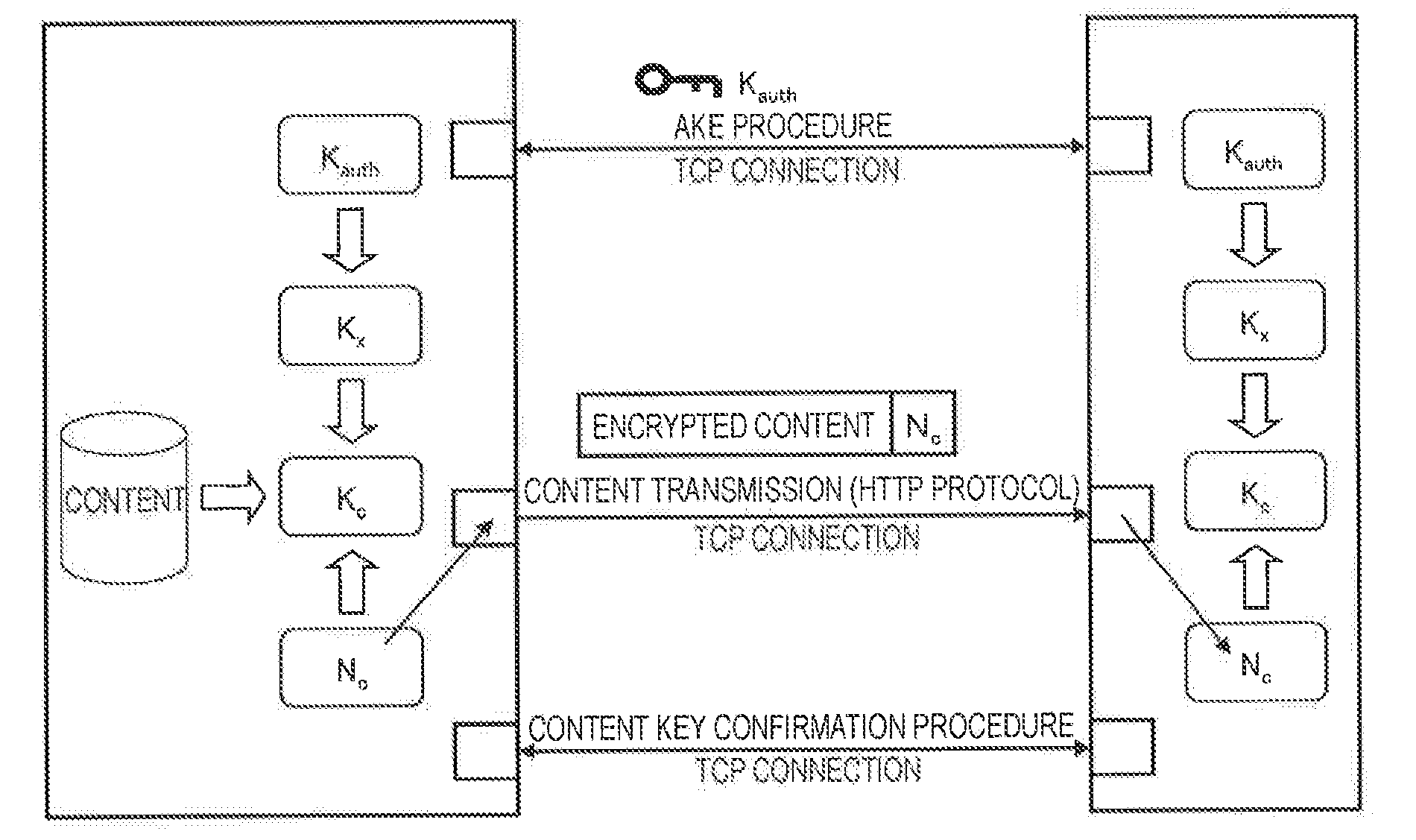

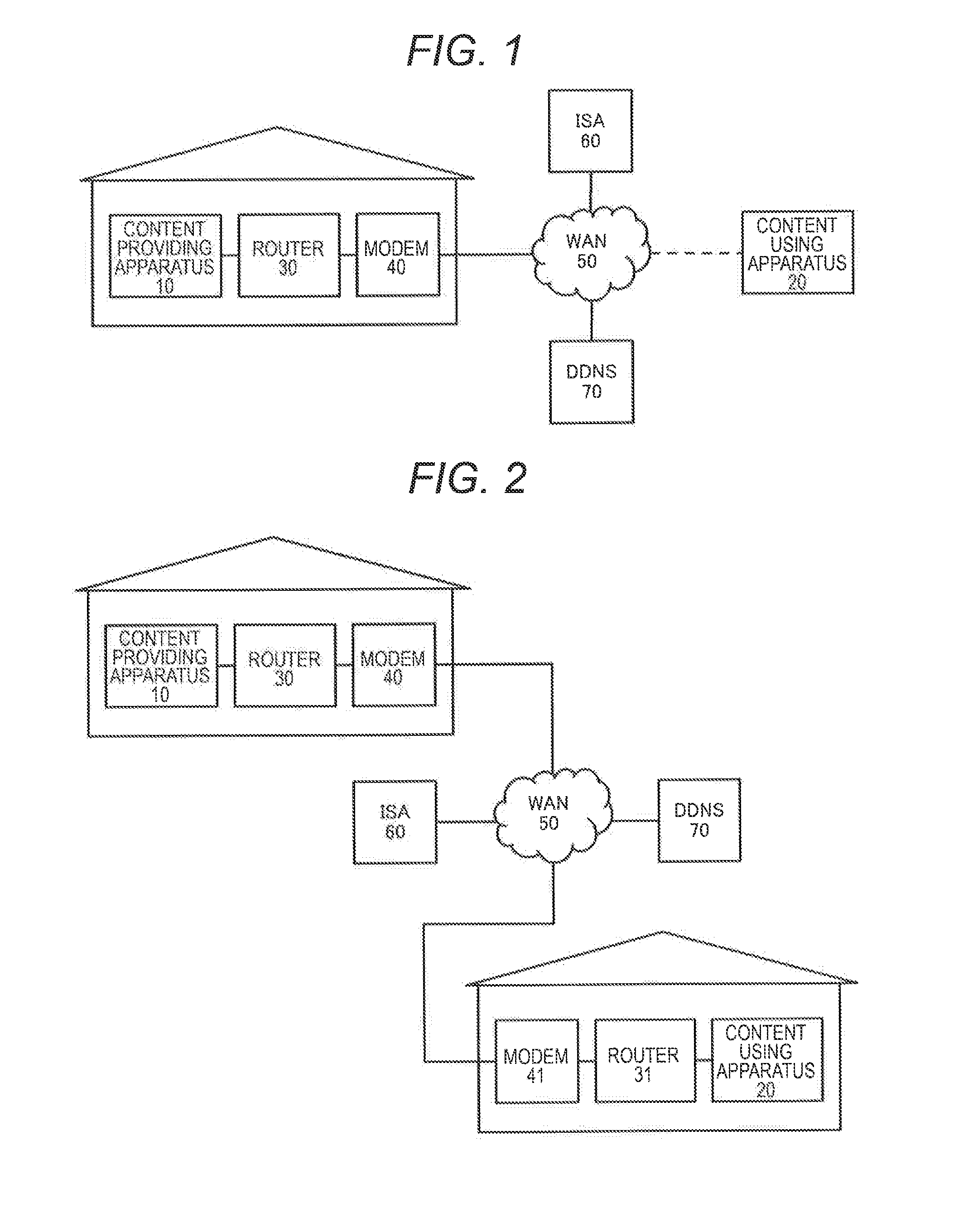

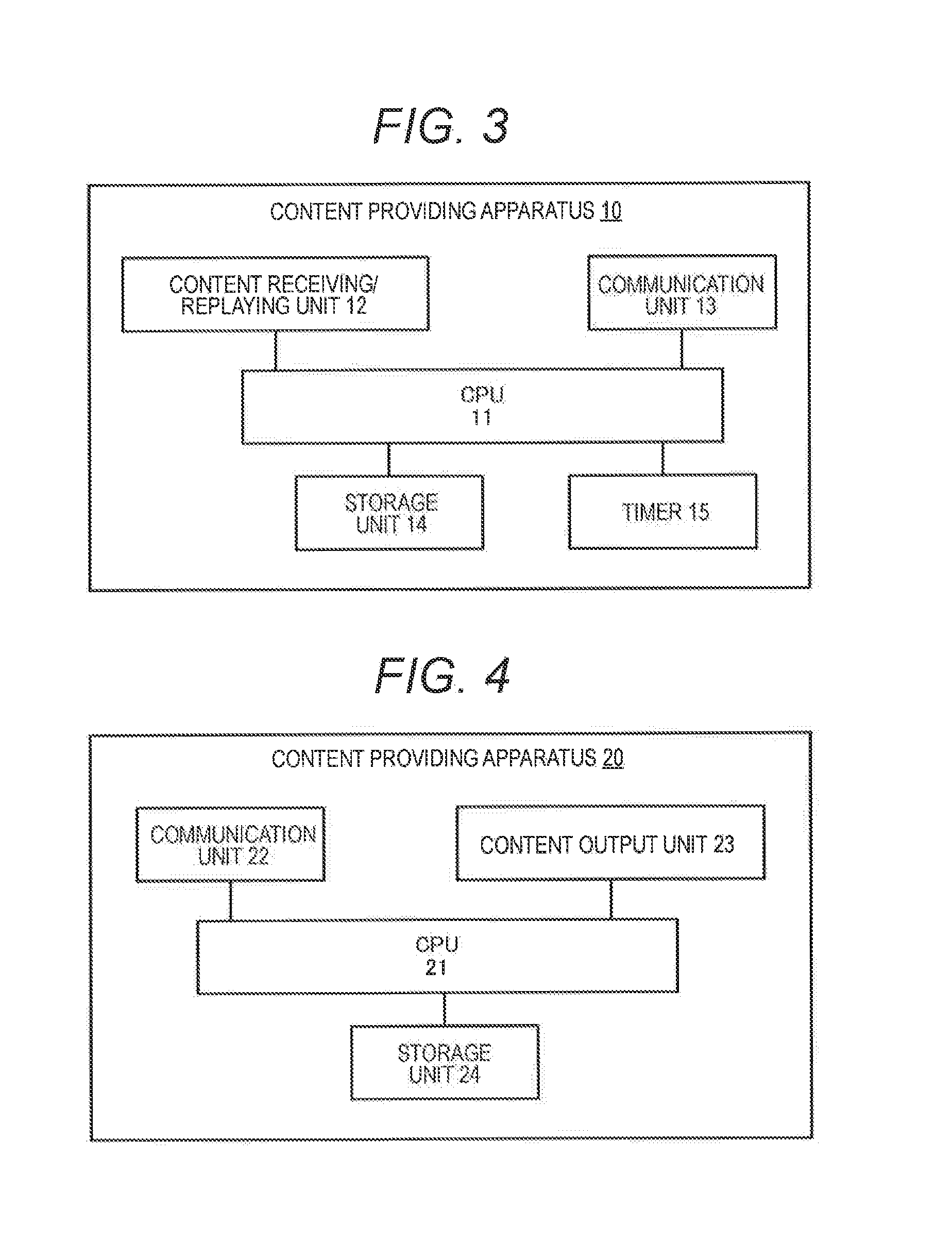

Communication system, communication apparatus, communication method, and computer program

InactiveUS20130124865A1Limited numberReduce in quantityKey distribution for secure communicationUser identity/authority verificationComputer securityComputer program

Owner:SONY CORP

Hemodialysis system

ActiveUS10596309B2Limited numberSimplify the fluid pathwayMembranesHaemofiltrationIntensive care medicineBiomedical engineering

A dialysis system comprises a filtration means, a pump and a sorbent device for performing a dialysis treatment and / or for regenerating a dialysate solution.

Owner:NEXTKIDNEY SA