Method for determining highly accelerated stress screening test condition

A technology with high accelerated stress and test conditions, applied in electronic circuit testing, optics, measuring devices, etc., can solve the problems of reducing product competitiveness, restricting the production capacity of manufacturers, low efficiency, etc., to reduce product production cycle, reduce testing cost, and the effect of improving test efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

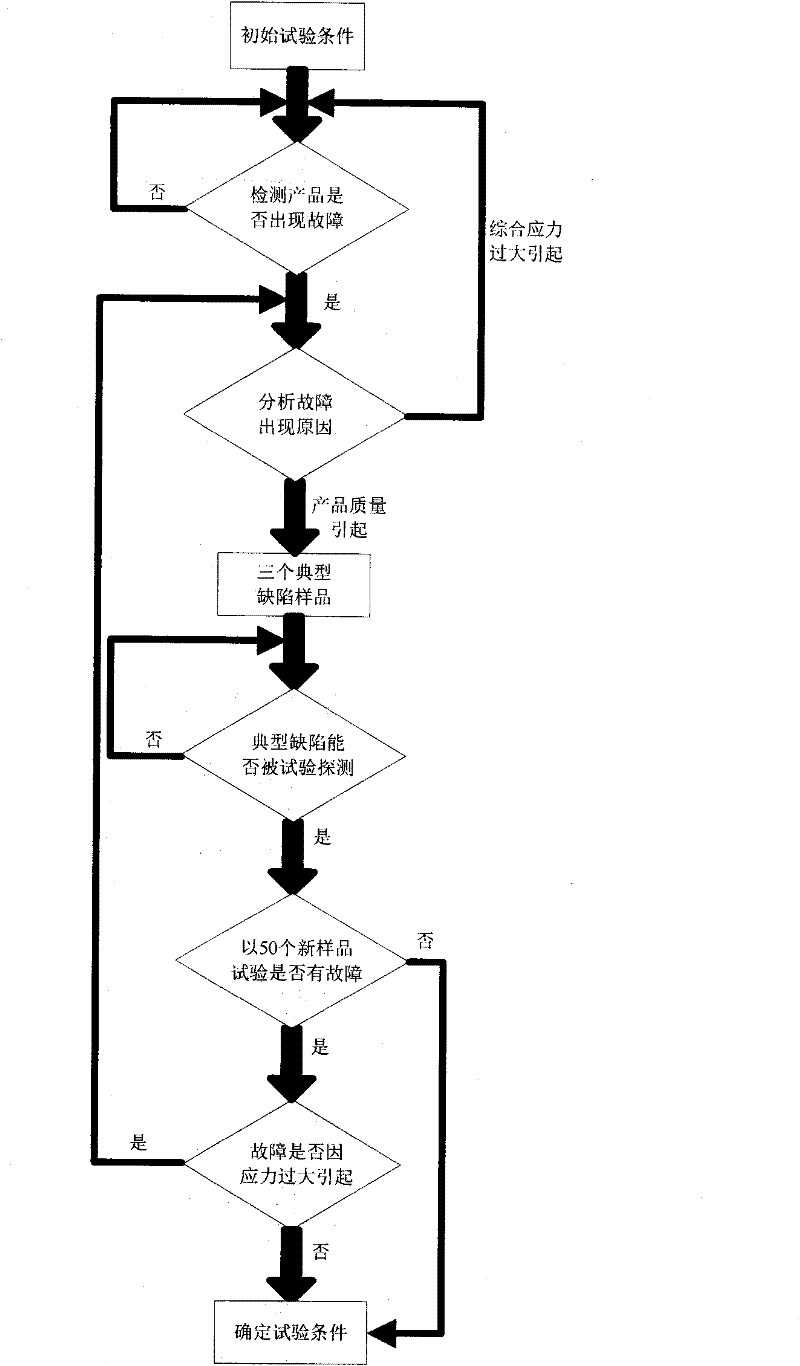

Image

Examples

Embodiment 1

[0021] Example 1: Method for determining high-accelerated stress screening test conditions of hardware circuit boards

[0022] First, according to the highly accelerated life test of the hardware circuit board, the temperature operation limit of the temperature and vibration comprehensive stress of the hardware circuit board, the vibration damage limit and the rapid temperature change conduction operation limit are determined. Reduce the temperature operation limit of temperature and vibration comprehensive stress by 30%, reduce the vibration damage stress by 50%, take 80% of the rapid temperature conduction operation limit as the temperature change speed value, and keep the high and low temperature for 10 minutes as the initial test conditions. Temperature and vibration comprehensive stress test with sub-rapid temperature change cycle. On the basis of this initial test condition, gradually increase the initial stress by 15%, and perform more than one functional test during the t...

Embodiment 2

[0026] Embodiment 2: Method for determining high-accelerated stress screening test conditions of LCD module products

[0027] First, according to the high-accelerated life test of the LCD module, the temperature operation limit, the vibration damage limit and the rapid temperature change conduction operation limit of the LCD module's temperature and vibration comprehensive stress are determined. Reduce the temperature operation limit of the combined temperature and vibration stress by 30%, reduce the vibration damage stress by 50%, use 80% of the rapid temperature conduction operation limit as the temperature change speed value, and keep the high and low temperature for 15 minutes as the initial test conditions. Temperature and vibration comprehensive stress test with 6 rapid temperature change cycles. On the basis of the initial test conditions, gradually increase the initial stress by 10%, and perform more than one functional test during the temperature and vibration stabilizat...

Embodiment 3

[0031] Embodiment 3: Method for determining high-accelerated stress screening test conditions for semiconductor integrated circuit chip IC products

[0032] First, according to the highly accelerated life test of the semiconductor integrated circuit chip IC, the temperature operating limit of the temperature and vibration comprehensive stress of the semiconductor integrated circuit chip IC, the vibration damage limit and the rapid temperature change conduction operating limit are determined. Reduce the temperature operation limit of the combined temperature and vibration stress by 30%, reduce the vibration damage stress by 50%, use 80% of the rapid temperature conduction operation limit as the temperature change speed value, and keep the high and low temperature for 15 minutes as the initial test conditions. Temperature and vibration comprehensive stress test with 6 rapid temperature change cycles. On the basis of the initial test conditions, gradually increase the initial stress...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More