Cathode patterns of electric semiconductor device and patterned arrangement method of cathode fingers thereof

A technology for power semiconductors and cathode strips, applied in semiconductor devices, electrical components, circuits, etc., can solve the problems of waste, reduce the utilization rate of chip area, large waste, etc., to improve uniformity, ensure convenience and practicability, The effect of improving gate characteristics

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

specific Embodiment approach

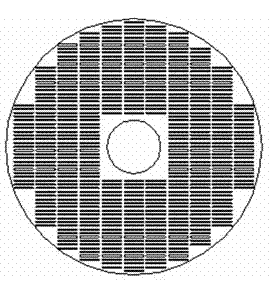

[0050] A specific embodiment of a method for arranging a cathode comb pattern of a power semiconductor device, comprising the following steps:

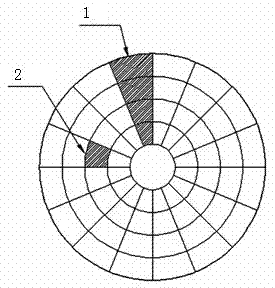

[0051] (A) Divide the cathode surface of the power semiconductor device into equal sectors with the center of the circle as the axis;

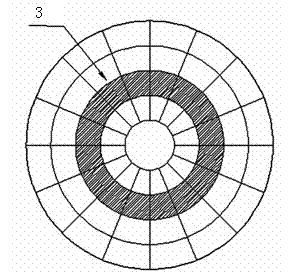

[0052] (B) Divide concentric rings on the cathode side of the power semiconductor device according to the length of the comb;

[0053] (C) Arrange combs in the sector, arrange the combs distributed in the sector and in the same ring along the circular arc of the ring, so that the outer edge of each circle of combs is a circular arc, and the combs The orientation of the bar setting is parallel to the center line of the sector;

[0054] (D) Reserve a gate shortcut channel between two adjacent sectors;

[0055] (E) The gate is provided in the central area or the ring area or the edge ring area of the cathode face;

[0056] (F) Process the photolithographic mask designed according to the above steps ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More