Silicon controlled rectifier used for ESD protection

A technology of electrostatic protection and thyristor, applied in circuits, electrical components, electric solid devices, etc., can solve the problems of high turn-on voltage, failure of gate oxide protection, slow thyristor opening speed, etc. Uniform, device robustness, and quick response

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0026] The structure of P well, N well, N+, P+ injection region, PMOS, NMOS and isolation resistance in the present invention can all be realized by using the existing standard CMOS integrated circuit manufacturing process.

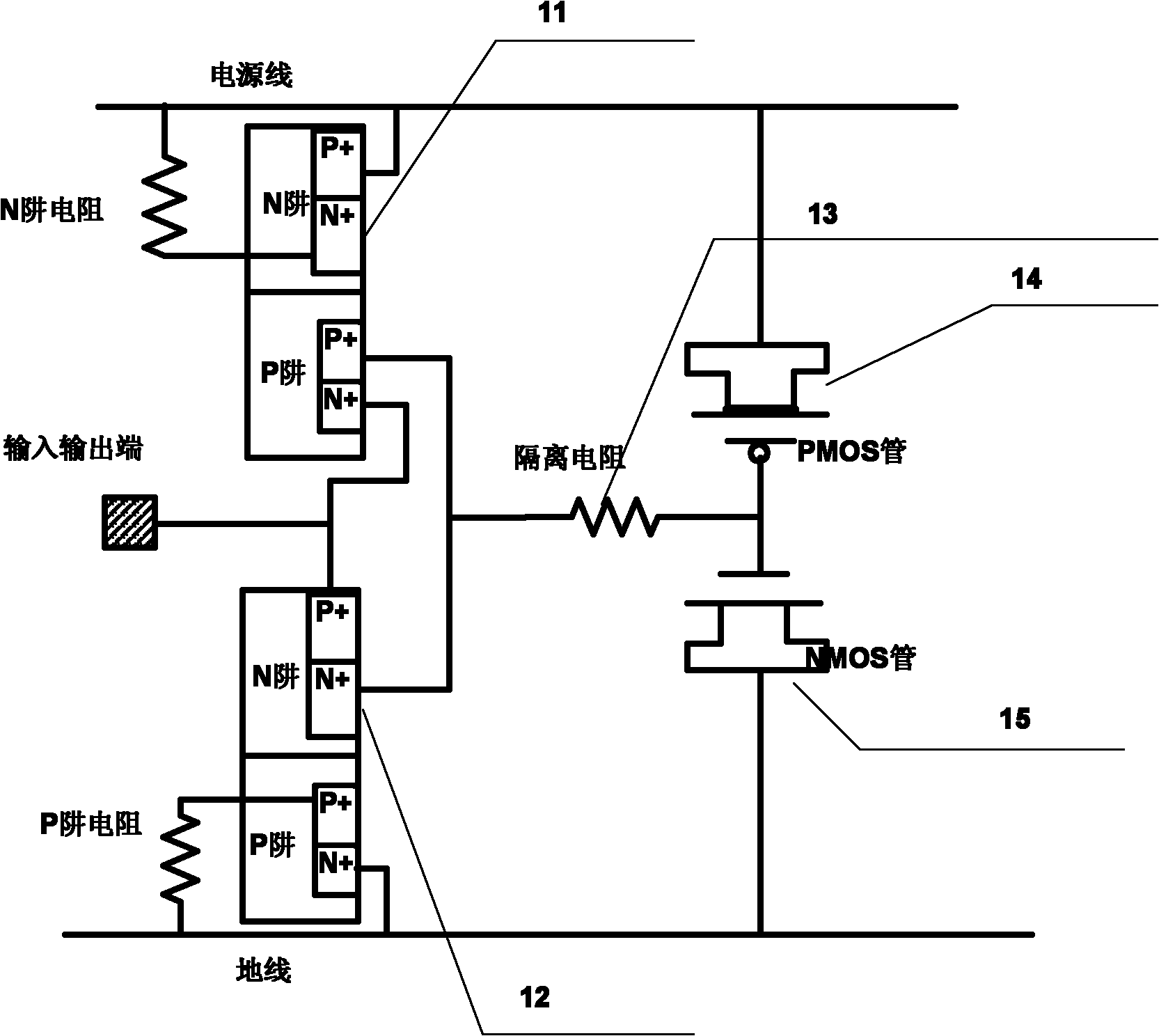

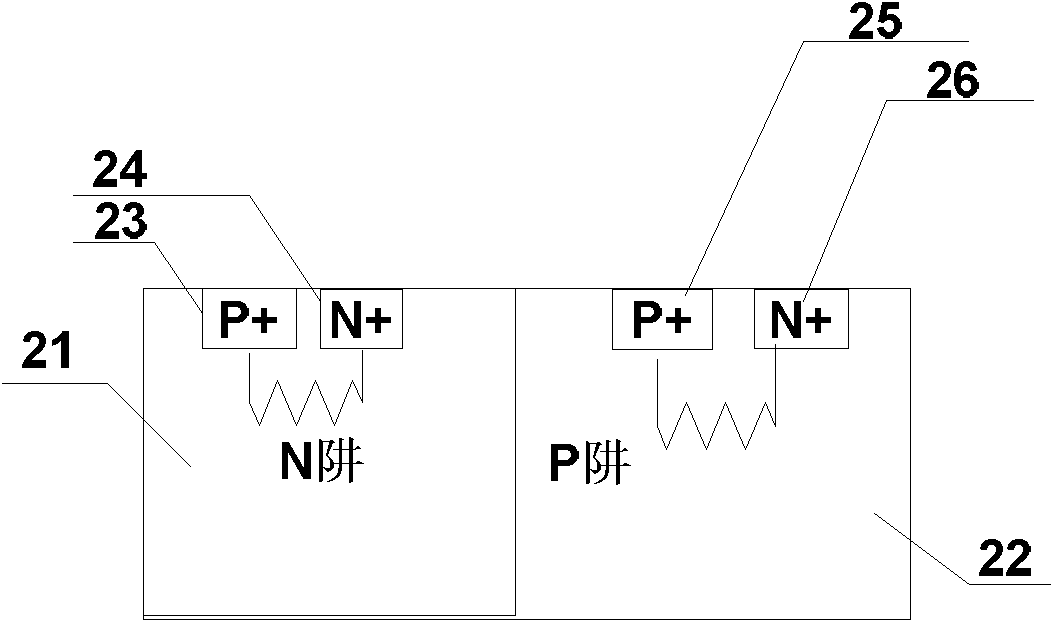

[0027] Such as Figure 1-3 As shown, a thyristor with an electrostatic protection structure includes a pull-up thyristor 11, a pull-down thyristor 12, an isolation resistor 13, an NMOS transistor 14, and a PMOS transistor 15. The pull-up thyristor 11 includes a first N well 21 and a first P well 22, wherein the first N well 21 has a first P+ implantation region 23 and a first N+ implantation region 24 respectively, and the first P well 22 has a second P+ implantation region respectively 25 and the second N+ implantation region 26;

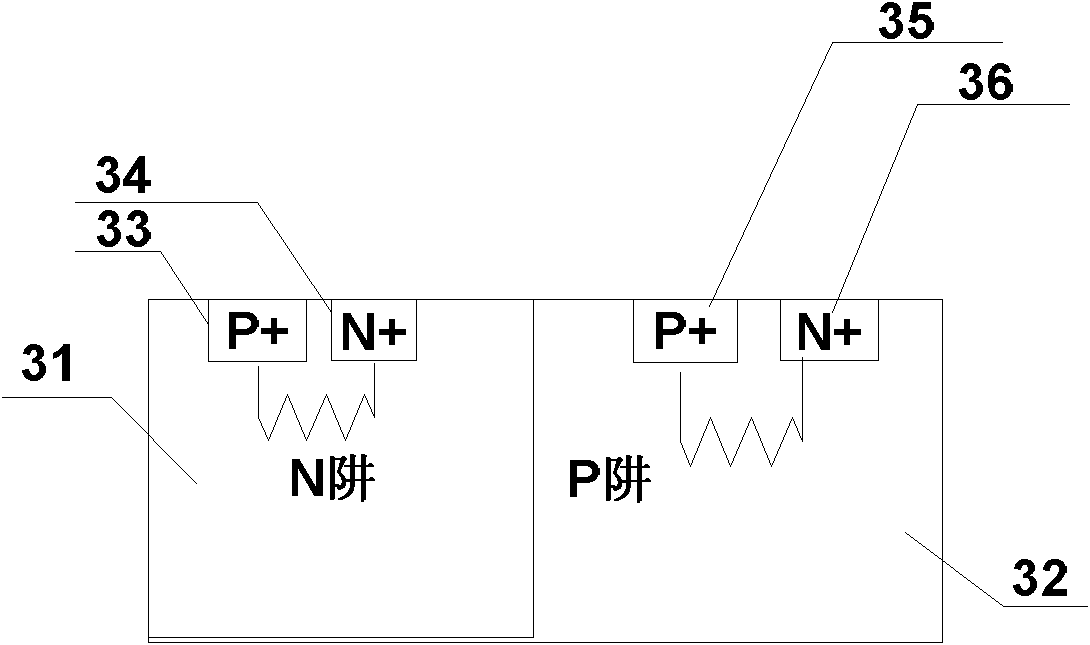

[0028] The pull-down thyristor 12 includes a second N well 31 and a second P well 32, wherein the second N well 31 has a third P+ injection region 33 and a third N+ implant region 34 respectively, and the second P well 32 has...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More