Method for testing time series data of standard unit

A technology of time series data and test method, which is applied in the field of microelectronics, can solve the problems of unexpandable test structure, test data that does not meet the analysis needs, simple test data, etc., and achieve the effect of convenient test vector and IO circuit scan test

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0033] The present invention is described in further detail below in conjunction with accompanying drawing:

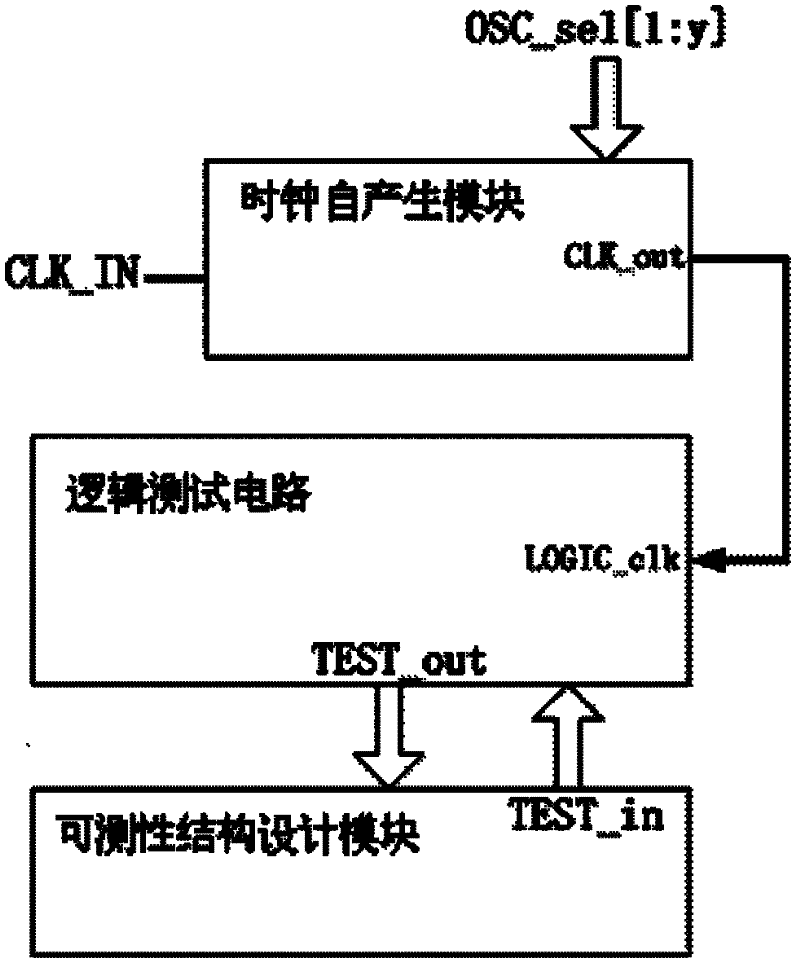

[0034] The method of the present invention is as attached figure 1 As shown, including the clock self-generation module, test logic circuit, and testability design module.

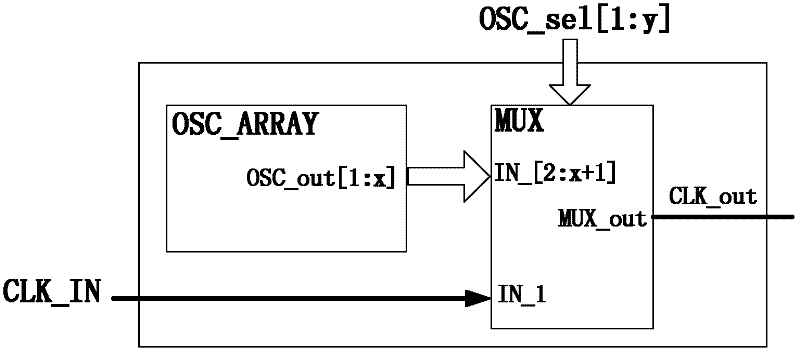

[0035] Clock self-generation module, including ring oscillator array OSC_ARRAY for clock generation and clock selection circuit MUX for multi-channel clock selection, the structure is as attached figure 2 shown. Among them, the x-channel output OSC_out[1:x] of OSC_ARRAY is respectively connected to the x-input terminals IN_[2:x+1] of the MUX, and the y-channel OSC_sel signal is respectively connected to the y-selection terminals sel[1:y] of the MUX. CLK_IN is connected to the input terminal IN_1 of MUX.

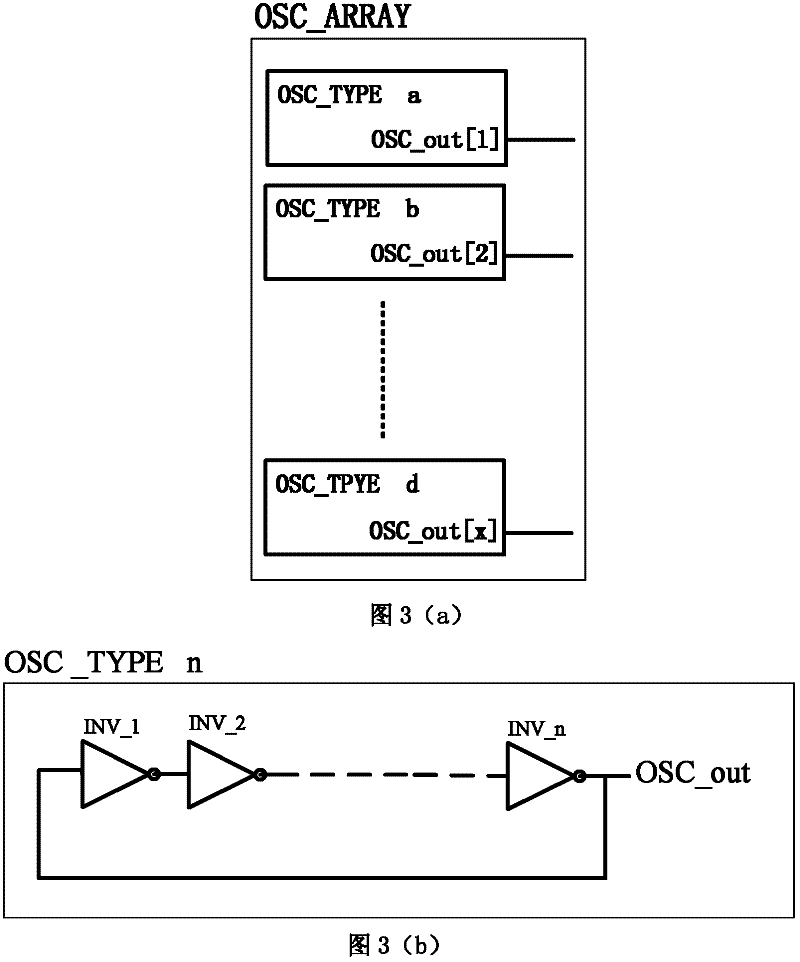

[0036] OSC_ARRAY module structure as attached image 3 As shown in (a), it consists of x ring oscillator logic OSC_TYPE, and outputs x clock signals OSC_out[1:x]. Among them, OSC_TYPE implem...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More