A SoC verification method and debugging tool for radio frequency signals

A radio frequency signal and verification method technology, applied in the field of single-chip system debugging and verification, can solve problems such as inability to approach verification results, interference, and inability to flexibly adjust electronic tuners and demodulators, so as to reduce development risks and improve efficiency. , The effect of convenient debugging work

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

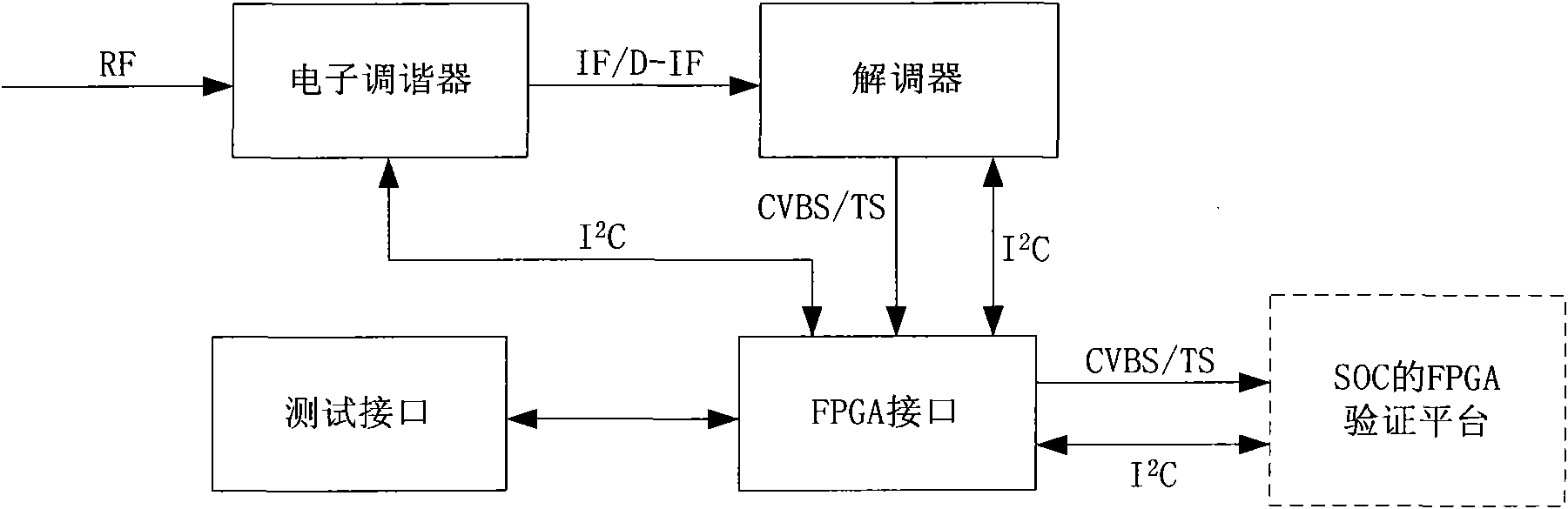

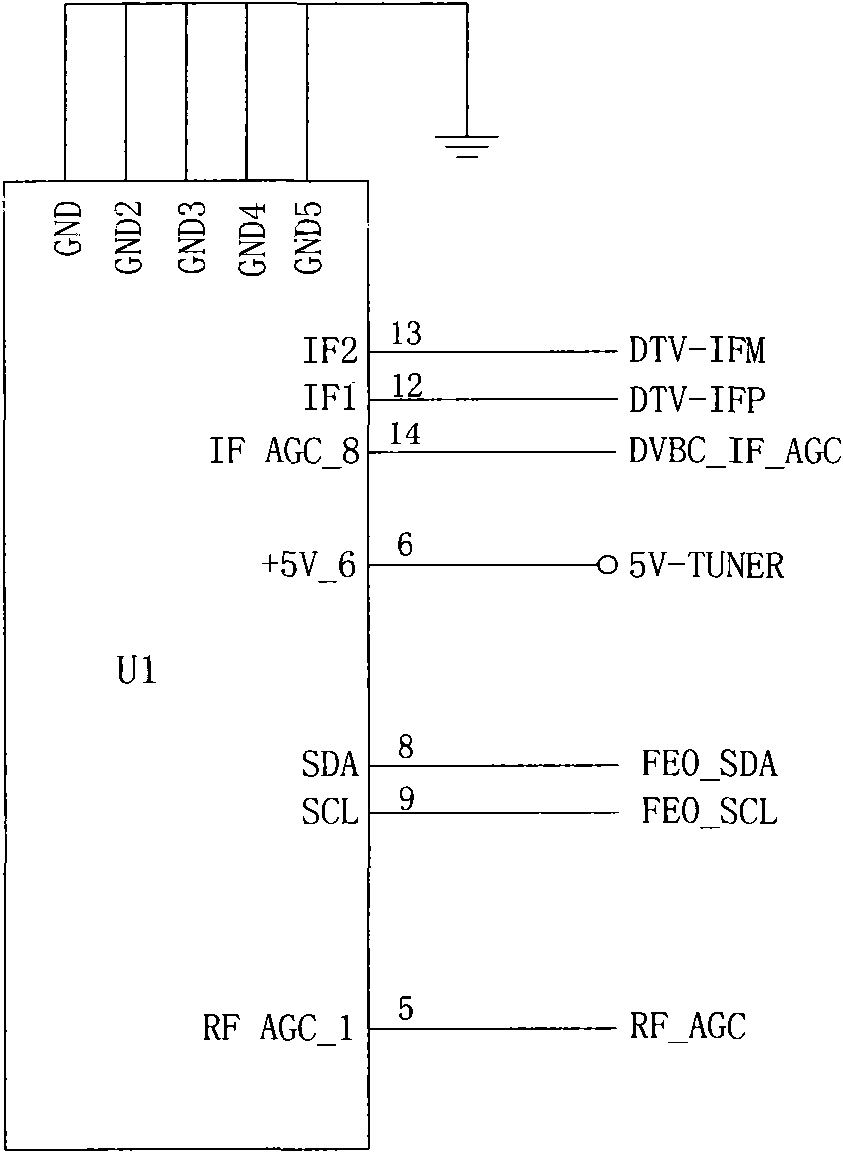

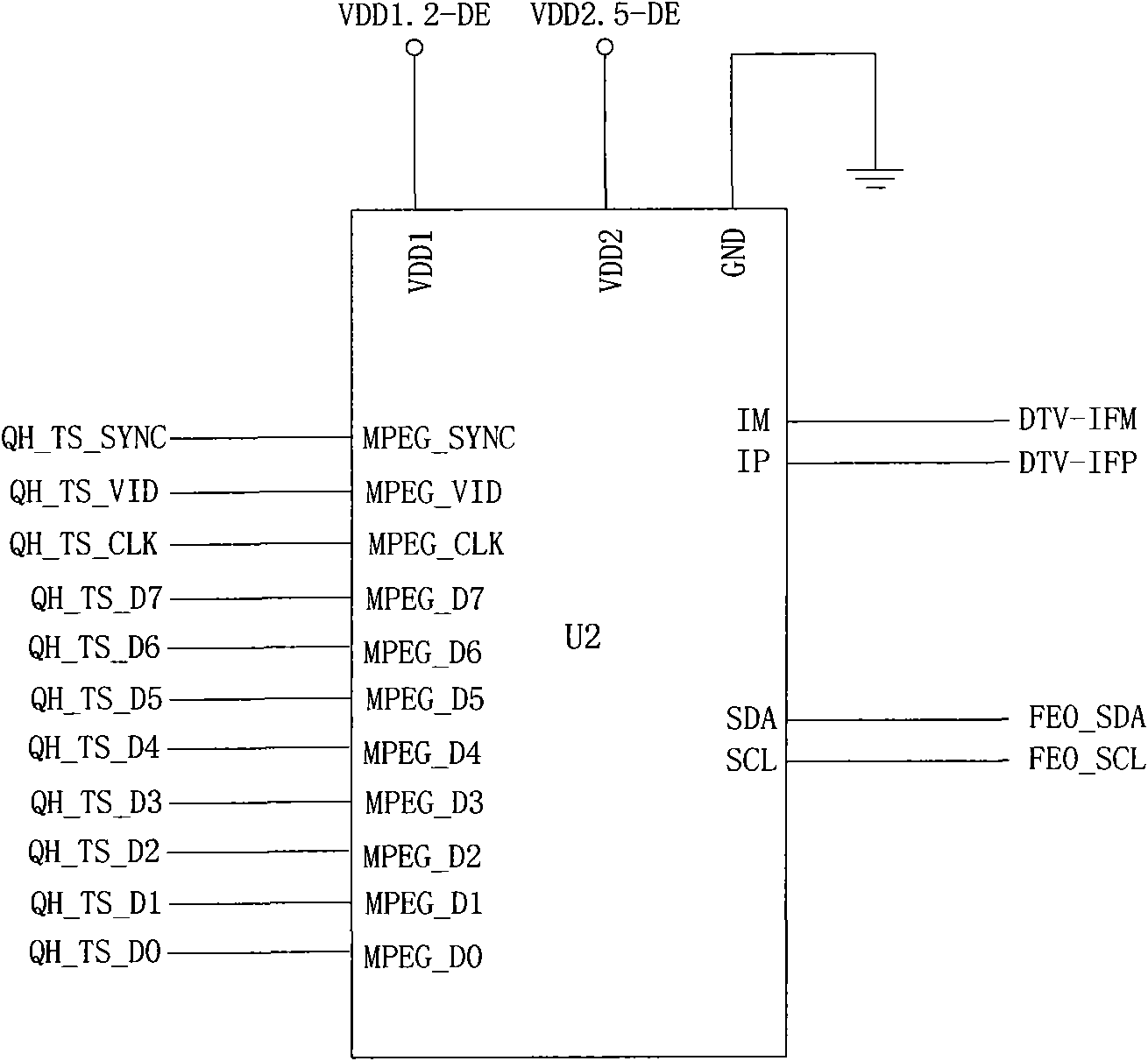

[0029] Embodiment one, see figure 1 As shown, the debugging tool of this embodiment uses an electronic tuner and a demodulator to build a radio frequency demodulation module. The electronic tuner can be a digital-analog integrated tuner or a digital and analog tuner, which receives the radio frequency signal RF and converts it into a digital intermediate frequency signal D-IF and an analog intermediate frequency signal IF and transmits it to the demodulator. The demodulator can be equipped with a digital demodulator and an analog demodulator at the same time, and the digital demodulator receives the digital intermediate frequency signal D-IF, converts it into a TS stream and transmits it to the corresponding pin of the FPGA interface; the analog demodulator receives the analog intermediate frequency signal D-IF The signal IF is converted into a mixed video broadcast signal CVBS and transmitted to the corresponding pins of the FPGA interface. According to the debugging and ver...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More