Clock phase alignment and adjustment circuit

A technology to adjust the circuit and clock phase, applied in the direction of electrical components, automatic power control, etc., can solve the problems of complex circuits, high requirements for process support, and inability to guarantee the duty cycle, and achieve the effect of avoiding glitches

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0040] Below in conjunction with the drawings, preferred embodiments of the present invention are given and described in detail.

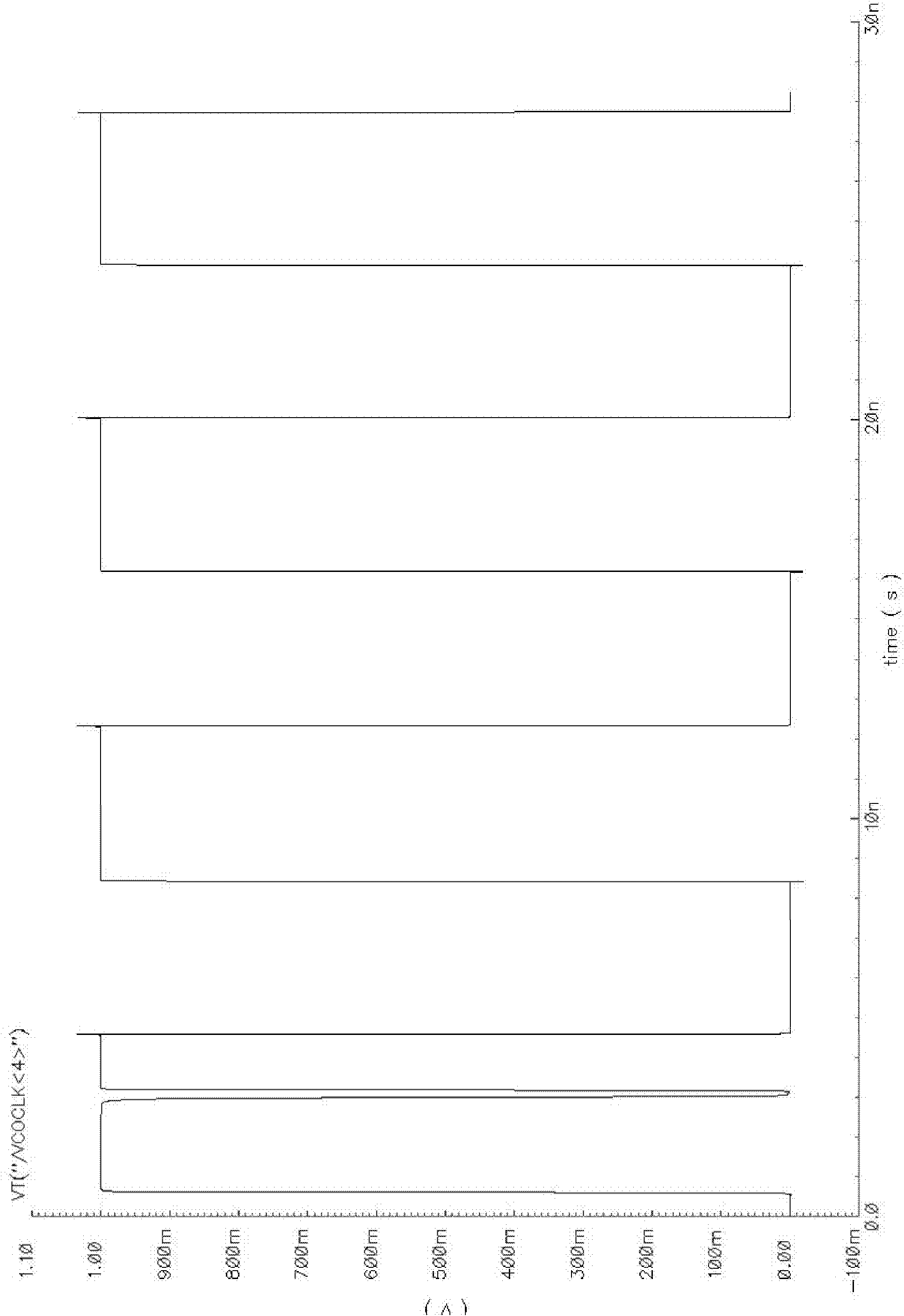

[0041] Such as Figure 5 As shown, the present invention, that is, a clock phase alignment adjustment circuit, includes an AND gate 3, a first delayer 4, a second delayer 5, a first D flip-flop 6, a second D flip-flop 7 and an inverter 8 ,in:

[0042] One input end of the AND gate 3 is connected to the output end of the phase-locked loop 1 to receive the voltage-controlled oscillator clock signal VCOCLK, and the other input end is connected to the output end of the second delayer 5 to receive the enable signal ENABLE, and the AND gate 3 The output terminal of each output frequency divider is connected to the input terminal of each output frequency divider 2, and the clock signal OUTCLK after adjusting the phase is provided to the output frequency divider 2;

[0043] The input end of the first delayer 4 receives the reset signal RESETB, and its ou...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More