Processing unit interface for intellectual property (IP) core and automatic generation method thereof

A processor interface and automatic generation technology, applied to the architecture with a single central processing unit, general-purpose stored program computer, etc., can solve the problem of low interface efficiency, reduced interface performance between IP core and processor, and poor compatibility and other issues to achieve the effect of improving development efficiency, reducing development time and verification time, and good compatibility

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

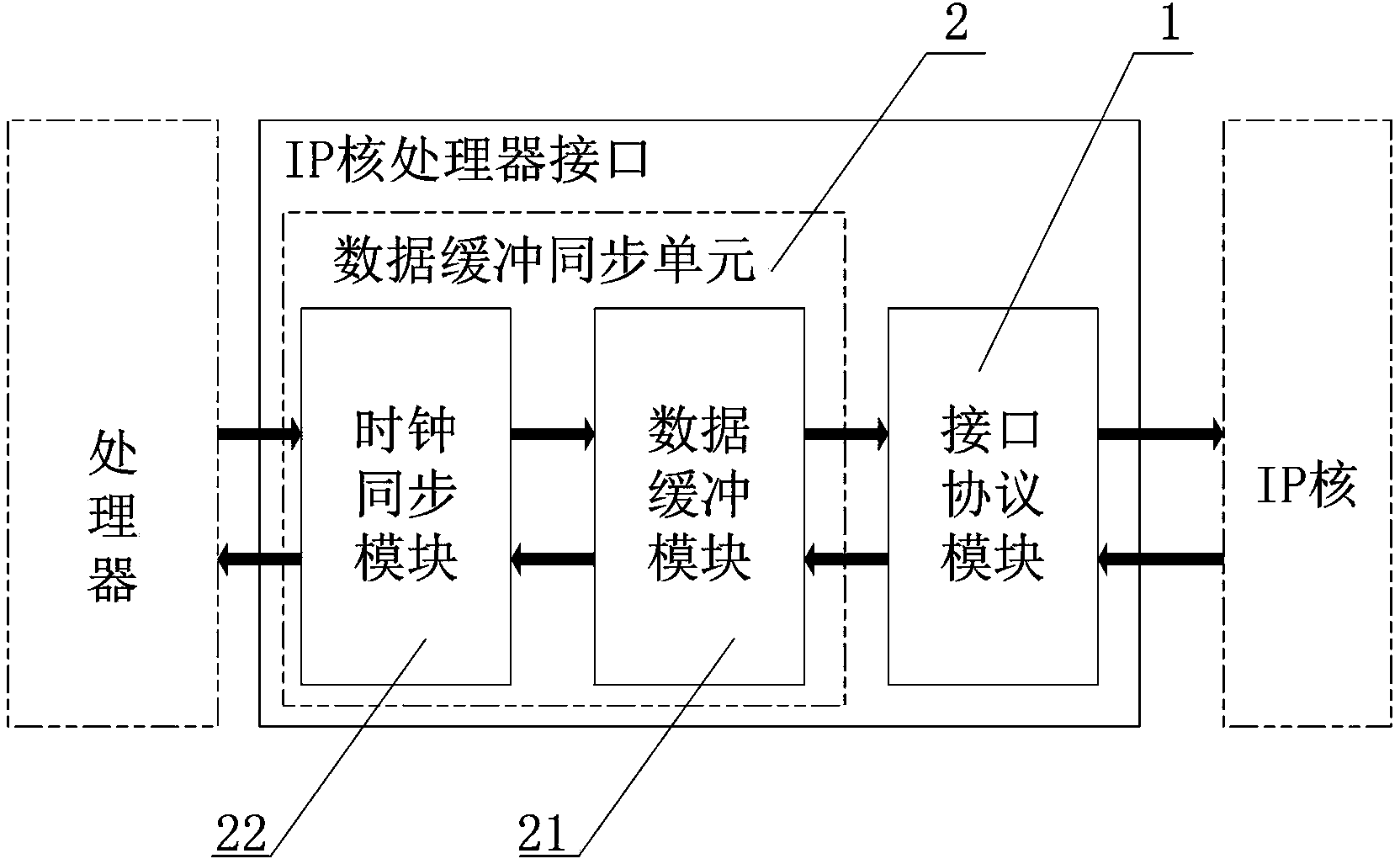

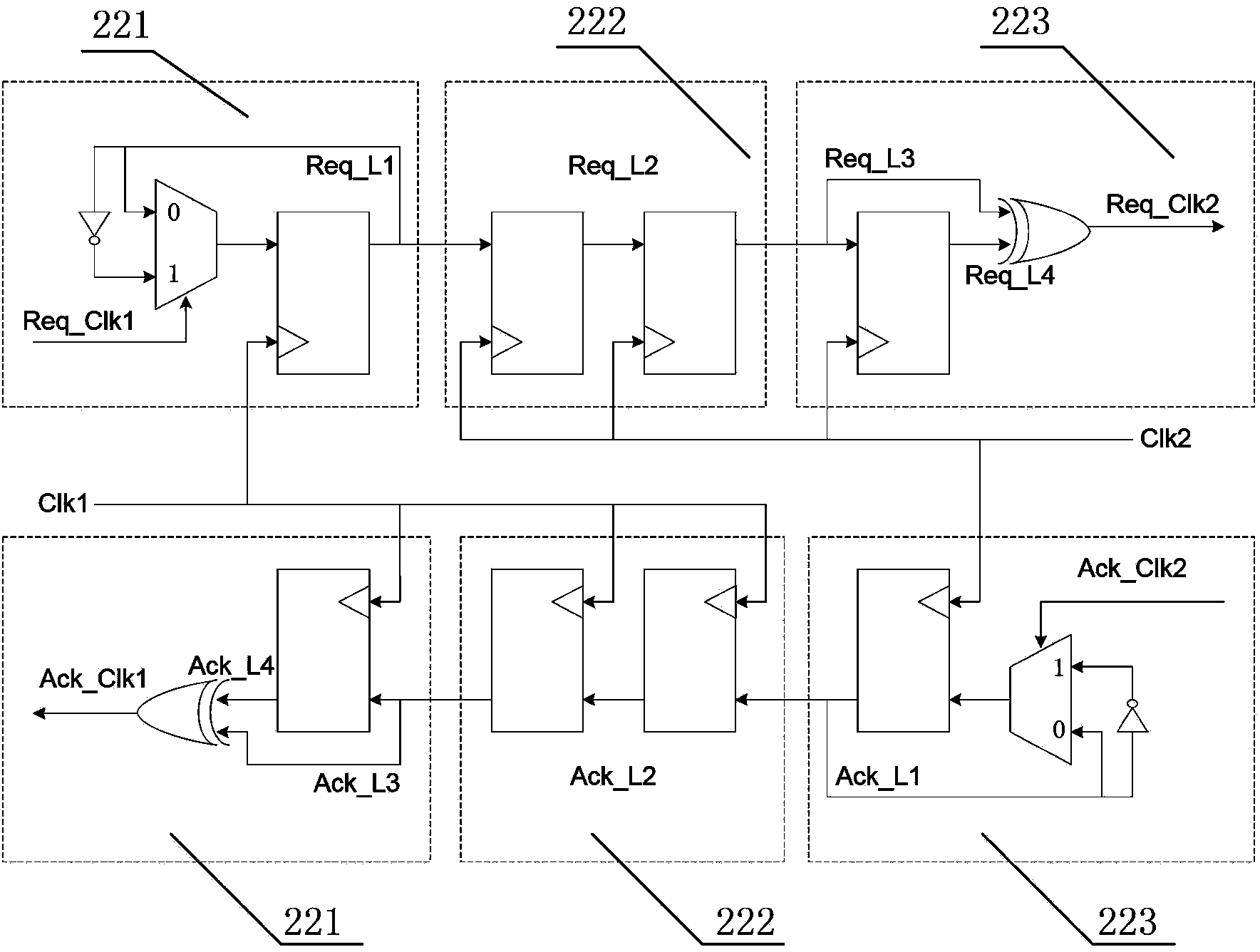

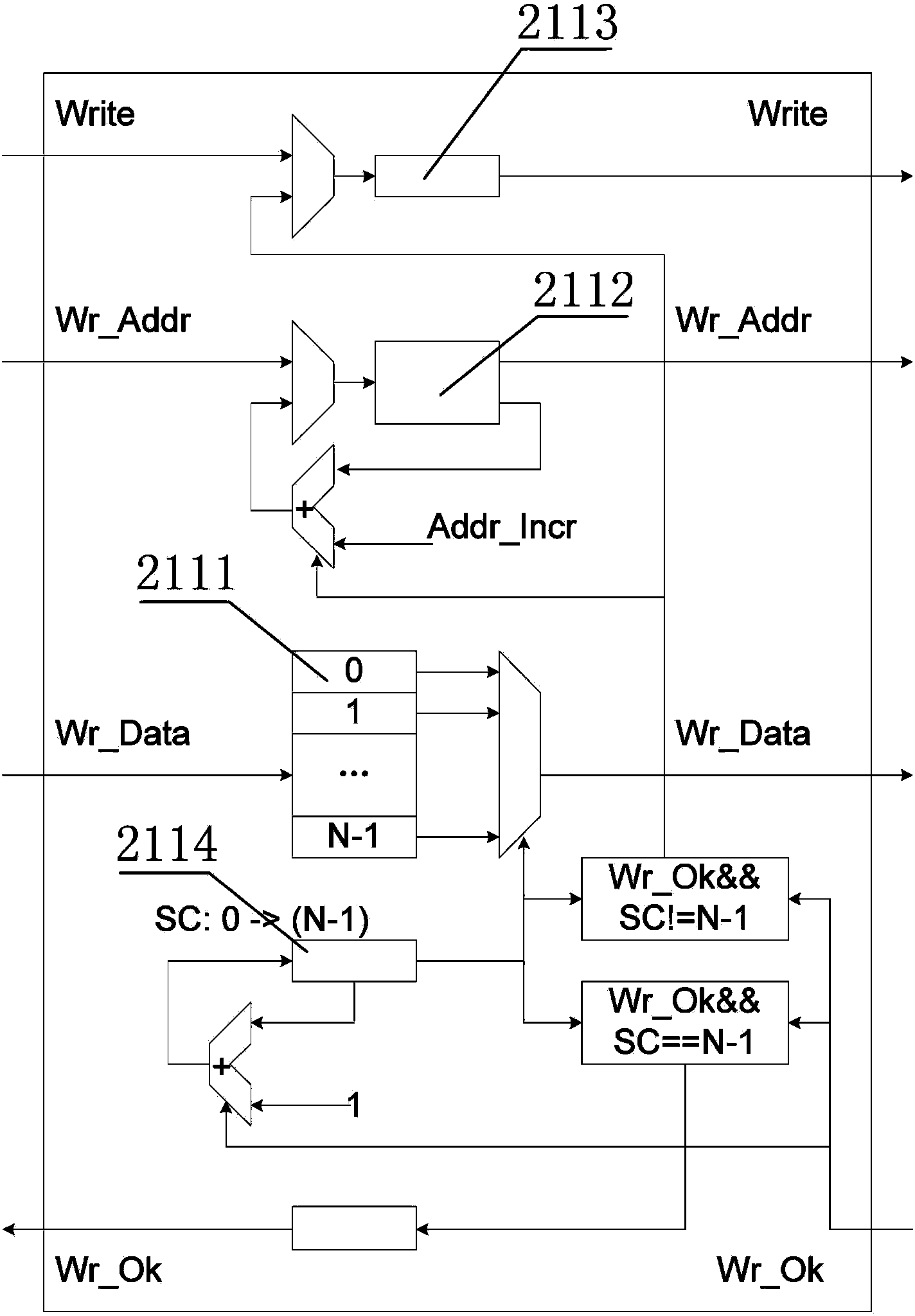

[0050] Such as figure 1 As shown, the embodiment of the present invention is used for the processor interface of IP core and comprises interconnected data buffer synchronization unit 2 and adopts the interface protocol module 1 of IP core complementary interface protocol, and interface protocol module 1 is connected with IP core, and interface protocol module 1 Connected to the processor through the data buffer synchronization unit 2, the data buffer synchronization unit 2 includes a data buffer module 21 for buffering data between IP cores and processors with different data processing widths and an IP core and processing for synchronizing different clock domains The clock synchronization module 22 of the data clock between the devices, and the data buffer module 21 is connected with the clock synchronization module 22.

[0051] In this embodiment, the interface protocol module 1 is automatically generated according to the interface description information, and the interface p...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More