Formation method of shallow trench isolation structure

An isolation structure and shallow trench technology, applied in electrical components, semiconductor/solid-state device manufacturing, circuits, etc., can solve problems such as short circuits and punch-throughs, avoid losses, reduce wet etching time, and increase wet etching rate. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

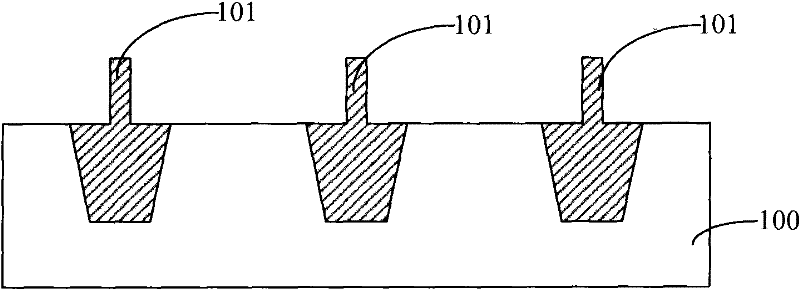

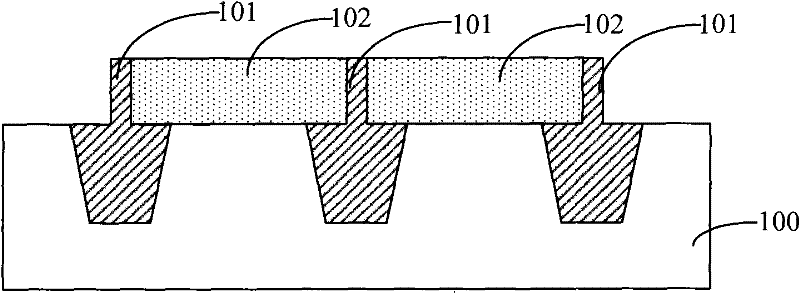

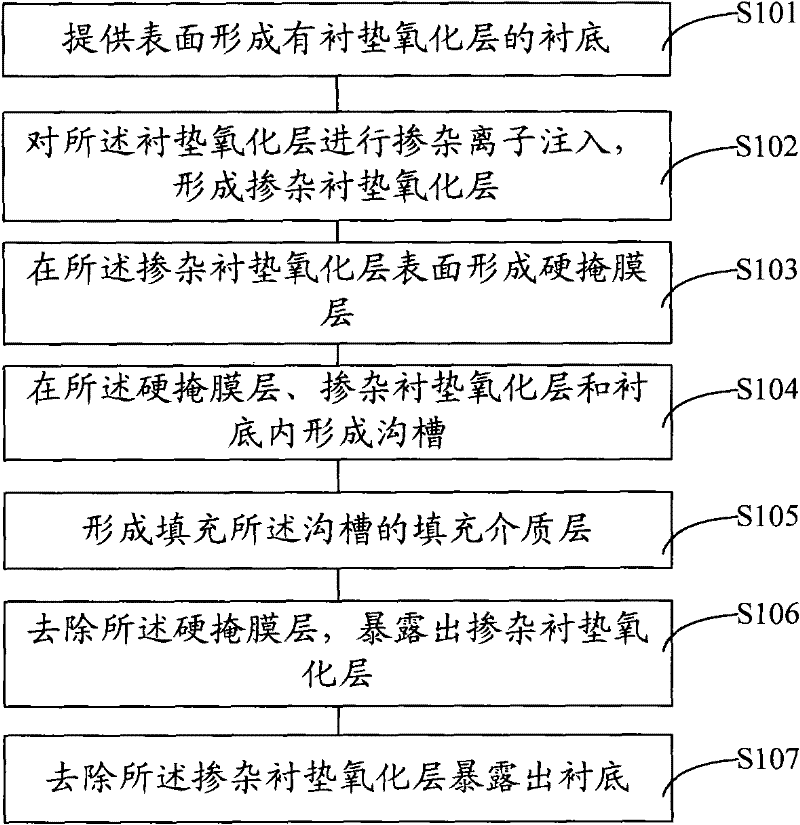

[0012] It can be seen from the background art that punch-through or short circuit usually occurs between the polysilicon gate structures formed on the surface of the substrate 100 . For this reason, the inventors of the present invention have found through research that the punch-through or short-circuit phenomenon is due to the fact that the shallow trench isolation structure 101 located between the polysilicon gate structures and higher than the surface of the substrate 100 is too narrow to effectively electrically isolate Adjacent polysilicon gate structures, so that the adjacent polysilicon gate structures have a punch-through or short circuit phenomenon.

[0013] After further research by the inventors, it was found that the reason why the shallow trench isolation structure above the substrate surface was too narrow was that the hard mask layer and the pad oxide layer were removed by a wet method, while the pad oxide layer and the shallow trench The material used for the ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More